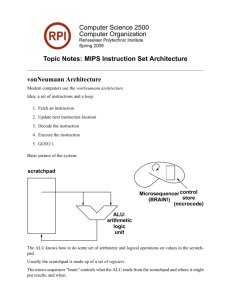

The MIPS Instruction-Set Architecture

advertisement

The MIPS Instruction-Set Architecture [H&P §2.12] The MIPS instruction set illustrates four underlying principles of hardware design: 1. 2. 3. 4. Simplicity favors regularity. Smaller is faster. Good design demands compromise. Make the common case fast. The MIPS instruction-set architecture has characteristics based on conclusions from previous lectures. • It is a load-store architecture that uses general-purpose registers. • It has only two addressing modes, displacement and immediate, but can synthesize other important modes from them. • It supports 8-, 16-, 32-, and 64-bit integers, and 32- and 64bit IEEE 754 floating-point numbers. • It has an orthogonal set of instructions to manipulate these data types. • It has separate comparison and branching instructions. (This is an example of making the common case fast.) MIPS has thirty-two 64-bit general-purpose registers, named R0, R1, … , R31. R0 always contains 0 (loading it with another value has no effect). It has 32 floating-point registers, which can hold either singleprecision (32-bit) or double-precision (64-bit) values. This is an example of smaller is faster—using a single register set would make register-address fields larger and make accesses take longer. © 2002 Edward F. Gehringer ECE 463/521 Lecture Notes, Fall 2002 Figures from CAQA used with permission of Morgan Kaufmann Publishers. © 2003 Elsevier Science (USA) 1 Addressing modes Displacement and immediate modes both have 16-bit fields. How can we synthesize other important addressing modes? › Register indirect: › Direct: › Scaled: › Memory indirect: Like the PowerPC, MIPS can select either Big Endian or Little Endian byte ordering. Memory is byte addressable with a 64-bit address. MIPS instruction formats Simplicity favors regularity … so all MIPS arithmetic instructions have exactly three operands. For example, DADD R3, R1, R2 Regs[R3] ← Regs[R1] + Regs[R2] DSUB R3, R1, R2 Regs[R3] ← Regs[R1] – Regs[R2] Good design demands compromise … so instructions are fixed length (32 bits). This requires different instruction formats. This table gives a summary of the three formats. Format 6 bits 5 bits 5 bits 5 bits 5 bits 6 bits R op rs rt rd shamt funct I op J op Lecture 13 rs rt address/immediate target address Advanced Microprocessor Design Comments Arithmetic Transfer, branch, immediate Jump 2 Let’s take a look at each of these formats in more detail. An R-type instruction has this format. 6 5 5 5 5 6 Opcode rs rt rd shamt funct ALU op Operand 1 Operand 2 Result Shift amt. add, sub, etc. This format is used for both arithmetic and boolean operations. In general, the shamt field is 0 for arithmetic operations, and the rs field is 0 for logical operations. An I-type instruction has this format. 6 5 5 16 Opcode rs rt Immediate Load/Store Source register Destination register Immediate Conditional branch Comparand Comparand 1 2 [rt ← rs op immediate] PC-relative offset [if rs rel rt then branch] A J-type instruction has this format. 6 26 Opcode Offset Jump [& link] Target address4..29 Jump register Register to jump to JR function code MIPS instructions Here are a few MIPS instructions. The text has another list, and a comprehensive list (for MIPS IV) can be found at techpubs.sgi.com/library/manuals/2000/ 007-2597-001/pdf/007-2597001.pdf © 2002 Edward F. Gehringer ECE 463/521 Lecture Notes, Fall 2002 Figures from CAQA used with permission of Morgan Kaufmann Publishers. © 2003 Elsevier Science (USA) 3 Arithmetic instructions Instruction Example Meaning Comments Add ADD R1,R2,R3 R1←R2+R3 Subtract SUB R1,R2,R3 R1←R2–R3 Add immediate ADDI R1,R2,10 R1←R2+10 Adds a constant Add unsigned ADDU R1,R2,R3 R1←R2+R3 No trap on o’flo. Add immed uns’d ADDIU R1,R2,10 R1←R2+10 Logical instructions Instruction Example Meaning Comments And AND R1,R2,R3 R1←R2&R3 Or OR And immediate ANDI Shift left logical SLL R1,R2,10 R1←R2<<10 Shift left by constant Shift right logical SRL R1,R2,10 R1←R2>>10 Shift right by constant R1,R2,R3 R1←R2|R3 R1,R2,10 R1←R2&10 and with a constant Load/store Instruction Load word Example LW Meaning Comments R1,10(R2) R1←Mem [R2+10] Memory to register R1,10(R2) Mem[R2+10] ←R1 Register to memory Load constant into Load upper LUI R1,10 R1←10×216 upper 16 bits of word immed. Store word SW Conditional branch Instruction Branch on equal Branch on not equal Example Meaning BEQ R1,R2,10 if (R1==R2) goto PC+4+10 BNE R1,R2,10 if (R1!=R2) goto PC+4+10 Set on less than SLT Lecture 13 Advanced Microprocessor Design R1,R2,R3 if (R2<R3) R1←1; else R1=0 4 16-bit signed offset is shifted left two places and added to the program counter. (The program counter is pointing to the next sequential instruction.) Unconditional jump Instruction Example Meaning Jump J 1000 goto 1000 Jump register JR R31 goto R31 Jump and link JAL 1000 Jump and link register JALR R1 Comments Jump to target address For switch or procedure return R31←PC+4; For procedure call goto 1000 R31←PC+4; For procedure call PC←R2 Floating-point Instruction Example Meaning Comments Add double ADD.D F1,F2,F3 F1←F2+F3 64-bit operation Subtract single SUB.S F1,F2,F3 F1←F2–F3 32-bit operation F1←F2×F3 Two 32-bit operations simultaneously Multiply paired MUL.PS single F1,F2,F3 Let’s take a look at how frequently these instructions are used. Here are frequencies for five SPECint2000 programs. © 2002 Edward F. Gehringer ECE 463/521 Lecture Notes, Fall 2002 Figures from CAQA used with permission of Morgan Kaufmann Publishers. © 2003 Elsevier Science (USA) 5 Below are frequencies for five SPECfp2000 programs. Compare these frequencies with the frequencies for integer programs. Why are there more loads than stores? What differences do you see in instruction frequencies? Lecture 13 Advanced Microprocessor Design 6 Sample MIPS program # # # # # sumit.asm Simple routine to sum N integers to demo a loop. Author: R.N. Ciminero Revision date: 10-06-93 Original def. See Patterson & Hennessy pg. A-46 for system services. .text .globl main main: li $v0,4 la $a0, msg1 syscall li $v0,5 syscall move $t0,$v0 # # # # # # li li # initialize counter (i) # initialize sum loop: addi add beq j $t1, 0 $t2, 0 load code for print_string address of string to print print string load code for read_int input N save $t1, $t1, 1 # i = i + 1 $t2, $t2, $t1 # sum = sum + i $t0, $t1, exit # if i = N, continue loop exit: li $v0, 4 la $a0, msg2 syscall # output msg2 li $v0,1 move $a0, $t2 syscall # output sum li $v0,4 la $a0, lf syscall # output lf li $v0,10 # exit syscall .data msg1: .asciiz "\nNumber of integers (N)? msg2: .asciiz "\nSum = " lf: .asciiz "\n" " Output Number of integers (N)? 5 Sum = 15 © 2002 Edward F. Gehringer ECE 463/521 Lecture Notes, Fall 2002 Figures from CAQA used with permission of Morgan Kaufmann Publishers. © 2003 Elsevier Science (USA) 7 Comments on the program In MIPS, registers have names as well as numbers. Some of the register names that are used in this program are— Register name Number $v0 2 Expression evaluation and function results $a0 4 Argument 1 $t0 8 Temporary (not preserved across call) $t1 9 Temporary (not preserved across call) $t2 10 Temporary (not preserved across call) Usage li $t1, 0 # initialize counter (i) Temporary register $t1 contains the count. li $t2, 0 # initialize sum Temporary register $t2 contains the sum. loop: addi $t1, $t1, 1 # i = i + 1 Increment the counter by one. add $t2, $t2, $t1 # sum = sum + i Add the counter to theum. beq $t0, $t1, exit # if i = N, continue If the counter equals the number of integers, then exit the loop. j loop Else perform the summation again. exit: li $v0, 4 # output msg2 Statement to execute upon leaving the loop. [All contents copyright © 1995 Ronald N. Ciminero. Used with permission.] Lecture 13 Advanced Microprocessor Design 8