MIPS Assembly Homework: C to MIPS Translation

advertisement

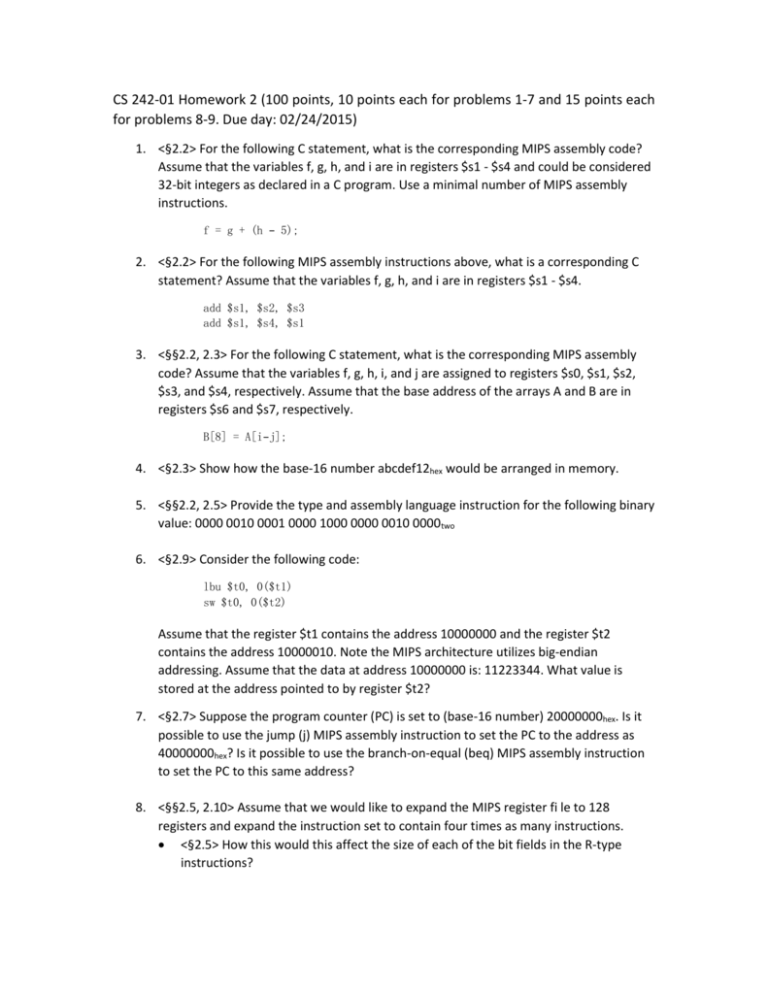

CS 242-01 Homework 2 (100 points, 10 points each for problems 1-7 and 15 points each

for problems 8-9. Due day: 02/24/2015)

1. <§2.2> For the following C statement, what is the corresponding MIPS assembly code?

Assume that the variables f, g, h, and i are in registers $s1 - $s4 and could be considered

32-bit integers as declared in a C program. Use a minimal number of MIPS assembly

instructions.

f = g + (h − 5);

2. <§2.2> For the following MIPS assembly instructions above, what is a corresponding C

statement? Assume that the variables f, g, h, and i are in registers $s1 - $s4.

add $s1, $s2, $s3

add $s1, $s4, $s1

3. <§§2.2, 2.3> For the following C statement, what is the corresponding MIPS assembly

code? Assume that the variables f, g, h, i, and j are assigned to registers $s0, $s1, $s2,

$s3, and $s4, respectively. Assume that the base address of the arrays A and B are in

registers $s6 and $s7, respectively.

B[8] = A[i−j];

4. <§2.3> Show how the base-16 number abcdef12hex would be arranged in memory.

5. <§§2.2, 2.5> Provide the type and assembly language instruction for the following binary

value: 0000 0010 0001 0000 1000 0000 0010 0000two

6. <§2.9> Consider the following code:

lbu $t0, 0($t1)

sw $t0, 0($t2)

Assume that the register $t1 contains the address 10000000 and the register $t2

contains the address 10000010. Note the MIPS architecture utilizes big-endian

addressing. Assume that the data at address 10000000 is: 11223344. What value is

stored at the address pointed to by register $t2?

7. <§2.7> Suppose the program counter (PC) is set to (base-16 number) 20000000hex. Is it

possible to use the jump (j) MIPS assembly instruction to set the PC to the address as

40000000hex? Is it possible to use the branch-on-equal (beq) MIPS assembly instruction

to set the PC to this same address?

8. <§§2.5, 2.10> Assume that we would like to expand the MIPS register fi le to 128

registers and expand the instruction set to contain four times as many instructions.

<§2.5> How this would this affect the size of each of the bit fields in the R-type

instructions?

<§2.5> How this would this affect the size of each of the bit fields in the I-type

instructions?

<§2.5> How could each of the two proposed changes decrease the size of an MIPS

assembly program? On the other hand, how could the proposed change increase

the size of an MIPS assembly program?

9. <§2.8> Implement the following C code in MIPS assembly. What is the total number of

MIPS instructions needed to execute the function? Assume n is in register $s0.

int f(int n){

if (n==0)

return 0;

else

return 1+f(n−1);

}