Xilinx Design Flow

advertisement

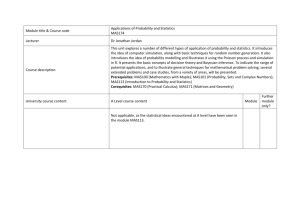

Xilinx Design Flow © Memec (MG 000-00) 04.01.04 The Integrated Software Environment Design Entry Advanced Design Techniques GNU Embedded Tools ¾Wind River Xilinx Edition ¾Embedded Development Kit ¾IMPACT ¾System ACE Configuration Manager ¾ HDL Edit and Entry ¾System Generator for DSP ¾CORE IP Generator ¾Architecture Wizards ¾ECS Schematic Editor ¾StateCAD State Diagram Editor ¾RTL Checker ¾ Verification Technologies ModelSim Xilinx Edition ¾Static Timing Analyzer ¾ChipScope Pro ¾XPower power estimation ¾Formal Verification support ¾3rd Party HDL simulation ¾ChipViewer ¾FPGA Editor with Probe ¾HDL Bencher testbench generator Synthesis Synplicity Synplify and Synplify Pro ¾Synplicity Amplify physical synthesis ¾MentorGraphics LeonardoSpectrum ¾Mentor Graphics Precision RTL physical synthesis ¾Synopsys FPGA Compiler II ¾Xilinx Synthesis Technology (XST) ¾ Implementation ¾ Floorplanner and PACE ¾Constraints Editor ¾Timing Driven Place & Route ¾Modular Design ¾Incremental Design ¾Timing Improvement Wizard ¾ Board Level Integration IBIS Models ¾STAMP Models ¾LMG Smart Models ¾HSPICE Models ¾ 3rd party partner tools One solution for all your logic design needs © Memec (MG 001-04) 02.27.04 Xilinx Design Flow Plan & Budget Create Code/ Schematic HDL RTL Simulation Implement Translate Functional Simulation Synthesize to create netlist Map Place & Route Attain Timing Closure Timing Simulation Create Bit File © Memec (MG 001-04) 02.27.04 Creating a Project Select File Æ New Project New Project Wizard guides you through the process Project name and location Target device Software flow Create or add source files © Memec (MG 001-04) 02.27.04 Creating and Adding Source Files To include an existing source file, double-click Add Existing Source To create a new source file, double-click Create New Source and choose the type of file HDL file IP Schematic State diagram Testbench Constraints file © Memec (MG 001-04) 02.27.04 Text Entry Color coding helps you understand and quickly enter the design Blue = Reserved words Pink = Signal type Green = Comments Black = User input © Memec (MG 001-04) 02.27.04 Language Templates Two methods to open templates: Language Icon Edit -> Language Templates Language Templates provide common templates for designs: Component instantiation Language templates Synthesis templates © Memec (MG 001-04) 02.27.04 Schematic Source File Files with .sch extension Selecting this source type will open the ECS (Engineering Capture System) schematic editor © Memec (MG 001-04) 02.27.04 Options and Symbols The Options tab selections change, depending on which function is selected For example, if you are adding a net name, the net name options would be shown Components are divided into categories Exact symbols are located in the Symbol box Symbol Name Filter for easier search Orientation Rotate 0, 90,180, 270 Mirror and rotate 0, 90, 180, 270 © Memec (MG 001-04) 02.27.04 State Diagram Source Files with .dia extension Selecting this surce type will invoke StateCAD © Memec (MG 001-04) 02.27.04 Implementation Status ISE will run all of the necessary steps to implement the design Synthesize HDL code Translate Map Place & Route Progress and status are indicated by icons Green check mark ( ) indicates that the process was completed successfully Yellow exclamation point ( ! ) indicates warnings Yellow question mark ( ? ) indicates a file that is out of date Red “X” indicates errors © Memec (MG 001-04) 02.27.04 Simulating a Design To simulate a design: In the Sources in Project window, select a testbench file In the Processes for Source window, expand ModelSim Simulator Double-click Simulate Behavioral Model or Simulate Post-Place & Route Model • Can also simulate after Translate or after Map © Memec (MG 001-04) 02.27.04 Sub-Processes Each process can be expanded to view sub-tools and sub-processes Translate • • Floorplan Assign Package Pins Map • Analyze timing Place & Route • • • • • Analyze timing Floorplan FPGA Editor Analyze power Create simulation model © Memec (MG 001-04) 02.27.04 Program the FPGA There are two ways to program an FPGA Through a PROM device • You will need to generate a file that the PROM programmer will understand Directly from the computer • Use the iMPACT configuration tool © Memec (MG 001-04) 02.27.04 3rd Party Simulation Integration ISE 6.1i is designed and tested to run with the leading HDL simulators in the industry Cadence NC-Sim Model Technology ModelSim Synopsys VCS-MX and Scirocco All Xilinx libraries and netlists conform to IEEE VHDL-93, VITAL-2000 and Verilog2001 standards Other simulators are available to perform Xilinx CPLD and FPGA verification © Memec (MG 001-04) 02.27.04 3rd Party Synthesis Integration Synplify/Pro 7.3.1 Ability to use the parity bit in Virtex™-II, Virtex-II Pro™, and Spartan™-3 devices to optimize Block RAM implementations Improved area optimization for Virtex-II, Virtex-II Pro, and Spartan-3 devices Precision 2003b Support Virtex-E/-II/-II Pro, Spartan-II/-IIE/-3 Advanced design analysis LeonardoSpectrum 2003b Support Spartan-3 family FCII v3.8 Support for Spartan-3 devices Support for all Virtex-II Pro devices © Memec (MG 001-04) 02.27.04 Simulation Tool © Memec (MG 000-00) 04.01.04 Simulation in the FPGA Environment RTL Simulation Design Entry Highest performance Many spins HDL RTL • highest throughput Functional Simulation • Does function match RTL Golden model Gate Level Simulation • • • Highest impact on simulation run time Full timing Does function match RTL Golden model Source Templates and Wizards, HDS, IPX, Xilinx LogiCORE, CORE Generator Leonardo Spectrum Synthesis HDL Gate Functional Functional Simulation Place & Route Xilinx ISE HDL Gate Timing ModelSim RTL Simulation HDL Gate Timing Gate Level Simulation ModelSim VITAL or Verilog Simulation Library ModelSim © Memec (MG 001-04) 02.27.04 HDL Bencher Creates timing VHDL and self-checking No knowledge HDL or constrained Verilog testbenches of scripting required © Memec (MG 001-04) 02.27.04 Create a New Source © Memec (MG 001-04) 02.27.04 Create a New Source © Memec (MG 001-04) 02.27.04 HDL Bencher Unit under test is analyzed, when selected Port problems Syntax violations Inconsistencies Design timing selected Clocked or combinatorial? © Memec (MG 001-04) 02.27.04 Create Waveforms Data values 1, 0 ,X ,Z, U Assignments Double-click bit signal to toggle value Pattern wizard assigns a range of cell values WaveTable assign signals like a spreadsheet By default, decimal values are shown in the WaveTable Waveform values are checked as they are entered Validation check for non-binary inputs only (for example, hex, or decimal) © Memec (MG 001-04) 02.27.04 Toggling Toggling bit values is the easiest way to assign bit signals Simply click directly on the signal’s waveform at the time where changes should take place Click directly on these boxes, at the time where signals should toggle © Memec (MG 001-04) 02.27.04 Pattern Wizard Aids complex waveform input To access, click a signal at the time it should be changed to access value cell editor Click in this area Click here for Pattern Wizard Note: light blue background = input assignment, light yellow background = output assignment © Memec (MG 001-04) 02.27.04 Pattern Wizard Available patterns Pattern description Changes depending on the pattern selected Count unit in clock cycles © Memec (MG 001-04) 02.27.04 Testbench Waveform file extensions are TBW Waveform file can be seen in the Sources in Project window of the Project Navigator To view testbench: In Sources in Project Window, select the TBW file Then in the Processes for Current Source window, click View Behavioral Testbench © Memec (MG 001-04) 02.27.04 Modelsim In ISE (FPGA) •RTL Simulation •Functional Simulation •Does function match RTL Golden model •Gate Level Simulation ( only gate delay) •Gate Level Simulation ( gate delay + wire delay) © Memec (MG 001-04) 02.27.04 Modelsim In ISE TestBench type code Simulation process © Memec (MG 001-04) 02.27.04 Top Answer Records Hits #15338: How do I compile simulation Models #16233: BlockRAM Collision Errors #10629: What are $setup and $hold violations #15501: How do I install SmartModels? #6537: How do I use the glbl.v file for Verilog? #15969: Using the ASYNC_REG constraint © Memec (MG 001-04) 02.27.04 CORE Generator © Memec (MG 000-00) 04.01.04 What are Cores? A core is a ready-made function that you can instantiate into your design as a “black box” Cores can range in complexity Simple arithmetic operators, such as adders, accumulators, and multipliers System-level building blocks, including filters, transforms, and memories Specialized functions, such as bus interfaces, controllers, and microprocessors Some cores can be customized © Memec (MG 001-04) 02.27.04 Sample Functions LogiCORE solutions DSP functions • Time skew buffers, FIR filters, correlators Math functions • Accumulators, adders, multipliers, integrators, square root Memories • Pipelined delay elements, single and dual-port RAM • Synchronous FIFOs PCI master and slave interfaces, PCI bridge AllianceCORE solutions Peripherals • DMA controllers • Programmable interrupt controllers • UARTs Communications and networking • ATM • Reed-Solomon encoders / decoders • T1 framers Standard bus interfaces • PCMCIA, USB © Memec (MG 001-04) 02.27.04 Invoking the CORE Generator System From the Project Navigator, select Project → New Source Select IP (CoreGen & Architecture Wizard) and enter a filename Click Next, then select the type of core © Memec (MG 001-04) 02.27.04 Xilinx CORE Generator System GUI Cores can be organized by function, vendor, or device family Core type, version, device support, vendor, and status © Memec (MG 001-04) 02.27.04 Core Customize Window Core Overview tab provides version information and a brief functional description Parameters tab allows you to customize the core Web Links tab provides direct access to related Web pages Contact tab provides information about the vendor Data sheet access © Memec (MG 001-04) 02.27.04 CORE Data Sheets Performance expectations (not shown) Features Functionality Pinout Resource utilization © Memec (MG 001-04) 02.27.04 Architecture Wizard Architecture Wizard contains two wizards: Clocking Wizard RocketIO Wizard Double-click Create New Source Select IP (CoreGen & Architecture Wizard), then click Next • • Expand Clocking and select desired function Expand I/O Interfaces and select RocketIO* © Memec (MG 001-04) 02.27.04 DCM Wizard --General Setup Options Select which pins are required Define attributes: Input Clock Frequency CLKIN Source Divide By Value Feedback Source Feedback Value Duty Cycle Correction Phase Shift (DPS) © Memec (MG 001-04) 02.27.04 DCM Wizard– DFS setting Frequency synthesizer Select M / D value OR Specify frequency “Calculate” button for jitter Period jitter is evaluated for CLKFX output Note: This dialog appears only if the CLKFX output was selected © Memec (MG 001-04) 02.27.04 Where Can I Learn More? Xilinx IP Center http://www.xilinx.com/ipcenter Software updates Download new cores as they are released Tech Tips on http://support.xilinx.com Software manuals: CORE Generator Guide DCM constraints: Online Software Manuals → Constraints Guide DCM architecture: Virtex-II, Virtex-II Pro, Spartan-3 Data Sheets → Detailed Description Virtex-II, Virtex-II Pro, Spartan-3 User Guides → Design Considerations → DCM DCM timing parameters: Virtex-II, Virtex-II Pro, Spartan-3 Data Sheets → Electrical Characteristics Virtex-II, Virtex-II Pro, Spartan-3 Interactive Data Sheets → http://support.xilinx.com/applications/web_ds/index_top.htm © Memec (MG 001-04) 02.27.04