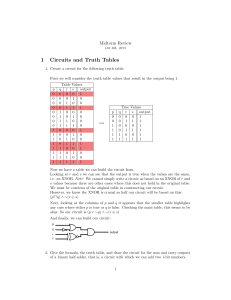

Device reliability challenges for modern semiconductor circuit design

advertisement