MOS and BJT device characteristics, large-signal and small

advertisement

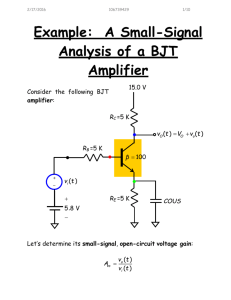

ECEN 4827/5827 Supplementary Notes 1. Review: Active Devices in Microelectronic Circuits c 2005 Dragan Maksimović Department of Electrical and Computer Engineering University of Colorado, Boulder The purpose of this part of the notes is to briefly review some of the prerequisite course materials related to characteristics of active device in microelectronic circuits. We summarize dc, large-signal and small-signal (incremental) models of two major types of active devices used in analog, digital and mixed-mode integrated circuits: metal-oxide-semiconductor field-effect transistors (MOSFET), and bipolar junction transistors (BJT). Several examples are used to illustrate approaches to analysis of DC, and AC (small-signal) properties of electronic circuits at the device level. 1 D NMOS D B G S S (b) S PMOS S B G G D D D + v DS + v GS - S (c) S v + + SG v G SD iD D - G G (a) iD G (d) G Figure 1: Symbols currently in use for “enhancement-mode” MOS transistors: (a) symbols of MOS transistor as 4-terminal devices; (b) symbols of MOS transistors with the substrate (B)shorted to the source (S) terminal; (c) symbols of MOS transistors with implied (default) connections of the substrate (B) terminal; (d) symbols commonly used in digital circuits where source (S) and drain (D) terminals are not specified. 1 Metal-oxide-semiconductor field-effect transistor (MOSFET) Prior to reading this section, it is useful to review suggested reference textbooks on CMOS technology, and physics of n-channle (NMOS) and p-channel (PMOS) devices. Various symbols for “enhancement-mode” NMOS and PMOS devices are shown in Fig. 1. On an integrated circuit, MOS transistor is a 4-terminal device, as indicated by the symbol in Fig. 1(a). In a standard, p-substrate CMOS technology, an n-channel (NMOS) device is built on a p-type substrate (B terminal). The n-type source (S) and drain (D) regions are the device “output” terminals. The gate (G) is isolated from the substrate by a thin layer of oxide. A p-channel (PMOS) device is built with p-type source and drain regions in an“n-well,” which serves as an n-type substrate (B), Depending on the voltage applied between the gate (G) and source (S) terminals, a conducting channel can be established between the drain (D) and the source (S). If the substrate terminal (B) is shorted to the source (S) terminal, the MOS transistor can be considered a 3-terminal device, and the symbols in Fig. 1(b) are in use. If the substrate terminal (B) is connected to a default voltage rail (negative supply rail for p-substrate, positive supply rail for n-wells), the MOS transistor can be considered a 3-terminal device, and the symbols in Fig. 1(c) are in use. Finally, in digital CMOS circuits, where the distinction between the source (S) and drain (D) terminals is not important, the symbols in Fig. 1(d) are commonly used. 1.1 Dc characteristics and operating modes (i.e. operating regions) Typical DC output-plane iD (vDS ) characteristics for an NMOS device are shown in Fig. 2. These characteristics are obtained by PSpice simulation of the circuit shown in Fig. 2. 2 MOS output characteristics (2N6782, mos.cir) 15mA VGS=5V i_D VGS=4.5V 10mA 2 3 VGS=4V 5mA 1 VGS=3.5V iD VGS=3V 2 + VGS < Vt + - v GS v DS 0 - -0mA 1 v_DS Vt=2V K=1.5mA/V^2 2N6782 -5mA -1.0V 0.0V id(m1) 1.0V 2.0V 3.0V 4.0V 5.0V VDS Figure 2: Dc characteristics of an n-channel MOS transistor (2N6782), as obtained by PSpice 2 between saturation (region 2) and triode (region simulation (mos.cir). Boundary iD = KvDS 3) modes is also shown. Glossary • Threshold voltage: Vt For an NMOS device, gate-to-substrate voltage greater than the threshold Vtn = |Vtp | = Vt causes formation of an inversion layer of free electrons (conducting channel) in the p-type substrate. The threshold voltage Vt is positive for “enhancement-mode” devices in a standard CMOS technology, typically between 0.5V and 1.5V. If the gate-to-substrate voltage at a certain point between source and drain is greater than the threshold voltage, we say that the channel is “on” at that point. Otherwise, the channel is “off”. Note that for NMOS devices the threshold voltage Vtn is positive, while for PMOS device the threshold voltage Vtp is negative. A “depletion-mode” NMOS device has a built-in conducting n-type layer in the psubstrate between the drain and the source, so that it takes a negative gate-to-substrate voltage to turn the channel “off”. For a depletion-mode n-channel MOSFET, Vt is negative, but all other characteristics are the same as for the enhancement-mode devices. • Conductance parameter: K The conductance parameter K is proportional to the channel width W , inversely proportional to the channel length L, and proportional to the gate-to-channel capacitance per unit area Cox , W µCox , (1) K= L 2 where µ is the carrier mobility (electron mobility µn for n-channel devices, hole mobility 3 v GD vGD - + NMOS + v GS - + v SG PMOS v DG + |Vt| 3 triode Vt Vt vDG 3 triode |Vt| vGS vSG 1 2 1 2 cutoff saturation cutoff saturation Figure 3: Operating modes of an NMOS and a PMOS transistor. µp for p-channel devices). Summary of dc characteristics • For vDS > 0 (NMOS devices), or vSD > 0 (PMOS devices), the MOSFET can operate in one of the three main operating modes: cutoff, saturation or triode, depending the whether the channel is on or off on the source (S) and the drain (D) ends. Fig. 3 shows the operating modes in the |vGD | vs. |vGS | plane for NMOS and PMOS devices. The summary here is for an NMOS device with Vtn = Vt > 0. 1. cutoff (region 1 in Fig. 2): vGS < Vt , vGD < Vt , the channel is “off” at both the source (S) and drain (D) ends. Consequently, iD = 0 and the device is cut off. 2. saturation/active (region 2 in Fig. 2): vGS > Vt , vGD < Vt , the channel is “on” at the source end, “off” at the drain end. The drain current is nearly independent of the drain-to-source voltage. This operating mode is similar to the active mode for the bipolar transistors. In the saturation/active mode, the steady-state characteristics of an NMOS transistor are described by: iD = K(vGS − Vt )2 (1 + vDS /VA ) ≈ K(vGS − Vt )2 (2) The parameter VA is used to model the non-zero slope of the dc characteristics in the saturation region. In many cases, we can assume that VA → ∞, i.e., that the drain current iD in the saturation mode is independent of the voltage vDS . In saturation, if vGS > Vt , the drain current has quadratic dependence on the gateto-source voltage vGS , as shown in Fig. 4. Because the drain (output) current can be controlled by the gate-to-source (input) voltage the MOS transistor can be used to build various signal-amplification circuits. 4 MOS i_D(v_GS) and gm (2N6782, mos-gm.cir) 15mA 10mA 5mA ID Q VGS 0A 0V id(m1) 1.0V 2.0V 3.0V 4.0V 5.0V VGS Figure 4: Input-to-output characteristic iD (vGS ) for the NMOS transistor 2N6782 operating in saturation, as obtained by PSpice simulation (mos-gm.cir). The box around the DC operating point Q (VGS , ID ) is blown up in Fig. 5. 3. triode (region 3 in Fig. 2): vGS > Vt , vGD > Vt , the channel is “on” at both the source end and the drain end. In the triode mode, iD depends strongly on both vGS and vDS . The steady-state characteristics are given by: 2 . iD = K 2(vGS − Vt )vDS − vDS (3) If vDS is much smaller than vGS , we have that vGD ≈ vGS so that the channel is equally “on” at both the source and the drain ends. As shown in Fig. 2, the iD (vDS ) characteristics close to the origin are close to straight lines. Between the drain and the source, the device behaves as a linear resistor whose resistance can be changed by the voltage applied to the gate. • For an enhancement mode PMOS, Vt < 0. The discussion above for an NMOS transistor applies to PMOS transistors if vGS is replaced by vSG , vGD is replaced with vDG , vDS is replaced by vSD and Vt is replaced by Vt = |Vtp |. For example, a PMOS transistor operates in the triode mode if vSG > |Vtp | and vDG > |Vtp |. In the triode mode, the drain current iD , with the polarity shown in Fig. 1(c), is given by: 2 iD = K 2(vSG − |Vtp |)vSD − vSD . (4) • The DC gate current is very close to zero, and can be neglected for all operating modes because the gate is electrically isolated from the channel by a thin layer of silicon oxide. • If vDS < 0 (NMOS devices), or vSD < 0 (PMOS devices) in a three-terminal MOSFET with the substrate shorted to the source, the substrate-to-drain junction becomes forward 5 biased as soon as |vDS | exceeds several tens of a volt. The device characteristic is very similar to the characteristic of a PN diode, as shown in the part of the characteristics in Fig. 2 for vDS < 0. • If the drain-to-source voltage exceeds a breakdown voltage VDSS , the drain current increases quickly with vDS . The excess current or the excess voltage may cause the device to fail. Circuits are normally designed so that the device never enters the breakdown region. 1.2 Small-signal (incremental) model at low frequencies MOS transistor, as most other semiconductor devices, has a number of operating modes described by nonlinear equations. A common approach to hand analysis of signal processing circuits is to find the DC operating point using device large-signal characteristics, and then linearize the characteristics around the DC bias operating point in order to examine what happens with signals that vary around the DC bias point. Mathematically, linearization of the device characteristics amounts to taking a Taylor expansion of the device nonlinear characteristic at a DC bias operating point and retaining only the first term in the expansion. For example, Fig. 4 shows the nonlinear iD (vGS ) characteristic of an NMOS transistor operating in saturation. Suppose that DC bias voltages and currents at the DC bias operating point Q are VGS , ID and VDS . Assume that the total voltage vGS has the dc component VGS and a signal component vgs = ∆VGS , vGS = VGS + vgs . (5) As a result, the total drain current iD can also be written as: iD = ID + id , (6) where ID is the DC bias drain current, and id is the signal component of the drain current. The relation between the signal components id and vgs is approximately linear if the amplitudes of id and vgs are relatively small, which is why the analysis based on linearization of device characteristics around a DC operating point is called the small-signal analysis. In general, to find signal components of all voltages and current in a given circuit, we use a small-signal model circuit obtained by removing the DC bias and replacing all devices with their linearized (incremental) small-signal models. In this section, we describe derivation of the small-signal model for a MOS transistor operating in the saturation mode. The same procedure can be followed to find the small-signal models in other operating modes, or for other devices. Applications of small-signal device models are discussed further in Section 4. If the MOS transistor operates in saturation at a DC bias operating point (VDS , ID ), the small-signal (incremental) model of Fig. 6 is obtained, where the parameters are obtained by taking partial derivatives of Eq. 2 and evaluating the partial derivatives at the DC bias operating point: ∂iD = 2K(VGS − Vt ) = 2 KID , (7) gm = ∂vGS 6 MOS i_D(v_GS) and gm (2N6782, mos-gm.cir) 5.0mA non-linear device characteristic 4.0mA ID DC operating point linearized characteristic Q 3.0mA gm = slope 2.0mA VGS 3.2V 3.4V 3.6V 3.8V 4.0V id(m1) VGS Figure 5: Linearization of the MOS iD (vGS ) characteristic to obtain the transconductance gm . G D + v gs S g m v gs rds - S Figure 6: The small-signal model of the MOS transistor operated in the saturation region. The model is exactly the same for both NMOS and PMOS devices. The parameter gm is called the transconductance and is equal to the slope of the iD (vGS ) characteristic at the DC bias point Q, as shown in Fig. 5, which is a blow up of Fig. 4 around the point Q. Similarly, the incremental output resistance is obtained as: rds = ro = 1 = gds ∂iD ∂vDS −1 = VA . ID (8) Note that two symbols, rds or ro are used interchangeably to represent the device incremental output resistance. Several general comments about the device small-signal models can be made here: • Small-signal models are linear, which allows all tools of linear system analysis to be applied in order to examine and design signal processing electronic circuits. Circuit characteristics such as “gain”, “output resistance,” etc. can be obtained using the smallsignal analysis. 7 • Parameter(s) in the small-signal models depend on the location of the DC operating point, i.e. on the DC bias. For example, see how the MOS transconductance or the MOS incremental output resistance depend on the DC bias current ID in Eqs. 7 and 8. • To obtain the small-signal model of a circuit, one first needs to solve for the circuit DC voltages and currents in order to obtain correct parameter values in the device smallsignal models. Then, each device in the circuit is simply replaced by its small-signal model. The dc voltage sources are short-circuited, while the dc current sources are opencircuited, because the variations (signal components) of dc voltages are equal to zero. Signal sources remain in the small-signal model unaltered, as long as the assumptions of the small-signal modeling remain valid. • Small-signal modeling involves linearization, i.e. neglecting all higher-order terms in the Taylor expansion of the actual nonlinear characteristics of the device. Therefore, all results obtained from a small-signal circuit model are approximate. The small-signal model is exact only for infinitely small voltage/current variations around the DC operating point. • How small should the signals around the DC operating point be so that the results obtain from the small-signal model are sufficiently accurate ? The answer depends on what you mean by “sufficiently accurate”. In the design process, acceptable errors are usually much larger than what one might expect. The device parameters, to start with, are known only within some tolerances. In practice, small-signal models are commonly applied even if variations around the DC operating point are comparable to DC values at the DC operating point, provided that the device does not leave the operating mode where the model is derived. For example, the small-signal MOSFET model cannot be applied if the vGS voltage variation takes the device from saturation to cutoff or triode, because the device characteristics change dramatically from one mode to another. As long as the MOSFET stays in the saturation mode, the results obtained from the small-signal model derived for the saturation mode are meaningful. Once a hand design is completed based on approximate models, tools such as computer simulation and prototyping are available for final performance verification. 2 Bipolar junction transistor (BJT) Before reading this section, it is a good idea to review the bipolar junction transistor IC technology and physics of BJT’s from any of the suggested reference textbooks. 2.1 Dc characteristics and operating modes/regions The BJT symbols for the npn and the pnp devices are shown in Fig. 7. Typical dc characteristics for the npn device are shown in Fig. 8. The characteristics are shown in the output plane, IC vs. VCE , for a range of base currents IB . Glossary • forward current gain: β = iC /iB 8 iC iB C E v + + EB v EC i B B C iC + B v CE + v BE - E NPN PNP Figure 7: Symbols for the NPN and PNP bipolar junction transistors. BJT output characteristics (2N3904, bjt.cir) 10mA IC IB=50uA 8mA IB=40uA 6mA IB=30uA 3 4mA 2 IB=20uA iC 2mA IB=10uA + + iB v BE - - v CE IB=0 1 0mA VCE VCES -1.0V 0V 1.0V 2.0V 3.0V 4.0V 5.0V ic(q1) vce Figure 8: Dc characteristics of an npn bipolar transistor (2N3904), as obtained by PSpice simulation (bjt.cir). 9 For integrated npn transistors at room temperature, in a standard bipolar technology, the current gain β in the active mode is typically between 100 and 300. The range of dc collector currents where the current gain has the highest value is between about 10µA and 1mA for a device with 5µm2 emitter area. A larger device can be designed to maintain the high current gain at higher collector currents. The current gain increases with temperature. • (common base) current gain: α = iC /iE , Since α = β β+1 , and β 1, α ≈ 1 in the active mode. • saturation voltage: VCES When the BJT operates in saturation (region 3 in Fig. 8), the dc characteristics are steep, and the voltage between the collector C and the emitter E is nearly constant. In a simplified DC model for the saturation mode, vCE ≈ VCES ≈ 0.2V is assumed constant. • Early voltage: VA This is the parameter that quantifies the finite slope of the transistor characteristics in the active mode (region 2 in Fig. 8). VA is 100 − 300V for npn devices in a standard bipolar process. • Breakdown voltage: BVCEO Collector-to-emitter voltage equal to or higher than BVCEO causes breakdown of the device and results in a steep increase in the collector current (not shown in Fig. 8). The breakdown voltage is 50V for a standard bipolar process. There is a variety of bipolar processes with different breakdown voltages. Summary of BJT dc characteristics For the purpose of hand analysis, it is appropriate to identify the distinct operating modes and the corresponding simplified models of bipolar transistors. • For vCE > 0 (for npn), (vEC > 0 (for pnp)), the bipolar transistor can operate in one of the three main operating modes, as shown in Figs. 8 and 9: 1. cutoff (region 1 in Fig. 8): both the BE junction and the BC junction are reversebiased (off); 2. active region (region 2 in Fig. 8): the BE junction is forward-biased, and the BC junction is reverse-biased. If a BJT operates in the active mode, its characteristics are described by: iC = ICO (evBE /VT − 1) 1 + iC = βiB 1 + 10 vCE VA vCE VA , (9) . (10) v BC vBC - + + v BE - NPN v CB + 3 saturation vCB + v EB 3 PNP saturation vBE vEB 1 2 1 2 cutoff active cutoff active Figure 9: Operating modes of an NPN and a PNP bipolar transistor. The characteristics in the active mode can be approximated by: iC = ICO evBE /VT , (11) iC = βiB . (12) Since the BE junction is forward biased in the active mode, the base-to-emitter voltage can be found using one of the following two approximations: (a) (accurate, but nonlinear:) vBE ≈ VT ln(iC /ICO ), or (b) (simple:) vBE ≈ VBE = 0.7V. 3. saturation (region 3 in Fig. 8): both the BE junction and the BC junction are forward-biased. If a BJT operates in saturation, VCE ≈ VCES , (13) iC < βiB . (14) • In the summary of BJT dc characteristics, everything holds for pnp transistors, except that reference polarities of the device voltages and currents are reversed, as indicated in Figs. 7 and 9 2.2 Small-signal (incremental) model at low frequencies If the BJT operates in the active mode, at a DC operating point (VCE , IC ), the small-signal (incremental) model is shown in Fig. 10. The parameters in the model depend on the DC bias operating point as follows: gm = ∂iC IC = , ∂vBE VT 11 (15) B v be E C + g m v be rpi - rce E Figure 10: Small-signal model of the BJT operating in the active mode. rπ = 1 ∂vBE ∂vBE ∂iC β = = = , gbe ∂iB ∂iC ∂iB gm (16) 1 ∂vCE VA = = . gce ∂iC IC (17) rce = The partial derivatives are evaluated at the dc operating point (VCE , IC ). 3 Operating modes: the key to solving microelectronic circuits at DC An essential component of electronic circuit design is to ensure that all devices operate in the operating modes best suited for the application. For example, transistors in amplifier stages are usually biased to operate in the active mode (BJTs) and saturation (MOSFETs). Devices in logic gates are usually forced to operate in either cut-off (fully off) region or fully on (saturation for BJTs, triode for FETs). Because the device characteristics are so much different depending on the operating mode, the first step in understanding any electronic circuit at the device level is to determine the device operating modes and the corresponding DC bias solution. A summary of large-signal DC characteristics can be found in Section 1.1 for MOSFETs, and Section 2.1 for bipolar transistors. Finding correct operating modes is discussed in this section with reference to several examples of circuits with bipolar transistors. These examples are taken from actual circuit diagrams of more complicated integrated circuits. In the examples of Fig. 11, the objective is to determine the operating modes of all transistors and to find the DC bias solution. We assume that all devices have identical characteristics, that VCC >> |VBE |, |VBE | > |VCES |, and β >> 1. The solutions are as follows: a) The BE junction is forward biased from +VCC through R. Therefore, VB = VBE and IB = (VCC − VBE )/R. The device Q is either in the active mode or in saturation. Assume that the device is in saturation. Then, VC = VCES , but this is impossible because VC = VCC . Therefore, Q is in the active mode and IC = βIB . b) The EB junction is shorted by the resistor R, and therefore reverse biased. IB = 0, and VB = VCC . The CB junction is therefore reverse-biased by VCC , and Q is cutoff, IC = 0. c) As in a), VB = VBE and IB = (VCC − VBE )/R. Again Q is in the active mode or saturated. Assume that Q is saturated. Then, VC = VCES , and IC = (VCC − VCES )/R. 12 +VCC +VCC R +VCC R IC IB R Q VB R IC IB VC VC Q VB Q IC (c) (b) (a) +VCC +VCC +VCC Q1 Q2 R R L IC2 VC2 2(IB) IR R R IC2 Q2 Q1 IR IR VC2 Q1 IC2 R Q2 VC2=VC4 Q3 L Q4 R1 R1 (d) (e) (f) Figure 11: Examples of finding correct operating modes of bipolar transistors. 13 Since VCC − VBE VCC − VCES <β = βIB , R R the device is indeed saturated, i.e., the initial assumption has been verified. IC = (18) d) The CB junction of Q1 is shorted and the EB junction of Q1 is forward biased from VCC through R. Therefore, Q1 is in the active region. The device with the base shorted to the collector is said to be diode connected. It behaves as a two-terminal pn diode. The EB junction of Q2 is forward biased by exactly the same voltage as the EB junction of Q1 . Therefore, IB1 = IB2 = IB , and Q2 is either in the active mode or in saturation. The current IR is given by IR = VCC − |VBE | = IC1 + 2IB . R (19) So, we can solve for the collector current of Q1 , IC1 = IR ≈ IR . 1 + 2/β (20) If Q2 is active, IC2 = βIB = IC1 ≈ IR , and the voltage across the load RL is RL IC2 ≈ RL IR . As long as the device is active, the load current is constant and set by IR , for any value of the load resistance RL . This is why the configuration (d), known as the current mirror is frequently used in integrated circuits as a current source. The condition for Q2 to operate in the active mode is that the CB junction of Q2 is reverse biased, which is the case for VC2 up to VCC − |VCES |. So, the current mirror operates as a current source for load resistances up to: RL < RLmax = VCC − |VCES | IR (21) For RL > RLmax , Q2 is saturated, and IC2 = (VCC − |VCES |)/RL is less than IR . e) This is the current mirror with npn transistors. We have exactly the same conclusions as in d), except that IC2 < IR because the voltage drop across R1 in the emitter of Q2 reduces the BE forward-bias voltage vBE2 with respect to vBE1 . To solve for IR we can still apply the approximation vBE ≈ VBE = 0.7V, IR = VCC − VBE , R (22) but to solve for IC2 , this approximation is inadequate because it would imply that IC2 = 0. Instead, since the solution depends on the difference between two forward-biased BE junctions, we need to use a more accurate exponential description of the device characteristic. From: vBE1 = vBE2 + R1 IC2 (23) we have VT ln IR IC2 = VT ln + R1 IC2 ICO ICO 14 (24) or VT ln IR = R1 IC2 , IC2 (25) which can be solved numerically for any given set of parameters. Note that for R1 = 0 we get IC2 = IR as in the current mirror d). f) This example combines the examples d) and e). Q1 and Q3 are diode-connected devices in the active mode, with IR = (VCC − 2|VBE |)/R. Assuming that Q4 is active, IC2 < IR , as found in e). Assuming that Q2 is active, IC2 = IR , which gives a contradiction. Therefore Q2 must be saturated with IC2 < IR = βIB2 , which confirms the saturation of Q2 . Finally, we have: VC2 = VC4 = VCC − |VCES |. You should try solving the examples again if all npn transistors are replaced with NMOS devices and all pnp transistors are replaced with PMOS devices. Assume that all MOSFETs have the same |Vt | < VCC and K. 4 Applications of small-signal (incremental) device models As discussed in Section 3, the purpose of dc biasing is to ensure that all devices are in the desired operating modes. The dc solution gives all steady-state dc voltages and currents. It is then of interest to predict the circuit response to time-varying (ac) inputs. This can be accomplished using the device large-signal nonlinear models. Unfortunately, for design-oriented hand analysis this approach usually yields intractable results, and little useful information. Instead, we simplify the task by linearizing the nonlinear device characteristics around the dc operating point. See the derivation of small-signal models for MOSFETS in Section 1.2 and BJTs in Section 2.2. The small-signal analysis can be applied to obtain results such as: • Input-to-output transfer function that shows how the signal propagates through the circuit. For example, we may want to determine the voltage gain of an operational amplifier in order to predict how the finite voltage gain affects some op-amp application. As another example, the small-signal analysis can be used to predict noise margins for a logic gate. This example is discussed in Section 4.1. • Input or output impedance that allows us to predict interactions among various parts of a larger circuit, input sensors, and output loads. For example, it is of interest to determine how large is the output resistance of a current source, i.e., how close the current source is to the ideal infinite output resistance. In general, the small-signal analysis results show how the quantity of interest (gain, impedance, or something else) depends on: 1. the device parameters, and 2. the dc operating point. 15 CMOS inverter: input-to-output characteristic (cmos.cir) 5.0V 1 2 (1.00,5.00) (2.125,4.59) VIL 4.0V (2.48,3.48) +VDD 3.0V Vtn=-Vtp=1V M2 vI 3 VDD=5V v 2.0V (2.51,1.51) O M1 1.0V (2.875,0.41) 4 (4.00,0.00) 5 VIH 0V 0V v(out) 1.0V 2.0V 3.0V 4.0V 5.0V Vin Figure 12: CMOS inverter and the vO (vI ) input-to-output characteristic. The device parameters are: Vtn = −Vtp = 1V, Kn = Kp = 30µA/V 2 , VA = 50V, VDD = 5V. As a result of the small-signal analysis, we can modify the design (change components, circuit configuration, or dc bias) in order to meet the specifications. As an introduction to small-signal analysis, we consider the example of finding the noise margins for a simple CMOS digital logic gate - an inverter. 4.1 Example: using small-signal analysis to determine the noise margins for a CMOS inverter The CMOS inverter and its large-signal input-to-output characteristic are shown in Fig. 12. Depending on the operating mode of the two devices, the input-to-output characteristic has 5 distinct segments. In segment 1, vI is less than the NMOS threshold voltage, vI < Vtn , so that M1 is cutoff. Since vSG2 is greater than the PMOS threshold voltage |Vtp |, and since the drain current of M2 is zero, M2 is in the triode mode. The output voltage is vO = VDD . In segment 2, vI > Vtn so that M1 moves from cutoff to saturation. The output voltage starts to drop as the current through M1 and M2 increases. M2 stays in the triode mode as long as vDG2 > |Vtp |, i.e., as long as vO − vI > |Vtp |. In segment 3, both M1 and M2 are in saturation. A small change in the input voltage causes a large change in the output voltage. In other words, the (negative) small-signal gain of the inverter in this segment is very large. M1 stays in saturation as long as vGD1 < Vtn , i.e., as long as vI − vO < Vtn . In segment 4, M1 is in the triode mode, and M2 is in saturation, as long as VSG2 > |Vtp |, i.e., as long as vI < VDD − |Vtp |. In segment 5, M2 is cutoff, M1 is in the triode mode, and vO = 0. 16 In the segments 2, 3, and 4, closed-form expressions for vO (vI ) can be obtained by solving iD1 = iD2 using the device large-signal nonlinear characteristics described in Section 1.1. Based on the characteristic of Fig. 12, the circuit in Fig. 12 can be used as a logic inverter: a logic LOW input level (close to zero) results in a logic HIGH output level (close to the supply voltage VDD ), and vice versa. The maximum input voltage that still corresponds to the logic LOW level is defined as the input voltage VIL such the slope of the vO (vI ) characteristic at vI = VIL is equal to −1. Similarly, the minimum input voltage that still corresponds to the logic HIGH level is defined as the input voltage VIH such that the slope of the vO (vI ) characteristic at vI = VIH is also equal to −1. Consider a logic gate with the dc voltage vI at the input, and a small noise voltage around this dc value. This logic gate is assumed to be in a chain of other similar logic gates. If vI is inside the allowed ranges, i.e., if vI < VIL , or vI > VIH , the output noise signal due to the input is smaller in magnitude than the input noise signal. Therefore, as long as vI < VIL or vI > VIH , reliable logic levels can be maintained in the chain of logic gates. If the input voltage vI is in the forbidden region VIL < vI < VIH , the noise is amplified, which may result in erroneous logic levels in the subsequent logic gates. This is why VIL and VIH , where the small-signal voltage gain of the gate is equal to −1, have been selected as the noise margin limits. The noise margins for reliable operation of a logic gate show how far an input voltage level can be from the nominal output voltage level, NML = VIL − VOL (26) NMH = VOH − VIH (27) In the CMOS inverter, the nominal output voltage levels are VOL = 0 (LOW) and VOH = VDD (HIGH). We can apply small-signal analysis to determine VIL , VIH and therefore the noise margins for the CMOS gate of Fig. 12. For simplicity, we assume that Kn = Kp = K and Vtn = |Vtp | = Vt . Let us first determine VIH in the segment (4) of the vO (vI ) characteristic. Since we know that M1 is in the triode mode, we start with the device large-signal device characteristic 2 iD1 = K 2(vGS1 − Vt )vDS1 − vDS1 , (28) and derive the device small-signal parameters following the approach described in Section 1.2. We assume that the total drain current iD1 consists of the dc value ID1 and a small ac signal component id1 , (29) iD1 = ID1 + id1 . We are interested in the response for the small ac signal only, which can be obtained by retaining only the first-order terms in the Taylor expansion of the large-signal characteristic: id1 = ∂iD ∂iD vgs1 + vds1 ∂vGS ∂vDS 17 (30) S2 (M2 in saturation) g G1=G2 v m2 i D1=D2 + + g vi v mt1 i - rdst1 vo - S1 (M1 in triode) Figure 13: The small-signal model of the CMOS inverter in segment 4 of the vO (vI ) dc characteristic. where the partial derivatives are computed at the dc operating point given by ID1 , VGS1 and VDS1 . The expression for small-signal components can be written in terms of circuit parameters as: 1 id1 = gmt vgs1 + vds1 (31) rdst where: ∂iD = 2KVDS1 , ∂vGS (32) ∂iD = 2K(VGS1 − Vt − VDS1 ) . ∂vDS (33) gmt = 1 rdst = Note the subscript t used to distinguish the small-signal parameters in the triode mode from the small-signal parameters gm and rds derived earlier for the MOS transistor in saturation (Eqs. (7) and (8)). In the segment 4, we know that M2 operates in saturation, and so the model of Fig. 6 and the parameters in Eqs. (7) and (8) can be applied. With VA → ∞, rds → ∞. The complete small-signal model of the CMOS inverter in segment 4 of the vO (vI ) characteristic is shown in Fig. 13. From the model, the boundary VIH can be determined from the condition that the smallsignal gain is equal to −1: vo = −(gm2 + gmt1 )rdst1 = −1 . (34) vi We evaluate the small-signal parameters at the point VGS1 = vI , VSG2 = VDD − vI , VDS1 = vO , VDD − vI − Vt + vO = vI − Vt − vO , which yields v O = vI − 18 VDD . 2 (35) (36) Finally, VIH is found at the intersection of the characteristic vO (vI ) and the straight line given by Eq. (36): VDD , (37) vO (VIH ) = VIH − 2 To solve for VIH , we make use of the expression vO (vI ) for the dc transfer function of the inverter in segment 4 of the characteristic. The solution to Eq. (37) is: VIH = VDD VDD − 2Vt + . 2 8 (38) Similarly, one can find the expression for VIL in segment 2 of the vO (vI ) characteristic, VIL = VDD − 2Vt VDD − . 2 8 (39) For numerical values: Vtn = −Vtp = 1V, and VDD = 5V, we have VIL = 2.125V, VIH = 2.875V, N ML = N MH = 2.125V. 4.2 Small-signal analysis techniques In this section we discuss how the small-signal device models can be applied efficiently so that the results for more complex circuits can be obtained with minimum of (usually messy) algebra. For now, we assume low-frequency signals so that the low-frequency device models can be applied. For efficient small-signal analysis, we rely on the following techniques: 1. prior knowledge of the incremental resistances “seen” looking into the device terminals; 2. prior knowledge of the final results for simple, frequently repeated circuits; 3. approximations based on known parameter relations, and applied before, and during the analysis, not after messy (and probably wrong) final results are obtained. 4. usual circuit-analysis short-cuts (voltage and current dividers, parallel and series impedance combinations, Thevenin and Norton equivalents). The incremental resistances “seen” at the device terminals can be determined just once, and then used as needed. Consider an arbitrary circuit shown in the left-hand side of Fig. 14. An arrow is used to indicate the port where we seek the incremental resistance (or impedance in general) seen between the port terminals. In general, the incremental resistance “seen” at a given circuit port can be determined by the small-signal analysis where a test source (voltage vt or current it ) is placed at the port and the response (current it or voltage vt ) is found. The incremental resistance Rx “seen” at the port is then found as Rx = vt /it . 4.3 MOS incremental resistances Fig. 15 shows the incremental resistances looking into the gate (G), source (S) and drain (D) terminals of a MOS transistor operating in saturation. We assume that the dc bias has been solved, and that the dc sources have been removed to obtain the small-signal model. External resistances RG , RD , RS are equivalent incremental resistances of the circuitry around the MOS 19 +VDD + circuit => Rx v it t Rx = vt/it small-signal model of the circuit Figure 14: Finding the resistance Rx “seen” when looking into a circuit port. transistor. An n-channel device is indicated, but the same results are obtained for a p-channel device. In this section, the symbol rds is used to represent the device incremental output resistance. Note that the symbol ro is also in common use, ro = rds . The circuits used to solve for the resistances are shown in Fig. 15(a,b,c). 4.3.1 Resistance seen looking into the gate, Rg From Fig. 15(a), Rg → ∞ (40) by inspection. At low frequencies, MOS gate is a very high resistance node. 4.3.2 Resistance seen looking into the drain, Rd To solve for Rd , we put a test current source it and find the voltage vt that the current source creates at the drain, as shown in Fig. 15(b): vt = RS it + (it − gm vgs )rds . (41) vgs = vg − vs = 0 − RS it , (42) vt = RS it + it (1 + gm RS )rds , (43) But, so that: and Rd = vt = rds + (1 + gm rds )RS . it (44) You may try to derive the same result using a voltage test source. Special cases and approximations The product gm rds is always much greater than 1, and so a somewhat simpler expression for Rd is obtained: Rd ≈ rds (1 + gm RS ) . (45) 20 RD RD + Rd RG v it G D t gmv gs Rs Rg rds S RS RS (a) small-signal model to find R g it G v D RG RD t + gmv gs G D RG rds gmv gs rds S S + RS v it t - (b) small-signal model to find R d (c) small-signal model to find R s Figure 15: Incremental resistances seen when looking into the gate (a), drain (b), and source (c) of a MOS transistor. 21 If, in addition, gm RS >> 1, Rd becomes: Rd ≈ gm rds RS (46) Note that for RS > 0, Rd can be much greater than either RS or rds . If RS = 0, i.e., if the source is at ac ground, the resistance seen looking into the device drain is just the device output resistance rds , VA . (47) Rd = rds = ID In the last expression, rds is shown as a function of the device parameter VA and the device dc operating current ID . In any case, even for RS = 0, the resistance Rd is relatively large. In other words, when the device operates in saturation, the drain current is almost independent of the drain-to-source voltage. 4.3.3 Resistance seen looking into the source, Rs To solve for Rs , we put a test voltage source vt and find the resulting current it , as shown in Fig. 15(c): vt − vd it = −gm vgs + . (48) rds Using vd = RD it , (49) and vgs = −vt , we obtain: it = gm vt + vt − RD it , rds (50) (51) which can be solved for Rs , vt rds + RD = . it 1 + gm rds You may try to derive the same result using a test current source. Rs = (52) Special cases and approximations As for Rd , we can use the fact that gm rds >> 1 for the device, so that Rs becomes: rds + RD 1 RD = + . (53) Rs ≈ gm rds gm gm rds The device output resistance rds is frequently much larger than the resistance RD seen in the drain of the device. If rds >> RD , we have the simplest result for Rs , 1 1 1 = √ = , (54) Rs ≈ gm 2K(VGS − Vt ) 2 KID which can be used in most applications. In the last expression, we explicitly use the fact that gm depends on the device parameters, K and Vt , and the dc operating current ID . Whenever RD < rds , the resistance seen looking into the source is in the order of 1/gm , which is relatively low. 22 RC Rc RB Re Rb RE Figure 16: Incremental resistances of the BJT. 4.4 BJT incremental resistances As for the MOS devices, we can determine the incremental resistances for the BJT. You may try to derive the results that are listed here with reference to Fig. 16. In this section, the symbol rce is used to represent the device incremental output resistance. Note that the symbol ro is also in common use, ro = rce . Using gm rce >> 1, we obtain the resistance Rb seen looking into the base: Rb = rπ + (1 + β)RE ≈ rπ + βRE . If RE = 0, Rb = rπ . The resistance Rc seen looking into the collector is: Rc = rce If RE >> rπ and RE >> RB , βRE 1+ RE + rπ + RB (55) . Rc ≈ βrce . (56) (57) If RE = 0, Rc = rce = VA /IC . In any case, Rc is relatively high. Using gm rce >> 1, we obtain the resistance Re seen looking into the emitter: Re = RB + rπ . 1+β (58) If RB << rπ , the simplest result for Re is obtained: Re ≈ 1 rπ 1 = = . β gm IC /VT 23 (59) In general, Re is relatively small. Small-signal analysis of more complex structures will make frequent use of the incremental device resistances derived in this section. 5 A Design Example The device-level design example in this section illustrates how basic single-transistor amplifier stages can be combined together to meet a set of design specifications. We make use of the MOSFET large-signal and small-signal characteristics summarized in Section 1, and the smallsignal analysis techniques discussed in Section 4. For discussion about configurations and properties of the basic single-transistor amplifier stages (common source, common-drain, and common-gate), refer to the suggested reference textbooks. Design Specifications A magnetic pick-up can be represented as an ac voltage source |vg | < 10mV in series with a Rg = 100kΩ resistance. It is desired to design a CMOS amplifier for the pick-up according to the following specifications: 1. the DC output voltage is VO = 0V; 2. the small-signal voltage gain is Ao = vo /vg = 10; 3. the DC bias current through vg must be equal to zero. 4. the amplifier output resistance is Rout ≤ 1kΩ; To design the amplifier, the following components are available: 1. 2 discrete resistors, and 1 large capacitor (C → ∞); 2. n- and p-channel enhancement-mode MOS devices; 3. two dc voltage sources, VDD = VSS = 10V, connected in series to obtain the ±10V supply around the ground. All transistors have the same parameters: Vtn = −Vtp = Vt = 1V, VA = 100V, and Kn = Kp = K = 20µA/V 2 for W/L = 1. The device conductance parameter K is directly proportional to the channel width W to length L ratio. For each device, the ratio W/L can be selected to scale K. It is not necessary that all devices have the same K. A solution consists of finding a suitable circuit configuration, and finding all device parameters (W/L of all MOSFETs, and resistances of all resistors) to meet the specifications. Solution The first step in the design is to choose a circuit configuration based on the design specifications. Since the required gain is |Ao | > 1, the amplifier should include at least one common-source (CS) stage. Since the gain of a CS stage is negative, two CS stages can be used to obtain the overall gain Ao > 0. The capacitor can be used either for injecting the ac signal to the input of 24 +VDD = 10V (W/L)2,3,5,7 = 1 (W/L)1 = 6.25 (W/L)4,6 = 25 R2 R1 V1 0.5mA I3 Q2 I1 I2 V2 IR VG Q1 900k Q3 20uA Q4 + Rg 20uA I1 C I3 Vo - Vg Q5 Q7 Q6 -VSS = -10V Figure 17: One possible solution to the design problem. the amplifier without disturbing the dc bias at the input, or to boost the gain of a CS stage by shorting the source to ac ground. Since both positive and negative supplies are available, the input can easily be dc biased at 0 volts, so that the pick-up can be connected directly to the input, without the capacitor in series. Instead, the available capacitor can be used to boost the gain of a CS stage by shorting the source to ac ground. The second CS stage can also be designed to satisfy the output-resistance specification. Alternatively, we may use a common-drain (CD, or source-follower) stage at the output, to meet the specified output-resistance, and also to obtain the zero output dc bias without additional discrete resistors. The amplifier stages can be biased using current mirrors. Based on the above considerations, a possible amplifier circuit is shown in Fig. 17. The input side of the current mirrors, Q7 , is dc biased from the dc supplies through R1 . The current-mirror outputs, Q5 and Q6 , serve as current sources to dc bias the input CS stage built around Q1 , and the output CD stage built around Q4 . Q6 is also the active load for Q4 . R2 is the load for the first CS stage. The output v1 of the first CS stage is the input to the second CS stage consisting of Q2 and Q3 . The source-to-gate of Q2 is dc biased by the voltage drop R2 I1 across R2 . The diode-connected device Q3 is the load for Q2 , and at the same time it provides the dc bias V2 at the gate of Q4 so that the output dc voltage VO can be adjusted to zero by selecting VGS3 = VGS4 . In the paper design, it is convenient to neglect the effects of finite VA on the dc bias solution, and on the small-signal results. Once the design is completed, the approximations can be verified. Also, we assume that all devices are biased to operate in saturation, which should be verified once the design is completed. A set of dc bias relations, and small-signal results can now be written for the circuit of 25 Fig. 17: R1 = VDD + VSS − VGS7 , IR (60) I1 = K5 IR , K7 (61) I3 = K6 IR , K7 (62) I2 = K2 (R2 I1 − Vt )2 , V2 = I2 + Vt , K3 vO = V2 − VGS4 = I2 − K3 (63) (64) I3 , K4 (65) The small-signal voltage gain can be found as: vo Ao = = vg v1 vg v2 v1 vo v2 gm2 ≈ (−gm1 R2 ) − (+1) , gm3 (66) while the output resistance is: Rout ≈ 1 gm4 . (67) For all devices the transconductance: gm = 2K(VGS − Vt ) = 2 KID (68) is evaluated at the appropriate dc operating point. Once the circuit configuration has been decided, and the necessary analytical results have been determined, we proceed to determine the parameter values in order to meet the design specifications. The set of design specifications is not sufficient to uniquely determine all parameter values. Additional design considerations, depending on the application, may include: 1. minimization of the total device area; for a given channel length L, we attempt to minimize the ratios W/L for the devices; 2. minimization of the quiescent power consumption; we attempt to minimize dc bias currents; 3. ability to handle large-amplitude ac signals without distortion; we attempt to dc bias the amplifier so that the dc operating point is as far away from the operating-mode boundaries (triode or cut-off) as possible; 4. frequency-response and transient-response specifications. 26 None of these additional constraints have been specified in this design problem, so that we have some freedom in selecting the values. Consider first the output-resistance requirement. From Eqs. (67) and (68), we have: 1 = 1kΩ . Rout = √ 2 K4 I3 (69) Select I3 = 0.5mA, as a compromise between large power consumption and large device size. As a result, K4 = 500µA/V 2 , and K4 = 25 . (70) K Note how a relatively large device and a relatively large dc bias current are needed to meet the small output resistance requirement. For Q2 , Q3 , Q5 and Q7 , we select the minimum-size devices, (W/L)2,3,5,7 = 1, biased at (W/L)4 = IR = I1 = I2 = I3 0.5mA K = 20µA . = K4 25 (71) To get I3 = 0.5mA, we also select K6 = K4 , i.e., (W/L)6 = (W/L)4 = 25. The dc gate-to-source voltage for all devices above is: |VGS |2,3,4,5,6,7 = Vt + IR = Vt + K I3 = 2V . K4 (72) From Eq. (60), we have R1 = 900kΩ, and from Eq. (63), we have R2 = 100kΩ. Also, VO = VGS3 − VGS4 = 0V, as required. Since K2 = K3 = K, and Q2 , Q3 have the same dc bias current I2 = IR = 20µA, the small-signal gain from v1 to v2 is v2 /v1 = −gm2 /gm3 = −1. Therefore, the gain requirement from Eq. 66 becomes Ao = gm1 R2 = 10 , (73) which yields: Ao = 2 K1 I1 R2 = 10 , K1 = Ao 2R2 2 1 = 125µA/V 2 . I1 Therefore, (74) (75) K1 = 6.25. (76) K To verify the assumption that rds is sufficiently large, we have (rds )1,2,3,5,7 = VA /20µA = 5M Ω >> R2 = 100kΩ > 1/gm , and (rds )4,6 = VA /0.5mA = 200kΩ >> 1/gm = 1kΩ. Some loss in the gain because of the finite rds can be easily compensated for by rounding (W/L)1 up. We proceed to confirm that that all devices are in saturation at the dc bias operating point. For the specified amplitude of the input signal, |vg | ≤ 10mV, it is also easy to confirm that all devices remain in saturation for all time when the ac input is applied to the input. The ac voltages at v1 , v2 and vo are within ±100mV around the dc bias. As an excercise, run PSpice simulations of the circuit in Fig. 17 to verify that it meets all design specifications. (W/L)1 = 27