9.15 schottky-clamped ttl

9.15

Schottky-Clamped TTL 623

9.15

SCHOTTKY-CLAMPED TTL

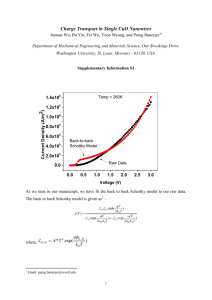

As discussed in Sec. 9.13, saturation of the transistors in TTL logic substantially slows down the dynamic response of the logic gates. The Schottky-clamped transistor drawn in Fig. 9.69 was developed to solve this problem. The Schottky-clamped transistor consists of a metal semiconductor

Schottky barrier diode in parallel with the collector-base junction of the bipolar transistor.

When conducting, the forward voltage drop of the Schottky diode is designed to be approximately 0.45 V, so it will turn on before the collector-base diode of the bipolar transistor becomes strongly forward-biased. Referring to Fig. 9.69, we see that v

C E

= v

B E

− v

S D

=

0

.

70

−

0

.

45

=

0

.

25 V (9.101)

The Schottky diode prevents the BJT from going into deep saturation by diverting excess base current through the Schottky diode and around the BJT. Because the BJT is prevented from entering heavy saturation, 0.7 V has been used for the value of v

B E in Eq. (9.101).

+ v

SD

–

Ohmic contact

E

B

Schottky diode

C

+ v

BE

–

+ v

CE

– n

+ p n n

+ p isolation

Figure 9.69

Schottky-clamped transistor.

Figure 9.70

Cross section of the merged

Schottky diode and bipolar transistor structure.

A cross section of the structure used to fabricate the Schottky transistor is given in Fig. 9.70.

Conceptually, an aluminum base contact overlaps the collector-base junction, forming an ohmic contact to the p -type base region and a Schottky diode to the more lightly doped n -type collector region. (Remember that aluminum is a p -type dopant in silicon.) This is another example of the novel merged structures that can be fabricated using IC technology.

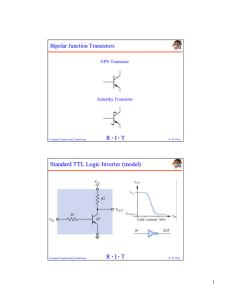

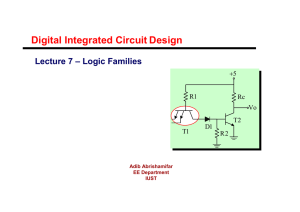

In Fig. 9.71, both transistors in the TTL inverter have been replaced with Schottky-clamped transistors, and the resulting gate is the prototype for a Schottky TTL inverter.

With a high-input level applied to the gate, as in Fig. 9.72, a base current of i

B 2

= (β

R

+

1

) i

B 1 attempts to saturate Q

2

.

4 k

Ω

V

CC

= +5 V

2 k

Ω

4 k

Ω

V

CC

= +5 V

2 k

Ω v

O i

B 1

0.45 V

Q

2

0.25 V v

I

Q

1

Q

2

5 V

Q

1

B

1

0.7 V

Figure 9.71

Prototype TTL inverter with Schottky-clamped transistors.

Figure 9.72

Prototype Schottky TTL gate with input at V

H

.

624 Chapter 9 Bipolar Logic Circuits

4 k

Ω

0.7 V

0.25 V i

B 1

Q

1

0.25 V

0.95 V

0.45 V i

C 2

≈

0

0.5 V

V

CC

= +5 V

2 k

Ω

5 V

Q

2

“Off ”

A

B

C

+ 5 V

R

B

2.8 k

Ω

R

C

900

Ω R

S

50

Ω

Q

1

R

2

500

Ω

Q

5

Q

3

R

5

3.5 k

Ω

Q

4 v

O

R

6

250

Ω

Q

6

Q

2

Figure 9.73

Prototype Schottky TTL gate with input at V

L

.

Figure 9.74

Schottky TTL NAND gate.

The Schottky diode prevents by Eq. (9.101). Thus, V

L

Q

2 from heavily saturating, and

= 0 .

25 V for this inverter.

Figure 9.73 shows the Schottky inverter with input the 4-k resistor causes Q

1 to saturate, with its v

C E v

I

= V v

C E

L is limited to 0.25 V, as given

= 0 .

25 V. The current through clamped to 0.25 V by the Schottky diode.

The resulting base-emitter voltage of turn on Q

2

. Thus, Q

2 is off and V

H

Q

2 is 0.5 V, which is 200 mV below the voltage required to

=

5 V.

Invention of this circuit required a good understanding of the exponential dependence of the

BJT collector current on base-emitter voltage as well as knowledge of the differences between

Schottky and pn junction diodes. Successful manufacture of the circuit relies on tight process control to maintain the desired difference between the forward drops of the base-emitter and

Schottky diodes.

Figure 9.74 is the schematic for a full three-input Schottky TTL NAND gate. Each saturating transistor in the original gate — Q

1

, Q

2

, and Q

3

— is replaced with a Schottky transistor.

Q

6

, R

2

, and R

6 replace the resistor R

E in the original TTL gate and eliminate the first “knee” voltage corresponding to V

I L in the VTC in Fig. 9.60. Thus, the transition region for the Schottky TTL is considerably narrower than for the original TTL circuit (see Probs. 9.115 to 9.117).

Q

5 provides added drive to emitter follower Q

4 original TTL gate.

Q

4 and eliminates the need for the series output diode D

1 cannot saturate in this circuit because the smallest value for v

C B 4 in the is the positive voltage V

CESAT5

, so it is not a Schottky transistor. The input clamp diodes are replaced with Schottky diodes to eliminate charge storage delays in these diodes.

The use of Schottky transistors substantially improves the speed of the gate, reducing the nominal delay for the standard Schottky TTL series gate (54S/74S) to 3 ns at a power dissipation of approximately 15 mW. An extremely popular TTL family is low-power Schottky TTL

(54LS/74LS), which provides the delay of standard TTL (10 ns) but at only one-fifth the power.

This gate is shown in Fig. 9.75. The resistor values are increased to decrease the power, but speed is maintained at lower power by eliminating the storage times associated with saturating

A

B

9.15

Schottky-Clamped TTL

R

B

20 k

Ω

R

C

+

5 V

8 k

Ω

D

1

D

2

R

S

120

Ω

Q

4

Q

5

Q

2

D

3

D

4

R

5

4 k

Ω v

O

625

R

2

1.5 k

Ω

R

6

3 k

Ω

Q

6

Q

3

Figure 9.75

Low-power Schottky TTL NAND gate.

transistors. This family is widely used to replace standard TTL because it offers the same delay at substantially less power.

As IC technology has continued to improve, the complexity and performance of TTL has also continued to increase. The advanced Schottky logic (ALS) and advanced low-power Schottky logic families were introduced with improved power-delay characteristics. The increasing complexity is apparent in the 54ALS/74ALS circuit in Fig. 9.76. Note the use of pnp transistors at the input.

A

Q

4

B

R

40 k

Ω

1

R

2

60 k

Ω

R

3

15 k

Ω

+

5 V

Q

1

Q

5

D

1

Q

6

D

3

Q

2

50 k

R

4

Ω

R

5

4 k

Ω

Q

3 v

O

D

2

R

6

3 k

Ω

R

Q

7

7

6 k

Ω

Q

8

Figure 9.76

Advanced low-power Schottky TTL NAND gate.