Digital Integrated Circuit Design

advertisement

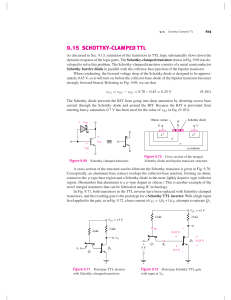

Digital Integrated Circuit Design Lecture 7 – Logic Families +5 R1 Rc Vo T1 Adib Abrishamifar EE Department IUST D1 T2 R2 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 2/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Logic Families on a Glance } Based on Underlying Semiconductor Technology } Transistor-Transistor Logic: TTL • Bipolar technology • Dual-in-line package (DIP) • Surface-mount technology (SMT): Smaller } Metal Oxide Semiconductors: MOS • Metal Oxide Semiconductor (MOS) technology • Very low power Notch Dot Pin 1 IUST: Digital IC Design 3/129 LECTURE 7 : Logic Families Pin 1 Adib Abrishamifar 2008 Logic Families on a Glance } TTL Families } } } } } } } 74 74L 74H 74S 74LS 74AS 74ALS IUST: Digital IC Design Standard Low power High speed Schottky Low power Schottky Advanced Schottky Advance Low power Schottky 4/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Logic Families on a Glance } Standard, 74 series - introduced by Texas Instruments in 1964 } Low-power, 74L series - large resistor values reduce power dissipation } High-speed, 74H series - small resistor values & Darlington pair reduce propagation delay } Schottky, 74S series - Schottky barrier diode is used to reduce time delay } Low-power Schottky, 74LS series - like 74S but uses larger resistor values } Advanced Schottky, 74AS series - improved version of 74S } Advanced low-power Schottky, 74ALS – has the lowest power-speed product IUST: Digital IC Design 5/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Logic Families on a Glance } CMOS Families } } } } 40xx/45xx 74C 74HC 74ACT IUST: Digital IC Design 6/129 Metal-gate CMOS TTL-compatible CMOS High speed CMOS Advanced CMOS-TTL compatible LECTURE 7 : Logic Families Adib Abrishamifar 2008 Logic Families on a Glance } 4000/14000 series - introduced by RCA/Motorola } 74C series - pin for pin and function for function compatible with TTL devices having the same number, e.g. CMOS 74C74 and TTL 7474 } 74HC series - high speed (comparable with TTL) and higher output current } 74HCT series - voltage levels compatible with that of TTL devices, i.e. a TTL device can directly drive a 74HCT device } Compared to TTL families ; lower power dissipation and slower speed IUST: Digital IC Design 7/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Logic Families on a Glance } Advanced CMOS Logic } First-Generation Devices • No output slew rate control – Serious noise! } Second-Generation Devices • Output slew rate control or TTL level output voltages } Third-Generation Devices • Vcc : 3.3V • Logic families optimized IUST: Digital IC Design 8/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Logic Families on a Glance } Advanced CMOS Logic Logic Family Manufactures First Generation, 5V 54/74 AC, ACT 54/74 AC11, ACT11 54/74FCT, FCT-A 29C800 National, Motorola, Harris Texas Instruments, Philips IDT, Cypress, Harris AMD Second Generation, 5V 54/74ACQ, ACTQ 54/74FCT-T, FCT-AT, FCT-CT National IDT Third Generation, 3.3V 54/74LVQ 54/74FCT3 74LVC IUST: Digital IC Design 9/129 National IDT Texas Instruments LECTURE 7 : Logic Families Adib Abrishamifar 2008 Logic Families on a Glance } Logic family letter designator } 5V family: AC, ACT, FCT, etc • With T, TTL compatible input threshold voltage levels at normal TTL supply } Low-voltage: LVC, LVQ, FCT3, etc • TTL compatible input threshold } FCT and 29C800 families } Bus interface families • They are not true logic families since they don’t have NANDs, NORs, etc IUST: Digital IC Design 10/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Logic Families on a Glance } BiCMOS Logic } BiCMOS technology • CMOS input structure + CMOS internal logic + Bipolar output structure • high speed, high drive, low power Logic familiy 54/74ABT 74BC 54/74BCT 54/74LVT IUST: Digital IC Design 11/129 Manufactures Texas Instruments, Philips Motorola, Toshiba Texas Instruments Texas Instruments LECTURE 7 : Logic Families Adib Abrishamifar 2008 Logic Families on a Glance } Simple Comparison of Logic Families Gate / Par. CMOS 74HC Static P.(mw/Gate) 25 ´ 10-6 TTL 74S 19 74ALS 74AS 1 8.5 4000 74 74LS 10-3 10 2 19 1 8.5 3 4 1.5 100KHz (mw/Gate) 0.17 0.1 10 PDT(ns) 50 10 Max Fr.(MHz) 8 40 2 10 12 35 40 125 70 200 S ´ P(Pj) 1.4 100 20 57 4 13 Fanout 10 11 4 40 -1.6 20 50 20 50 -0.4 -2 -0.1 -0.5 Max in. Current (mA) IUST: Digital IC Design 0.001 12/129 0.001 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 13/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Diode Logic (DL) } In this lecture we assume the following parameters for a PN junction and Bipolar transistor Parameter Value Vg 0.7V VBEoff 0.5V VBEon 0.7V VBEsat 0.8V VCEsat / max 0.1/ 0.2V IUST: Digital IC Design 14/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 DL A B Vo +10 0 0 0.7 R 0 5 0.7 5 0 0.7 5 5 5.7 A B Vo } AND Gate IUST: Digital IC Design 15/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 DL } If we series the two equal DL sections the minimum of output voltage will be increased +10 R +10 R A Vo Min = 2 ´ 0.7 = 1.4 IUST: Digital IC Design 16/129 B LECTURE 7 : Logic Families Vo Adib Abrishamifar 2008 DL } Vg Canceling +10 10K A Þ Vo Max Þ Vc Max 10 - 0.7 = ´ 4 = 2.66 10 + 4 = 3.36 C Vo B 4K ìVi £ 2.66 Þ Vc = Vi + 0.7 Þ V0 = Vi Þí îVi ³ 2.66 Þ Vo = 2.66 IUST: Digital IC Design 17/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 DL } VTC } What is the value of NM=? Vo 2.66 2.66 IUST: Digital IC Design 18/129 LECTURE 7 : Logic Families Vi Adib Abrishamifar 2008 DL } OR Gate } Vth may be selected equal to zero A B Vo 0 0 -0.7 A B Vo 0 5 5-0.7 5 0 5-0.7 4K 5 5 5-0.7 Vth IUST: Digital IC Design 19/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 DL } XOR A B AB R Vth A B Y = AB + AB AB R 4K Vth Vth IUST: Digital IC Design 20/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 DL } Wired OR } Open (normally collector) outputs connected together to a common pull-up (or pull-down) resistor } Any collector can pull the signal line low IUST: Digital IC Design 21/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 DL } Wired OR A B A+B Y = A+B+C+D R B C Vth C D A D C+D Y = A+B+C+D R R Vth Vth IUST: Digital IC Design 22/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 DL } Wired AND A B A+B Y R Vth C D CD R Vth IUST: Digital IC Design 23/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 24/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Resistor Transistor Logic (RTL) } The first active Gate (NOR) Vcc = +3.6 Rc 640 out A Rb 450 B Rb 450 C Rb 450 I IH 450 } Rb for Vbe equalization IUST: Digital IC Design 25/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 RTL } It is not good for NAND Gate because the output must be only grounded when all of three transistors are activated (Thermal consideration,…) Vcc - VCEsat 3.6 - 0.1 = = 5.47mA Rc 640 Icsat 5.47 = = = 0.182mA [10 £ bmin £ 50] bmin 30 ICS = I Bsat Þ VIH = VBEsat + 450W ´ 0.182mA = 0.88 Þ VIH = 0.88 VBEon = 0.7 Þ VIL » 0.5 (it is not a standard but we assume) Þ NML=VIL -VOL =0.5-0.2=0.3 IUST: Digital IC Design 26/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 RTL } NML is low then choose the VOH for NMH>0.3 NMH = VOH - VIH Þ 0.3 = VOH - 0.88 Þ VOH = 1.18V } This value is used for calculating Fan out 3.6 - 1.18 IOH = = 3.78mA 640 1.18 - 0.8 I IH = = 0.844mA 450 IOH 3.78 Þ Fanout = FO = = = 4.48 ® FO = 4 I IH 0.844 IUST: Digital IC Design 27/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 RTL } VTC Vo 0.1 0.5 VIL IUST: Digital IC Design 28/129 VIH LECTURE 7 : Logic Families Vi Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 29/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 DTL +4 } Disadvantages: Vcc = +4 } Two Supplies are needed } One more pin is needed 4K R1 2K A B D1 D4 D3 D2 Vc Vo T1 R2 5K Vbb = -2 NAND } Advantages: } D3,D4 are always on IUST: Digital IC Design 30/129 Switching and NM are good LECTURE 7 : Logic Families Adib Abrishamifar 2008 Diode Transistor Logic (DTL) } NM +4 NML = VIL - VOL VIL = 0.7 + 0.7 + 0.5 - 0.7 = 1.2V Vcc = +4 VOL = 0.2 Þ NML = 1.2 - 0.2 = 1V NMH = VOH - VIH R1 2K VOH = VOH = 4V A VIH = ? B Vc = 2 ´ 0.7 + 0.8 = 2.2 VA,B ³ Vc - 0.7 = 1.5 = VIH Þ NMH = 4 - 1.5 = 2.5V Þ NM = 1 What is the min. of β? 4 - 2.2 VA , VB > 1.5 Þ I R1 = = 0.9mA 2K 0.8 - (-2) IR 2 = = 0.56mA Þ I B = 0.9 - 0.56 = 0.34mA 5 I 4 - 0.1 0.975 Icsat = = 0.975mA Þ b min = csat = Þ bmin = 2.9 4 I Bsat 0.34 IUST: Digital IC Design 31/129 LECTURE 7 : Logic Families 4K Vo D4 T1 D1 D3 D2 Vc R2 5K Vbb = -2 NAND Adib Abrishamifar 2008 DTL } Fan-Out I IH » 0 Þ FO H = ¥ +4 Vcc = +4 FO L : 4 - 0.8 2 - 0.6 = = = 0.28mA 1.6mA, I R 2 K K 2 5 A Þ I IL = 1.6mA - 0.28mA = 1.32mA(out of Gate) B (VA , VB = 0.1) Þ I R1 = Icsat = bI Bsat = 30 ´ 0.34mA = 10.2mA 10.2mA - 0.975mA FO L = = 7.44 ® FO L = 7 1.32 Þ FO = 7 IUST: Digital IC Design 32/129 LECTURE 7 : Logic Families R1 2K D1 D3 D2 Vc 4K D4 Vo T1 R2 5K Vbb = -2 NAND Adib Abrishamifar 2008 DTL } Pdis } We have 3-state for output high (input low) and 1-state for low } Pdis=3/4PdisL+1/4PdisH Vcc = +4 PdisL = VccI R1 + VBB I R 2 - VIL I IL = 4 ´ 1.6mA + 2 ´ 0.28mA - 0.1´ 1.32mA = 6.828mW PdisH = Vcc(I R1 + I Rc ) + VBB I R 2 = 4(0.975mA + 0.95mA ) + 2 ´ 0.5 = 8.8mW 1 Þ Pdis = [3 ´ 6.828 + 1´ 8.8] = 7.321mW ® Better than RTL 4 +4 4K R1 2K A B D4 D1 D3 Vc D2 Vo T1 R2 5K Vbb = -2 NAND } VBB is needed for better switching of transistor IUST: Digital IC Design 33/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 34/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Modified DTL (MDTL) VBB , D3 ® Q1 +5 R3 1.75K Q1, D4 = on Þ Q2 Charges very rapidly In input we need the Base current Þ Fan-Out is increased Vcc ® +5V 5 - 0.1 Icsat = = 0.8mA K 6 Q1 is never saturated V1 = 0.7 + 0.7 + 0.8 = 2.2V Þ VIH = 2.2 - 0.7 = 1.5V Rc 6K R1 2K A B D1 D2 V1 Q1 D4 R2 5K Vo Q2 VIL = 0.5 Q1 + 0.7 D + 0.5 Q2 - 0.7 = 1V VOL = 0.2 IUST: Digital IC Design 35/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 MDTL NML = 1 - 0.2 = 0.8 VOH = 5 NMH = 5 - 1.5 = 3.5 Þ NM = 0.8 Vin = +0.1 Þ I IL = 5 - 0.8 = 1.12mA K K 2 + 1.75 0.8 ì 5 - 2.2 ï 25.75mA, I B2 = (b1 + 1)I BQ1 I BQ1 = Two inputs High = =í R2 R1 + (1 + b1 )R3 ï îb1 = 60 Þ I R 3 = 1.57mA PdisL = VccI IL - VIL I IL = 5 ´ 1.12 - 0.1´ 1.12 = 5.488mW PdisH = Vcc(I R 3 + I Rc ) = 5(1.57 + 0.8) = 11.85mW Pdis = IUST: Digital IC Design 36/129 Rc LECTURE 7 : Logic Families 6K R1 2K A 1 (3 ´ 5.488 + 1´ 11.85) » 7mW 4 +5 R3 1.75K B D1 D2 V1 Q1 Vo Q2 D4 R2 5K Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 37/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Transistor Transistor Logic (TTL) +5 R1 Rc +5 6K Rc A Vo Vo Q2 B V1 R2 TTL DTL IUST: Digital IC Design 38/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 TTL } Multi Emitter Cross Section +5 E1 E2 + + B C Rc Vo N N P N + V1 N IUST: Digital IC Design 39/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 TTL } If input is low +5 Þ V1 = 0.1(Low) + 0.1(VCEsat ) = 0.2V Rc Vo } In this configuration the pull down is very good but pull up is not, because the output configuration is CE } In CC the situation is Reverse! } By combining this two configurations we have a better output stage! IUST: Digital IC Design 40/129 LECTURE 7 : Logic Families V1 Adib Abrishamifar 2008 TTL } Totem Pole Output +5 100W (Protection) T2 T1 Vi (Phase Splitter) D T3 C Vi = High ® T1 = sat, T3 = sat Þ D is used for T2 = off IUST: Digital IC Design 41/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 42/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Standard TTL +5 R1 R2 1.6K 4K T3 Vc2 T1 Vc1 R4 130W T2 D Vo T4 R3 IUST: Digital IC Design 43/129 1K LECTURE 7 : Logic Families Adib Abrishamifar 2008 Standard TTL } VTC Vi = 0.1V Þ Vc1 = 0.2 Þ T2, T4 = off Þ Vc2 » 5V Þ VOH = 5 - 2 ´ 0.7 = 3.6V Vi = 0.6V Þ Vc1 = 0.7V Þ T2 = on ® Vo ¯ Vi = 1.3V Þ Vc1 = 1.4V Þ T2, T4 = on 0.7 V Þ I E 2 = (I B4 » 0) + K » 0.7mA 1 Þ VR 2 = 0.7 mA ´ 1.6K = 1.12V Þ Vc2 = 5 - 1.12 » 3.9V Þ Vo = 3.9 - 1.4 = 2.5V Vi = 1.5V Þ Vc1 = 1.6V Þ T2, T4 = sat Þ Vo = 0.1V IUST: Digital IC Design 44/129 +5 R1 Vo R2 1.6K 4K T3 Vc2 T1 Vc1 3.6 R4 130W T2 D Vo T4 R3 1K 2.5 0.1 LECTURE 7 : Logic Families 0.6 1.3 1.5 Vi Adib Abrishamifar 2008 Standard TTL } Fan (In, Out) Vi > 1.5V Þ VBCT1 = 0.7 (VBET1 < 0.6) Þ T1 = Reverse Mode I E = bR I B , IC = (bR + 1)I B , I B = å NI 5 - 2.3 = 0.675mA, bR = 0.2 K 4 +5 E1 = bR I B R1 0.2 ´ 0.675 Þ I E1 = = 0.0675mA = 67.5mA 2 In DTL it was equal to Io » 0 mA IUST: Digital IC Design 45/129 LECTURE 7 : Logic Families R2 1.6K 4K T3 Vc2 T1 Vc1 R4 130W T2 D Vo T4 R3 1K Adib Abrishamifar 2008 Standard TTL } Fan (In, Out) 5 - 0.9 » 1mA K 4 5 - 0.9 41 41 0.8 = = , I = - K = 1.76mA Bsat 4 K 1.6 16 16 1 = bmin I Bsat 4 = (b = 10) ´ 1.76 = 17.6mA I IL = I E = I B + IC » I B = Icsat 2 Icsat 4 +5 R1 R2 1.6K 4K T3 Vc2 T1 Vc1 R4 130W T2 D Vo T4 R3 1K IR 4 17.6mA Þ FO L = mA = 17, FO H = > FO L Þ FO = FO L = 17 67.5mA 1 Real FO = 10 (bmin = 6) IUST: Digital IC Design 46/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Standard TTL } NM } Accept the following values because VTC has not high slope VOH = 2.5V, VIH = 1.5V, VIL = 1.3V, VOL = 0.2V Þ NMH = VOH - VIH = 2.5 - 1.5 = +1V NML = VIL - VOL = 1.3 - 0.2 = 1.1V Þ NM = 1V IUST: Digital IC Design 47/129 Vo 3.6 2.5 0.1 0.6 LECTURE 7 : Logic Families 1.3 1.5 Vi Adib Abrishamifar 2008 Standard TTL } Pdis PdisL = (T2 = off ) = 5V ´ 1mA - 0.1V ´ 1mA = 4.9mW PdisH = ViIi + (I R1 + I R 2 )Vcc + VOL IiL = 3.6V ´ 67.5mA + (0.675mA + 2.56mA ) ´ 5V + 0.1V ´ 1mA = 16.53mW 1 Þ Pdis = (3 ´ 4.9mW + 1´ 16.53mW ) 4 » 8mW +5 R1 R2 1.6K 4K T3 Vc2 T1 Vc1 R4 130W T2 D Vo T4 R3 IUST: Digital IC Design 48/129 LECTURE 7 : Logic Families 1K Adib Abrishamifar 2008 Standard TTL } Layout Vcc R3 1.6K R1 4K Q4 A B R4 130W Q2 D1 Q1 Out Q3 R2 IUST: Digital IC Design 1K 49/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Family on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Threshold Logic (HTL) } High Speed TTL (74HXX) } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 50/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 High Threshold Logic (HTL) +V R1 R4 R2 A B IUST: Digital IC Design 51/129 D1 D2 Q1 Vo Q2 Z1 R3 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Threshold Logic (HTL) } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 52/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 High Speed TTL (74HXX) } In previous T1 , T2 , (T3) and T4 can be saturated but in this circuit T5 prevent T3 from going to saturation } After T2=off , T6 discharges the base of T4 then the switching speed of T4 is very high } In previous we could not decrease the R3, because the current for conducting T4 must be increased!! } D is used for compensating the ringing IUST: Digital IC Design 53/129 +5 R1 4K R 130W R2 1.6K T5 T3 T1 D T2 D 500 LECTURE 7 : Logic Families R4 Vo T4 R ¢3 250 T6 Adib Abrishamifar 2008 HSTTL } VTC } TTL has a curvature in VTC for R3 because at first T2=on and then T4=on, but in this circuit T2,T4 must be conducted together Vo 3.6 +5 R1 4K R 130W R2 1.6K T5 T3 T1 D T2 R4 D 500 Vo T4 R ¢3 250 0.1 1.3 1.5 T6 IUST: Digital IC Design 54/129 LECTURE 7 : Logic Families Vi Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 55/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Tri-State Logic } Totem-pole outputs should not be tied together } Therefore, tri-state bus driver or open collector output can be used to prevent this problem } Usually used to bus multiple signals on the same wire } Advantage: The output of tri-state ICs can be connected together without sacrificing switching speed IUST: Digital IC Design 56/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Tri-State Logic } Tri-state logic has three possible output states: } } } high low high impedance (Hi-Z) } Tri-state logic is used as bus-driver where more than one output can be connected together } There is an input controlling the output state, enable or disable Enable state: The output operates as a conventional gate, the output level is either high or low Disable state: The output is an open circuit, it is the Hi-Z state IUST: Digital IC Design 57/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Tri-State Logic } } Tri-state bus driver can be non-inverting or inverting When more than one outputs are connected to a bus, only one of them can be at enable state, the others must be disabled. Otherwise, excessive current will flows through the output stage (in case of TTL) or output will be at abnormal level (in case of CMOS) IUST: Digital IC Design 58/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Tri-State Logic } Example1 +5 R4 130W T3 D Vo T4 Disable Signal IUST: Digital IC Design 59/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Tri-State Logic } Example2 +5 R R2 R1 T5 T3 T2 T1 R4 D D = 0 (off ) Vo T4 R3 = 1 (on) IUST: Digital IC Design 60/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 61/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Storage Delay Time } This delay has a max respect to other therefore must be reduced } One method for reduction is as follow +5 Rc R1 R2 R3 IUST: Digital IC Design 62/129 _ Vo + Do not saturate LECTURE 7 : Logic Families Adib Abrishamifar 2008 Storage Delay Time } Schottky Diode } In previous method we need a large area } Another method is using schottky transistor + E _ P N+ B C N+ N IUST: Digital IC Design 63/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 64/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Schottky TTL (74SXX) } High speed variant of TTL } Schottky transistors which have faster switching speed } Schottky-barrier diode connected from base to collector to prevent transistor from going into saturation IUST: Digital IC Design 65/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Schottky TTL } All of transistor (except T3) are replaced by schottky transistor +5 2.8K 50 900W T5 T3 T1 T2 3.5K Vo T4 500 250 T6 IUST: Digital IC Design 66/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Schottky TTL } NM +5 VDonsh = VBConsh = 0.5V VBEsat 4 = 0.8V, VBCon 4 = 0.5V Þ VCEsat 4 = 0.3V 2.8K T5 Þ VOL = 0.3V = VOL , VIL = 0.7 NM = 0.4V T3 T1 T2 VOH = 3.6V 3.5K Vo T4 VOH = 5 - 1.6 = 3.4V 500 VIH = 1.3V IUST: Digital IC Design 50 900W 250 T6 67/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Schottky TTL } VTC +5 Vo 3.6 2.8K 50 900W T5 T3 T1 T2 3.5K Vo T4 500 0.3 1.1 IUST: Digital IC Design 1.3 VIH 68/129 250 T6 Vi LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 69/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Low Power Schottky Clamped TTL (74LSXX) } The input do change as figure +5 } Resistors are large } Component function • D1, D2: AND function A • D5, D6: High-speed D5 clamping of input signal excursions below ground • D3, D4: Stored charge B D6 removal of the base of T2 and T3 on Positive transition of the input • 20KW resistor connected to D1 and D2: Small amount of current source IUST: Digital IC Design 70/129 120 8K 20K T2 D1 T3 D3 D2 LECTURE 7 : Logic Families V1 1.5K T1 40K Vo D4 T5 3K T4 Adib Abrishamifar 2008 LSTTL } NML +5 20K 5 - (0.3 + 0.5) I IL = = 0.21mA K 20 VOL = 0.3V A VOH = 5 - 1.4 = 3.6 B 120 8K T2 D1 T3 D3 D2 VIL = (0.5 T1 + 0.5 T5 ) _ 0.5 D2 = 0.5V VOL = VOL = 0.3V V1 1.5K T1 40K Vo D4 T5 3K T4 NML = 0.5 - 0.3 = 0.2V IUST: Digital IC Design 71/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 LSTTL +5 } VTC Vo 20K 3.6 A B 0.3 0.9 1.1 Vi 120 8K T2 D1 T3 D3 D2 V1 1.5K T1 40K Vo D4 T5 3K T4 (0.7 T1 + 0.7 T 4 ) - 0.5 D2 IUST: Digital IC Design 72/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 73/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Advanced Schottky (74ASXX) } In the early to middle 1980s } Discontinuing } Letter designator } F: fast advanced Schottky TTL } ALS: advanced low-power Schottky TTL } AS: advanced Schottky TTL } Selection criteria of FAST vs. AS } Price, availability IUST: Digital IC Design 74/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Advanced Schottky (74ASXX) +5 900W 2.7K A T2 D1 T3 3K5 D4 B D2 T1 D5 500 D3 T5 Vo D6 300 T4 Re s ¯, I -Þ AS IUST: Digital IC Design 75/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Advanced Schottky (74ASXX) } Input circuit } Component function • D1, D2: AND function • D4, D5: High-speed clamping of input signal excursions below ground • D3: Stored charge removal of the base of T3 in output on Positive transition of the input • 2.7KW resistor connected to D1 and D2: Small amount of current source IUST: Digital IC Design 76/129 +5 900W 2.7K A T2 D1 T3 3K5 D4 D2 B T1 D5 LECTURE 7 : Logic Families 500 D3 T5 Vo D6 300 T4 Adib Abrishamifar 2008 Advanced Schottky (74ASXX) } Output circuit } T2, T3: Darlington pair } D6: negative voltage excursions reductions due to reflection caused by transmission-line effects +5 900W 2.7K A T2 D1 T3 3K5 D4 D2 B T1 D5 500 D3 T5 Vo D6 300 T4 IUST: Digital IC Design 77/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Advanced Schottky (74ASXX) } Combination Circuit (AND + OR + Inverter) +5 20K 120 8K A T1 T3 D3 B 4K 20K T2 Vo D4 C T5 1.5K D 3K T4 Y = AB + CD IUST: Digital IC Design 78/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 79/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Advanced Low Power Schottky (74ALSXX) } Input transistors do not have to be schottky, because they do not saturate } If we use schottky for them, the area will be large! +5 60K 40K 50W 15K C A 4K B D3 D1 3K Vo 6K D2 Res -, I ¯Þ ALS IUST: Digital IC Design 80/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 81/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Emitter Coupled Logic (ECL) } Current steering rather than transistors to represent logic 0/1 } Extremely high-speed IUST: Digital IC Design 82/129 LECTURE 7 : Logic Families saturating Adib Abrishamifar 2008 ECL } We do not saturate any transistor! + Vcc + Vcc Rc1 Rco Vo2 Vo1 A T2 B T1 To Vref V1 Io VEE IUST: Digital IC Design 83/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 ECL } VTC IC1 é æ Vi - V1 ö ù = IS êexp ç ÷ - 1ú V êë t è ø úû é æ Vref - V1 ö ù ICo = IS êexp ç ÷ - 1ú V t è ø ûú ëê æ Vi - Vref IC1 » exp ç ICo Vt è I aIo ö ÷Þ ø Ic1 æI ö Vi - Vref = Vt Ln ç C1 ÷ è ICo ø IC1 + ICo = aIo Þ IC0 = aI o Ico 1 æ Vi - Vref ö 1 + exp ç ÷ Vt è ø IUST: Digital IC Design 84/129 Vref LECTURE 7 : Logic Families Vin Adib Abrishamifar 2008 ECL IC1 = 100ICo ® Vi - Vref » 100mV Þ To » off , T1 » on From one output ® NOR Gate From other output ® OR Gate 1 (VOH + VOL ) 2 In ECL we need VEE - andVcc ® 0 for noise reduction + Vcc + Vcc Rc1 Rco Vo2 Vo1 A T2 B T1 To V1 For Similarity ® Vref = IUST: Digital IC Design 85/129 LECTURE 7 : Logic Families Vref Io VEE Adib Abrishamifar 2008 ECL } OR + NOR + Vcc R1 270 R2 300 T3 Vo1 (NOR) 2K T4 A R5 50K T1 B T2 To Vref Vo2 V1 50K R3 1.25K R4 (OR) 2K VEE IUST: Digital IC Design 86/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 ECL } Noise Immunity T1, T2 » off Þ Vcc - (Vo1 + VBE ) Vo1 - VEE I B3 = = R1 R5(b + 1) Vcc - VBE VEE + R1 (b + 1)R5 Þ Vo1 = Þ R1 + (b + 1)R5 R1R5(b + 1) + Vcc R1 270 T3 Vo1 (NOR) 2K T4 A 87/129 T1 B T2 To Vref Vo2 V1 R5 50K (b + 1)R5 ì dVo1 = ï dVcc R1 + (b + 1)R5 » 1 ï í R1 R1 ï dVo1 = » ïî dVEE R1 + (b + 1)R5 (b + 1)R5 Þ VEE is noise immune IUST: Digital IC Design R2 300 LECTURE 7 : Logic Families 50K R3 1.25K R4 (OR) 2K VEE Adib Abrishamifar 2008 ECL } Vref Circuit VEE - 2VD K ´ 0.3 = -0.428V K K 2.3 + 0.3 Þ Vref = + VB - 0.75 = -1.14V 1)A, B ® Low, Vcc = 0 Þ Vo1 = -0.75V V1 = Vref - 0.75 = -1.9V 5.2 - 1.9 = 2.64mA IR 3 = K 1.25 VR 2 = -2.64mA ´ 0.3K = -0.792V 300 VB = - VB Vref 2K VEE = -5.2 + Vcc R1 270 88/129 R2 300 T3 T4 A Vo1 (NOR) 2K R5 50K Vo2 = VR 2 - 0.75 = -1.542V IUST: Digital IC Design 2.3K LECTURE 7 : Logic Families T1 B T2 To Vref Vo2 V1 50K R3 1.25K R4 (OR) 2K VEE Adib Abrishamifar 2008 ECL } Vref Circuit 300 VEE - 2VD K VB = ´ 0.3 = -0.428V K K 2.3 + 0.3 Þ Vref = + VB - 0.75 = -1.14V VB Vref 2K 2)A, B ® High(-0.75V), Vcc = 0 Þ Vo2 = -0.75V VEE = -5.2 + Vcc V1 = -0.75V - 0.75V = -1.5V 5.2 - 1.5 = 2.96mA IR 3 = 1.25K VR1 = 2.96mA ´ 0.27 K » 0.8V R1 270 89/129 R2 300 T3 Vo1 (NOR) 2K T4 A R5 50K Vo1 = VR1 - 0.75 = -1.55V IUST: Digital IC Design 2.3K T1 B T2 To Vref Vo2 V1 50K R3 1.25K R4 (OR) 2K VEE LECTURE 7 : Logic Families Adib Abrishamifar 2008 ECL } Symbol and VTC Vo OR A B OR -0.75 NOR + Vcc R1 270 R2 300 T3 Vo1 (NOR) 2K T4 A R5 50K T1 B T2 To Vref V1 50K R3 1.25K R4 Vo2 -1.55 (OR) 2K 90/129 -1.55 -0.75 Vi Vo » -1.71 VEE IUST: Digital IC Design NOR LECTURE 7 : Logic Families Adib Abrishamifar 2008 ECL } VTC } T1 may be saturate if R3 is used VEE - 0.1 Ic1sat = = 3.36mA K K 1.25 + 0.27 Þ Vo1 = -0.8 - 3.36mA ´ 0.27 K Vo1 = -1.71V (Vi = -0.25V) } If Vi is increased more (Vi>-0.25) Vo -0.75 Vo1 = Vi - 1.45 -1.55 -1.55 Vo1 = Vi + VBCT1 + VBET3 Þ Vo1 = Vi - 0.7 - 0.75 (for NOR Gate) IUST: Digital IC Design 91/129 NOR LECTURE 7 : Logic Families -0.75 Vi Vo » -1.71 Adib Abrishamifar 2008 ECL } Speed of OR, NOR ECL Gate } To is in CB configuration therefore OR is faster than NOR + Vcc R1 270 R2 300 T3 T4 A Vo1 (NOR) 2K R5 50K T1 B T2 To Vref V1 50K R3 1.25K R4 Vo2 (OR) 2K VEE IUST: Digital IC Design 92/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 ECL } Pdis + Vcc 1)Input Low I R 3 = 2.64mA R1 270 R2 300 T3 Vo1 (NOR) T4 A T1 B T2 To Vref Vo2 5.2 - 0.75 IR 5 = = 2.225mA R5 5.2 - 1.55 IR 4 = = 1.825mA R4 Pdis = 5.2V (2.64mA + 2.225mA + 1.825mA ) = 34.8mW 2K R5 50K V1 50K R3 1.25K R4 (OR) 2K VEE IUST: Digital IC Design 93/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 ECL } Pdis 2)Input High I R 3 = 2.96mA I R 5 = 1.825mA I R 4 = 2.225mA + Vcc R1 270 R2 300 T3 T4 A Vo1 (NOR) 2K T1 B T2 To Vref V1 R5 50K 50K R3 1.25K R4 Vo2 (OR) 2K VEE Pdis = 5.2V (2.96mA + 1.825mA + 2.225mA ) = 36.4mW 1 Pdis = ( 36.4 + 34.8 ) = 35.6mW 2 IUST: Digital IC Design 94/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 ECL } Pdis (Vref) 5.2 - 1.15 300 I 2K = = 2.025mA VB K Vref 2 2K 5.2 - 1.4 2.3K I 2.3K = 1.46mA = K K VEE = -5.2 2.3 + 0.3 V mA mA Pdisref = 5.2 (2.025 + 1.46 ) = 18.122mW Pdistot = 35.6 IUST: Digital IC Design mW 95/129 + 18.122 mW » 53.7mW LECTURE 7 : Logic Families Adib Abrishamifar 2008 ECL } 10K Typical Characteristics VOH / VOL -0.9 / - 1.7 FO 10 VIH / VIL -1.2 / - 1.4 Supply -5.2V 0.3 / 0.3 PD 24mW 0.8V PDT 2n sec NM H / NM L Logic Swing IUST: Digital IC Design 96/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 ECL } Better ECL (Positive Supply) VOH = 1.7V + Vcc = 1.7 VOL = Vcc - 0.5 Platin Schottky Diode = 1.2V Vref = 1 1.7 V + 1.2V = 1.45V 2 ( Rco Rc1 ) Vo2 Vo1 A T1 B T2 To Vref RE IUST: Digital IC Design 97/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 ECL } 100K Series } In ECL10K series the reference voltage is centered with respect to VOH and VOL even with changes of temperature } However, the Vref and output voltage levels do change with temperature, increasing as temperature increases } In ECL100K series this problem is solved IUST: Digital IC Design 98/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 ECL } 100K Series } D1, D2 and R4 eliminate the curvature in VTC + Vcc = 1.7 Vo Rc1 D1 Rco -0.75 R4 A T1 B D2 To T2 T3 NOR Vref OR D1, D2, R4 eliminate this -1.55 -1.55 R3 -0.75 Vi -VEE(-4.5) IUST: Digital IC Design 99/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 ECL } Combination in ECL } To1, To2 have the same B,C therefore the area is small + Vcc = 1.7 A+B A T1 B C+D (A + B)(C + D) T2 To1 Vref To2 C D RE IUST: Digital IC Design 100/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 101/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Merged Transistor Logic } Minimal TTL Implementation to Reduce Number of Passive, Power Dissipating Components } Integrated Injection Logic: I2L } Multiple collector NPN bipolar transistors } Can be “wire-or’d” to create all logic functions IUST: Digital IC Design 102/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 I2L , MTL } I2L=Integrate Injection Logic (Phillips) } MTL=Merged Transistor Logic I Pdif I N - epi C1 C2 C3 C1 C2 C3 Pdif N - epi N N+ N+ N+ + I C1 C2 C3 E IUST: Digital IC Design 103/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 I2L , MTL } } } } Vertical NPN is not suitable because Collector N+ Base Large Emitter N-epi Pdif I C1 C2 C3 Pdif N - epi N+ N+ N+ N+ E IUST: Digital IC Design 104/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 I2L , MTL } NM 0.9V £ Vcc £ 15V I VOH = VOH = 0.8V VOL = 0.1V VOL = 0.2V bmin = is equal to no output collectors (for 5 outputs β min =5) VIH = 0.7V N - epi C1 C2 C3 VIL = 0.5V NML = VIL - VOL = 0.5V - 0.2V = 0.3V NMH = VOH - VIH = 0.8V - 0.7 V = 0.1V IUST: Digital IC Design 105/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 I2L , MTL } Advantages: } Digital + Analog } PDP is close to CMOS } Small area Collectors Base I IUST: Digital IC Design 106/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 I2L , MTL } I2L NOR A+B I A I B IUST: Digital IC Design 107/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 I2L , MTL } I2L NAND I AB A B IUST: Digital IC Design 108/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 I2L , MTL } I2L FF } The largest time constant is belong to Emitter (Emitter area is very large and delay is equal to time which need charge Emitter-Base cap. with I) S Q I S I Q Q R Q R IUST: Digital IC Design 109/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 I2L , MTL } Better I2L } N1+ is used in 3 sides (except left) } N1+ ® Increase Injection in Vertical ® b } We can not use schottky because we need N in collector } I2L is slower than ECL by approximately 5 I epi P N P C1 C2 N+ N+ N1+ N+ E IUST: Digital IC Design 110/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 I2L , MTL } Delay Power P = IV » IVBE , VCEsatPNP » 0 ® Vcc » VBE Q = CVBE C 2 = It Þ t = VBE ® Pt d = CVBE = Cte I td } From this point the Excess current is large then in delay calculation, the storage time must be calculated P1 IUST: Digital IC Design P 111/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 I2L , MTL } Faster I2L } If we change ΔVBE to a lower value the Gate become faster } By a Schottky on collector of T1, ΔVBE=0.7-0.5=0.2V } This reduces NM C1 C2 T1 T2 IUST: Digital IC Design 112/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 I2L , MTL } Faster I2L B I C1 N + P C2 T1 T2 IUST: Digital IC Design 113/129 LECTURE 7 : Logic Families N-Implant P P - N+ N - epi N+ Adib Abrishamifar 2008 I2L , MTL } Faster I2L (Other Idea) } Schottky is used for T2 } We have Large VCEsat and then it is very difficult to design a Gate , because VD + VCEsat not to be reached to VBE(0.7) } The Metal for schottky will be very important for reduction of barrier potential, usually the mixture of Si and Pt is used IUST: Digital IC Design 114/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 115/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } Schottky Transistor Logic (STL) } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Schottky Transistor Logic (STL) T1 T2 IUST: Digital IC Design 116/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 117/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Integrated Schottky Logic (ISL) } We use resistor for PNP } Only in this configuration the Emitter junction is on the top C1 R T1 VCBT1sat = 0.7V C2 VEBT 2 = 0.6V < VCBT1 T2 IUST: Digital IC Design 118/129 C¢2 ì PNP ® Prevents NPN to saturate ü Þí ý Þ Higher Speed î NPN ® Prevents PNP to saturate þ LECTURE 7 : Logic Families Adib Abrishamifar 2008 ISL } N+1 is used for lowering the ohmic junction of collector } It covers the large area of Base Then bPNP ¯ C1 R B Poly R C2 T1 T2 IUST: Digital IC Design 119/129 P C¢2 LECTURE 7 : Logic Families E C1 C2 N+ N-epi P N1+ C¢2 Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 120/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Compatibility of Logic Families } Common ground, common supply voltage, and TTL input and output levels } Common ground, common supply voltage, CMOS inputs, and TTL outputs } Common ground, common supply voltage, TTL inputs, and CMOS outputs } Common ground, different Supply voltage levels } Dynamic interface issues IUST: Digital IC Design 121/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Compatibility of Logic Families } Common GND, Different Supply Voltage } Low-voltage device for interface to TTL level I/O 5V logic devices • Low voltage BiCMOS LVT, CMOS LVC, LVQ, FCT3, etc } Cautions • 3.3V to 5V logic interface – In general, no problem • 5V to 3.3V logic interface – Must have no an electrostatic protection network (a diode or diodes) at the inputs of 3.3V devices to prevent excessive current IUST: Digital IC Design 122/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Compatibility of Logic Families } Dynamic Interface Issues } When logic families are mixed • Dynamic and static interface compatibility • Timing problem by mixing slow and fast devices – Holding time violation by fast-edge to slow-edge logic interface » In synchronous systems, signals originating from fast devices may go away before they can be captured by slow devices IUST: Digital IC Design 123/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 124/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Noise Margins of Logic Families } What is the Noise margin? } Difference between the worst-case output levels and the worst-case input levels } Static and Dynamic noise margins } Static noise margin: low-frequency safety margins } Dynamic noise margin: sensitivity of logic devices to noise spikes • It is less than that of older logic families because of designing for high-speed operation IUST: Digital IC Design 125/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Noise Margins of Logic Families } Static Noise margin Family ABT AC ACT AC11 ACT11 ALS AS FAST FCT FCT3 BC BCT LVQ LVT IUST: Digital IC Design Input levels, V VIL MAX VIH MIN 0.8 2.0 1.35 3.15 0.8 2.0 1.35 3.15 0.8 2.0 0.8 2.0 0.8 2.0 0.8 2.0 0.8 2.0 0.8 2.0 0.8 2.0 0.8 2.0 0.8 2.0 0.8 2.0 126/129 LECTURE 7 : Logic Families Output levels, V VOL MAX VOL MIN 0.55 2.5 0.1 4.4 0.5 3.7 0.1 4.4 0.5 3.7 0.5 2.4 0.55 2.4 0.55 2.4 0.55 2.4 0.5 2.4 0.5 2.5 0.55 2.4 0.5 2.4 0.5 2.4 Adib Abrishamifar 2008 Noise Margins of Logic Families } Dynamic Noise margin } Low state pulse rejection characteristic of IDT FCT244 PULSE AMPLITUDE (v) 4 3 HAZARD 2 SAFE 1 0 1 2 3 4 5 6 7 8 9 10 11 PULSE WIDTH (ns) IUST: Digital IC Design 127/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008 Contents } Logic Families on a Glance } Diode Logic (DL) } Resistor Transistor Logic (RTL) } Diode Transistor Logic (DTL) } Modified DTL (NAND) } Transistor Transistor Logic (TTL) } Standard TTL } High Speed TTL (74HXX) } Tri-State Logic } Storage Delay Time } Schottky TTL (74SXX) } Low Power Schottky Clamped TTL (74LSXX) IUST: Digital IC Design 128/129 } Advanced Schottky (74ASXX) } Advanced Low Power Schottky (74ALSXX) } Emitter Coupled Logic (ECL) } I2L , MTL } STL } Integrated Schottky Logic (ISL) } Compatibility of Logic Families } Noise Margins of Logic Families } Summary LECTURE 7 : Logic Families Adib Abrishamifar 2008 Summary } In this lecture the development of Digital IC specially bipolar gate circuit is described. Specially described in detail are: } RTL } DTL } TTL including: • • • • • } } } } Standard TTL Schottky Clamped (S) Low Power Schottky (LS) Advanced Schottky (AS) Advanced Low Power Schottky (ALS) ECL I2 L STL ISL IUST: Digital IC Design 129/129 LECTURE 7 : Logic Families Adib Abrishamifar 2008