Functional NEMS

advertisement

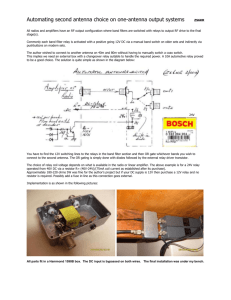

Realizing Energy-Efficient Integrated Circuits with NEM Relays Elad Alon (UC Berkeley) in collaboration with Tsu-Jae King Liu (UC Berkeley), Vladimir Stojanovic (MIT), Dejan Marković (UCLA), Chanro Park, Rinus Lee, Wei-Yip Loh (SEMATECH) Digital Computing Power Crisis Power Density Prediction circa 2000 Power Density (W/cm2) 10000 100 Nuclear Reactor 8086 Hot Plate 10 4004 P6 8008 8085 Pentium® proc 386 286 486 8080 1 1970 1980 1990 2000 2010 Year S. Borkar Since ~2000 supply voltages (VDD) stuck at ~1V 1000 Sun’s Surface Rocket Nozzle Leakage stops you from lowering threshold (VT) Leads to very poor power scaling… 1kW chips? 2 Parallelism to the Rescue Parallelism allows slower, more efficient cores While maintaining overall throughput Works well (if you can parallel program), but… 3 Leakage: Game Over for CMOS CMOS circuits have an absolute minimum energy Need to balance leakage and dynamic components Parallelism doesn’t help if already at Emin… 4 NEM Relays: The Next Savior? Measured MEM Relay I-V Curve MEM Relay Energy vs. VDD Etotal=Edynamic Mechanical relays don’t leak, turn on abruptly Potential pathway to continued energy scaling Relay Emin: ~1aJ (>10X better than 65nm CMOS) Device/circuit co-design critical R. Nathanael et al., “4-Terminal Relay Technology for Complementary Logic,” IEDM 2009 5 Relay Structure and Operation Poly-SiGe Tungsten OFF: |Vgb| < Vpo (pull-out) ON: |Vgb| > Vpi (pull-in) 6 NEM Relay as a Logic Element Gate Source Mimics operation of CMOS transistors Body Drain Electrostatic actuation is ambipolar Unlike CMOS, non-inverting logic is possible Switch state set only by gate-to-body voltage 7 Digital Circuit Design with NEM Relays NEMS: 12 switches CMOS: delay set by electrical time constant Cascade simple gates to distribute fanout Relays: delay dominated by mechanical movement So, want all to switch simultaneously Æ Implement logic as a single complex gate (1930’s) 8 Need to Compare at Block Level NEMS: 12 relays 4 gate delays Single mechanical delay per block 1 mechanical delay Substantially mitigates perceived delay disadvantage Often fewer devices for same function Comparable area despite larger individual devices F. Chen et al., “Integrated Circuit Design with NEM Relays,” ICCAD 2008 9 Example: 32-bit Relay Adder Ripple carry configuration Cascade full adder cells to create larger complex gate Stack of 32 relays, still a single mechanical delay 10 Scaled Relay vs. CMOS Adders Vd d 1V : Æ 0 .5 V Vd 0.9 d: V Æ 0.3 2 9x 10x * V Compare vs. CMOS adder* in 90nm technology For similar area: >9x lower E/op >10x greater delay D. Patil et al., “Robust Energy-Efficient Adder Topologies,” ARITH 2007 11 Parallelism Can extend energy benefit up to GOPS throughput As long as parallelism is available 12 Contact Resistance Low contact R not critical Good news for reliability… 13 Relay Contact Reliability Contact resistance [Ω] 1.E+06 100kΩ specification 1.E+05 1.E+04 1.E+03 L=25µm Measured in ambient 1.E+02 1.E+0 1.E+3 1.E+6 1.E+9 No. of on/off cycles Higher contact R, hard contact (W) improves reliability Limits power dissipation, material flow Current endurance record: 65 billion cycles Theory/experiments predict >1015 cycles @ 1V VDD H. Kam et al., IEDM 2010 14 Circuit Demonstration Platform 9mm Test Devices 8-bit adders 4-bit and 2-bit adders 2-bit accumulator SRAM Flip-flops DRAMs 7:3 Compressor 4-bit DAC Oscillators 4-bit ADCs 4-bit DAC Oscillators F. Chen et al., ISSCC 2010 , M. Spencer et al., JSSC, Jan. 2011 15 Relay VLSI Design Infrastructure Verilog-A Model Logic Synthesis Place & Route Verilog-A model & Logic Synthesis customized for relays Flow supports multiple device designs and foundries 16 Looking Forward: Need Advanced Materials Relay with Ru/RuO2 contacts 100kΩ specification 1.E+05 1.E-02 1.E-03 Contact Instability 1.E-04 1.E-05 1.E-06 1.E+04 1.E+03 ID (A) Contact resistance [Ω] 1.E+06 L=25µm 1.E-08 1.E-09 1.E-10 1.E-11 Measured in ambient 1.E+02 1.E+0 1.E+3 1.E+6 1.E+9 No. of on/off cycles 1.E-07 1.E-12 1.E-13 1.E-14 0 2 4 6 8 10 12 VG (V) Advanced materials crucial to solving remaining technology challenges E.g., W contacts unstable due to oxidation Sematech enabling exploration of Ru/RuO2 contacts 17 Scaling Back to The Future? 1 µm litho (UCB) 0.25 µm litho (Sematech) 120µm x 150µm 20µm x 20µm 18 Conclusions Relay characteristics enable energy scaling beyond CMOS Nearly ideal Ion/Ioff Need to adapt circuit design style Reliability improving Circuit level insights critical (contact R) Demonstrated simple, operational circuits Potential for 10X or more lower E/op than CMOS Scaling, advanced materials critical Next step: >10k relay µC demo with scaled devices 19 Acknowledgements Circuit design Matthew Spencer, Patrick Kwong, Abhinav Gupta Fred Chen, Hossein Fariborzi Chengcheng Wang, Kevin Dwan Device design Philip Chen, Louis Hutin, Jaeseok Jeon, Hei Kam, Rhesa Nathanael, Vincent Pott Sponsors DARPA NEMS program FCRP (C2S2, MSD) Berkeley Wireless Research Center MIT CICS NSF 20