Design Entry with the Schematic

advertisement

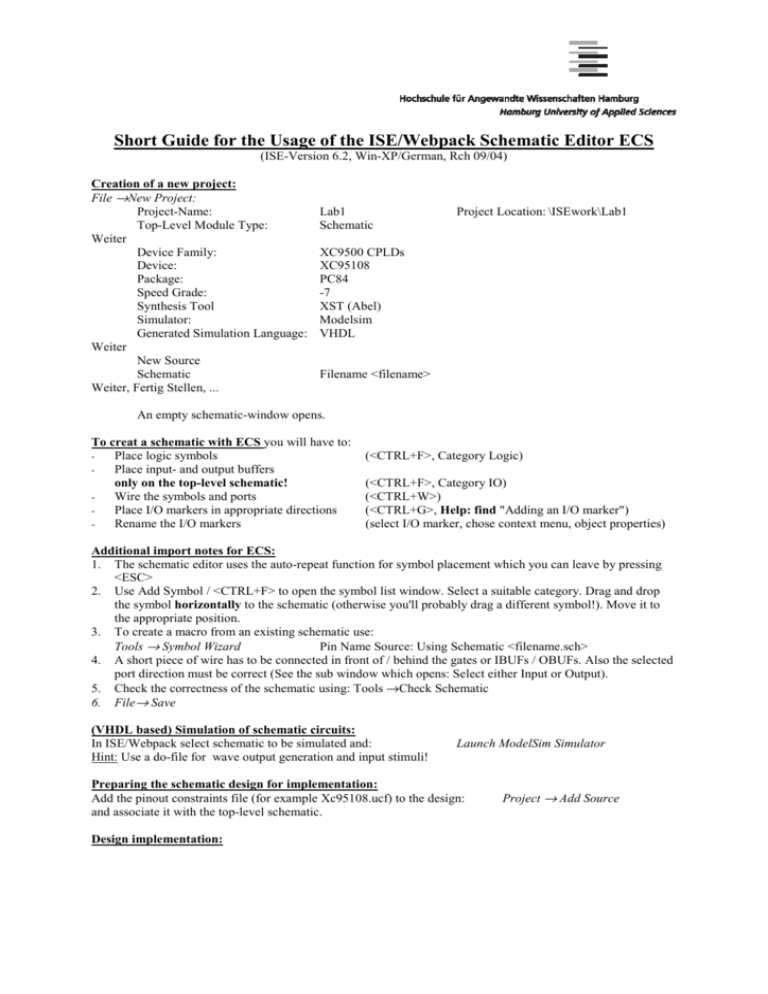

Short Guide for the Usage of the ISE/Webpack Schematic Editor ECS (ISE-Version 6.2, Win-XP/German, Rch 09/04) Creation of a new project: File →New Project: Project-Name: Top-Level Module Type: Weiter Device Family: Device: Package: Speed Grade: Synthesis Tool Simulator: Generated Simulation Language: Weiter New Source Schematic Weiter, Fertig Stellen, ... Lab1 Schematic Project Location: \ISEwork\Lab1 XC9500 CPLDs XC95108 PC84 -7 XST (Abel) Modelsim VHDL Filename <filename> An empty schematic-window opens. To creat a schematic with ECS you will have to: Place logic symbols Place input- and output buffers only on the top-level schematic! Wire the symbols and ports Place I/O markers in appropriate directions Rename the I/O markers - (<CTRL+F>, Category Logic) (<CTRL+F>, Category IO) (<CTRL+W>) (<CTRL+G>, Help: find "Adding an I/O marker") (select I/O marker, chose context menu, object properties) Additional import notes for ECS: 1. The schematic editor uses the auto-repeat function for symbol placement which you can leave by pressing <ESC> 2. Use Add Symbol / <CTRL+F> to open the symbol list window. Select a suitable category. Drag and drop the symbol horizontally to the schematic (otherwise you'll probably drag a different symbol!). Move it to the appropriate position. 3. To create a macro from an existing schematic use: Tools → Symbol Wizard Pin Name Source: Using Schematic <filename.sch> 4. A short piece of wire has to be connected in front of / behind the gates or IBUFs / OBUFs. Also the selected port direction must be correct (See the sub window which opens: Select either Input or Output). 5. Check the correctness of the schematic using: Tools →Check Schematic 6. File→ Save (VHDL based) Simulation of schematic circuits: In ISE/Webpack select schematic to be simulated and: Hint: Use a do-file for wave output generation and input stimuli! Launch ModelSim Simulator Preparing the schematic design for implementation: Add the pinout constraints file (for example Xc95108.ucf) to the design: and associate it with the top-level schematic. Design implementation: Project → Add Source