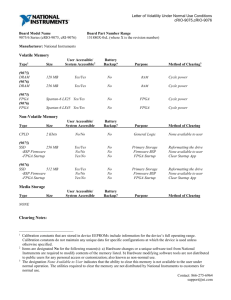

Spartan-6 FPGA SelectIO Resources User Guide (UG381)

advertisement