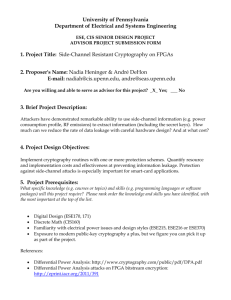

Implementation of SCA-Resistant CPU and an ECDLP Engine on

advertisement