VLSI

advertisement

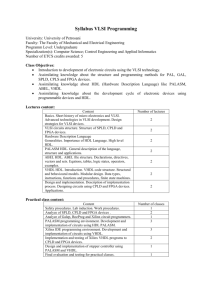

VLSI TECHNOLOGY : VLSI DOMAIN : IEEE TRANSACTIONS ON CORE VLSI S.NO 1 CODE VLSI001 PROJECT TITLE YEAR A NOVEL CARRY-LOOK AHEAD APPROACH TO AN UNIFIED BCD AND 2008 BINARY ADDER/SUBTRACTOR 2 VLSI002 SPECULATIVE CARRY GENERATION WITH PREFIX ADDER USING VHDL / 2008 VERILOG 3 VLSI003 HIGHER RADIX AND REDUNDANCY FACTOR FOR FLOATING POINT SRT 2008 DIVISION USING VHDL / VERILOG 4 VLSI004 AREA-EFFICIENT ARITHMETIC EXPRESSION EVALUATION USING 2008 DEEPLY PIPELINED FLOATING POINT CORES USING VHDL 5 VLSI005 IMPROVING ERROR TOLERANCE FOR MULTITHREADED 2008 REGISTER FILES 6 VLSI006 REGISTER FOR PHASE DIFFERENCE BASED LOGIC 2007 7 VLSI007 DESIGNING EFFICIENT ONLINE TESTABLE REVERSIBLE ADDER WITH 2007 NEW REVERSABLE GATE 8 VLSI008 NOVEL BCD ADDERS AND THEIR REVERSIBLE LOGIC IMPLEMENTATION 2006 FOR IEEE 754R FORMAT 9 VLSI009 HIGH SPEED RECURSION ARCHITECTURE FOR MAP- BASED TURBO 2007 DECODERS 10 VLSI010 CONCURRENT ERROR DETECTION IN REED SOLOMON ENCODERS AND 2007 DECODERS TECHNOLOGY : VLSI DOMAIN : : IEEE TRANSACTIONS ON LOW POWER AND FPGA S.NO CODE PROJECT TITLE 1 VLSI011 LOW POWER YEAR DESIGN OF PRECOMPUTATION-BASED CONTENT- 2008 L-CBF: A LOW-POWER, FAST COUNTING BLOOM FILTER ARCHITECTURE 2008 ADDRESSABLE MEMORY USING VHDL / VERILOG 2 VLSI012 USING VHDL 3 VLSI013 LOW-POWER LEADING-ZERO COUNTING AND ANTICIPATION LOGIC FOR 2008 HIGH-SPEED FLOATING POINT UNITS 4 5 VLSI014 FPGA IMPLEMENTATION OF LOW POWER PARALLEL MULTIPLIER 2007 VLSI015 LOW 2007 POWER MULTIPLIER WITH SUPERIOUS POWER SUPRESSION TECHNIQUE 6 VLSI016 SHIFT INVERT CODING FOR LOW POWER VLSI 2004 TECHNOLOGY : VLSI DOMAIN :IEEE TRANSACTIONS ON IMAGE PROCESSING S.NO 1 CODE PROJECT TITLE YEAR VLSI017 LOW POWER HARDWARE ARCHITECTURE FOR VBSME USING PIXEL 2008 TRUNCATION USING VHDL 2 VLSI018 A MODELING OF A DYNAMICALLY RECONFIGURABLE PROCESSOR USING 2008 VHDL 3 VLSI019 A PROCESSOR IN MEMORY ARCHITECTURE FOR MULTIMEDIA 2007 COMPRESSION 4 VLSI020 A VLSI PROGRESSIVE CODING FOR WAVELET BASED IMAGE COMPRESSION 2007 5 VLSI021 SHIFT REGISTER BASED DATA TRANSPOSITION FOR COST EFFECTIVE 2007 DISCRETE COSINE TRANSFORM TECHNOLOGY: VLSI DOMAIN: SECURITY AND COMMUNICATIONS S.NO CODE PROJECT TITLES 1 VLSI022 FPGA IMPLEMENTATION(S) OF A SCALABLE ENCRYPTION ALGORITHM YEAR 2008 USING VHDL 2 VLSI023 DESIGN AND IMPLEMENTATION OF AES USING VHDL 2008 3 VLSI024 COST-EFFICIENT SHA HARDWARE ACCELERATORS 2008 4 VLSI025 EFFECTIVE USES OF FPGAS FOR BRUTE-FORCE ATTACK ON RC4 2008 CIPHERS 5 VLSI 26 DESIGN OF REVERSIBLE FINITE FIELD ARITHMETIC 2008 CIRCUITS WITH ERROR DETECTION 6 VLSI027 A ROBUST UART ARCHITECTURE BASED ON RECURSIVE RUNNING SUM FILTER FOR BETTER NOISE PERFORMANCE 2007 7 VLSI028 COMPACT HARDWAE DESIGN OF WHIRLPOOL HASHING CORE 2006 8 VLSI029 DIGITAL DESIGN OF DS-CDMA TRANSMITTER USING VHDL AND FPGA 2006 9 VLSI030 REAL TIME ADAPTIVE SPEECH WATERMARKING SCHEME FOR MOBILE 2003 APPLICATIONS 10 VLSI031 A LIGHTWEIGHT ENCRYPTION METHOD SUITABLE FOR COPYRIGHT 1998 PROTECTION TECHNOLOGY:VLSI DOMAIN:NON IEEE /APPLICATION S.NO CODE PROJECT TITLE 1 VLSIN001 RTL DESIGN AND SIMULATION OF MICRO CONTROLLER IN HDL 2 VLSIN002 HDL IMPLEMENTATION OF ERROR DETECTION AND CORRECTION CIRCUIT 3 VLSIN003 DAQ SYSTEM 4 VLSIN004 DESIGN AND IMPLEMENTATION OF DIRECT DIGITAL SYNTHESIZERS FOR WIRELESS APPLICATIONS 5 VLSIN005 MULTI LEVEL SECURITY SYSTEM