DOC - Cryptographic Engineering Research Group

advertisement

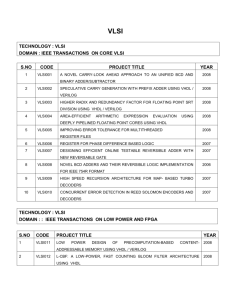

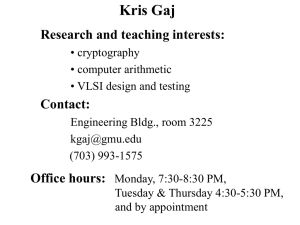

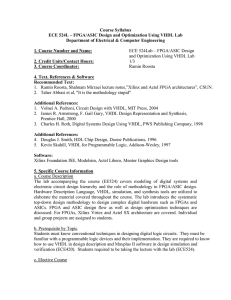

Yamini Ravishankar 9411 Lee Highway Apt-1011, Fairfax, VA- 22031 yravisha@gmu.edu • yaminiravishankar@gmail.com • 703-731-6302 EDUCATION Master of Science, Electrical Engineering, George Mason University , Fairfax, VA Expected Graduation May 2014 Member, Cryptographic Engineering Research Group (CERG), Volgenau School of Engineering Courses completed : Microprocessors , Digital System Design w/ VHDL, Cryptography and Network Security Courses I intend to take : Computer Arithmetic, Advanced Applied Cryptography, Digital Integrated Circuits, VLSI Design for ASICs, VLSI Test Concepts Bachelor of Technology (B.Tech (Hons.)), Electronics and Communication Engineering May 2012 SASTRA University, Thanjavur, India Cumulative GPA – 9.17/10 Recipient of the Lord Vignesh award (best outgoing student) and Shri Ambarish award (best outstanding student) of the ECE Department, SASTRA University (Class of 2012) Dean’s Lister (Top 10% in University) for the academic year 2010-2011 Dean’s Lister (Top 2% in University) for the academic year 2008-2009 Published a paper titled “Random & AWGN road for MC-CDMA bus to Phase Hide – A MUX in MUX Stego” WORK EXPERIENCE August 2012 - Present Lab Assistant, Electrical and Computer Engineering Department, George Mason University Maintenance of the hardware laboratory equipment including the trainer kits, digital multimeters, oscilloscopes. Software installations and troubleshooting in the ECE labs TECHNICAL SKILLS Programmable Hardware Programming Languages Scripting Language Hardware Languages Tools Altera FPGA and Xilinx FPGA C, C++, Matlab Python VHDL, Assembly coding ModelSim, Xilinx ISE, Altera Quartus, Code Composer Studio, Keil uVision3, GnuPG, Cryptool, LogiCube Logic Analyzer AREAS OF INTEREST VLSI design and architecture, Processor Architecture, Hardware implementations of Cryptographic Algorithms, Memory testing PROJECT WORK Evaluation of Physical Unclonable Functions Fall 2012 Comparison of the PUF models proposed by the research team of George Mason University and Virginia Tech based on metrics – Uniqueness, Uniformity, Reliability, Steadiness and Bit-Aliasing under the guidance of Dr.Kris Gaj Implementation of a Hash-CFB based on Keccac Fall 2012 Hardware implementation of the Hash-CFB based on SHA-3 Keccac with the optimization target of maximum Throughput/ Area ratio using VHDL Digital IC Tester Fall 2012 Term project implemented using MSP430 offering a cost-effective circuit for testing simple ICs Method and Apparatus for On-Chip and Off-Chip Memory December 2012 - April 2012 testing of Cyclone FPGAs Proposed a simple BIST architecture for testing the SRAM and the Internal M4K blocks of Cyclone II FPGAs in the Altera DE1 kit using VHDL programming CO-CURRICULAR ACTIVITIES Proof-read the book titled Cloud Enterprise Architecture by Dr. Pethuru Raj, Wipro Technologies and several scholarly papers of Professors at SASTRA University published in IEEE, Science Direct, International Journal of Computer Applications Head of the Editorial Board of the ECE Department Association responsible for publication of monthly newsletter and “CEPSTRUM”, an internal academic magazine