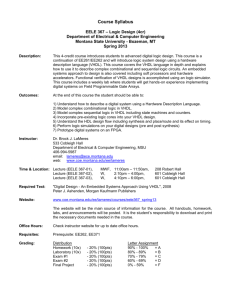

Tutorial on VHDL Compilation, Simulation, and Synthesis

advertisement

Tutorial on VHDL Compilation, Simulation, and Synthesis

USING MENTOR GRAPHICS

INTRODUCTION

This tutorial is designed to give Mentor Graphics users an experience of how to create a VHDL model,

compile it for simulation, simulate it and verify the model is functional, and synthesize the model to

generate corresponding hardware. It is assumed that the user is familiar with Design Architect and has

entered at least one digital schematic and simulated using QuickSim II.

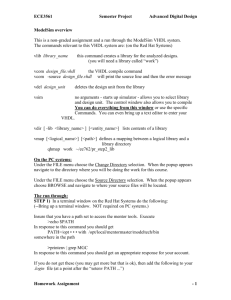

CREATING AND COMPILING A VHDL MODEL USING DESIGN ARCHITECT

Before you start using VHDL compiler, you need to create a working library to store all your designs for

future reference. This can be done by issuing the following command at the prompt:

voyagerx> cd \

voyagerx> cd mentor

voyagerx> qhlib work

This will create a directory called work with a file _info in your mentor directory. All your compiled

designs will be stored here. If you want to use your designs in future VHDL programs you can access them

by adding the following line in your VHDL program.

Use work.all

1. Invoke Design Architect by issuing the following command at the prompt,

voyager{User}: da

This opens up the Design Architect window.

2. Once you are in Design Architect click on the Open VHDL icon. This opens up a dialog box

prompting you to enter the name of the design. Enter the design name, my4bit_full_adder in the

VHDL source box and execute the dialog box.

3. If you are opening a new file, an empty VHDL editor window is opened. Start entering your VHDL

code in this window. As you start typing, the line numbers are created automatically. A 4-bit FullAdder example is given below:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY my_full_vhdl IS

PORT(

a: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

b: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

cin: IN STD_LOGIC;

sum: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

cout : OUT STD_LOGIC

);

END my_full_vhdl;

architecture behavior of my_full_vhdl is

begin

P1:process(a,b,cin)

variable c: STD_LOGIC_VECTOR(4 DOWNTO 0);

begin

c(0) := cin;

for j in 0 to 3 loop

sum(j)<=(a(j) xor b(j) xor c(j));

c(j+1):=(a(j) and b(j)) or (a(j) and c(j)) or (b(j) and c(j));

end loop;

cout<=c(4);

end process P1;

end behavior;

4. After you finish typing, save the file by choosing the File à Save pull-down menu.

5. To compile the model you have just created choose: Compileà

à Set options from pull-down menu.

This opens up a dialog box to choose options for the compilation.

6. In the Work Library box enter the name of your working library. If your working library is named

work type work here after mentor. Select VHDL 93 as QuickHDL option and Simulation as the

purpose. Click on Just for Conditional Compilation and only choose Entity and Architecture. Press

OK to close the box.

7. Now choose Compileà

à Compile either from the pull-down menu or click on Compile option in the

right side palette. A compilation report is generated. If there are any errors in compilation, fix the

problem. Once the compilation is successful, as indicated by the following output, entity and

architecture files will be created in mentor/work directory.

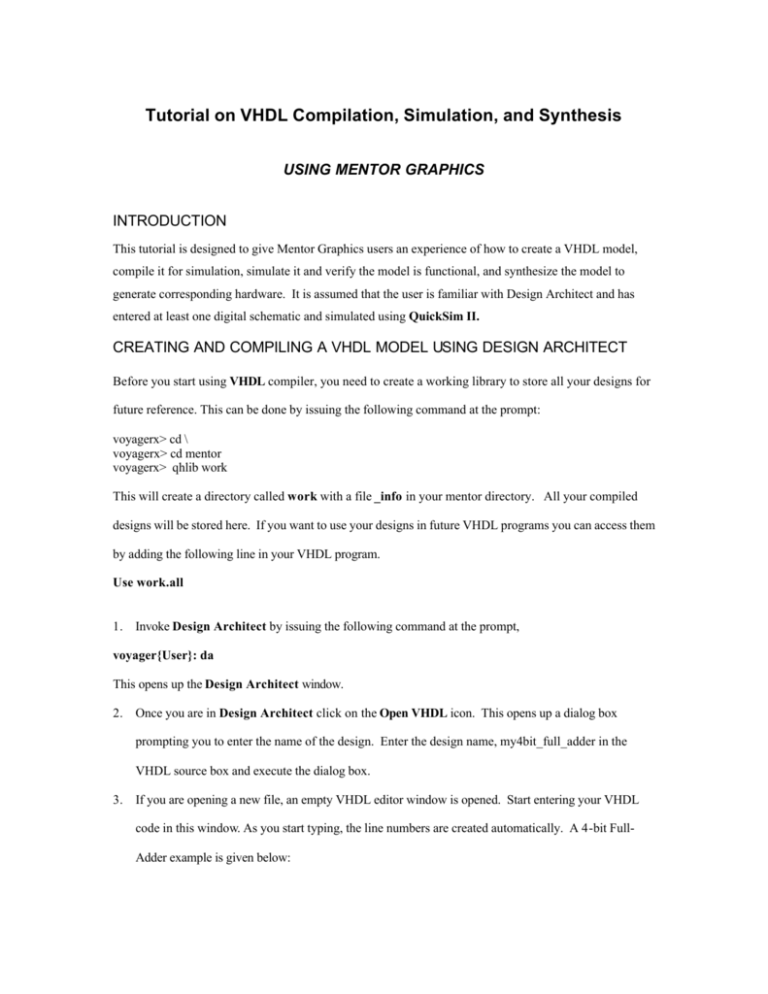

SIMULATING THE VHDL MODEL USING QHSIM FROM DESIGN ARCHITECT

You need to simulate the design and verify the correctness of the model before you synthesize it for

hardware realization.

1. Click the mouse pointer anywhere in the design architect window. Now, the design architect window

is selected. The VHDL editor window will be deselected.

2. Select the QuickVHDL à qhsim option from the pull-down menu.

3. This opens up a Startup selection box as shown below. Type work in the Library path so your path

should look like <your home directory>/mentor/work. In that library, my_full_vhdl will be shown in

the entity field and behavior will be displayed in architecture field as shown below. Select those

entries and click on Load button.

5. A small window by the name qhsim.mod is opened with the QHSIM 1 prompt.

6. Type view * at the prompt and seven different windows will be opened.

7. Click on the Signals window and select Wave à Signals in the region.

8. All the signals appear in the Wave window. For this tutorial, the signal names displayed would be: a,

b, cin, sum, cout. Note that all the signals are undefined as indicated by U.

9. Go to the qhsim.mod window and type force a 1111 at the QHSIM prompt. Press return. Also type

force b 1100 and force cin 0 at this prompt.

10. Type run at the QHSIM prompt. The simulation will run for 100ns(default) and stops. The

waveforms will be displayed in the wave window. Check the simulation results and confirm that your

design works correctly.

1. If you want the simulation to run for more than 100ns then specify the time at the command; for

example, run 300 to run for 300ns. Now change the forces by typing following commands.

Force a 1101

Force b 0001

Force cin 0

And then simulate for additional 100 ns by typing command run 100. You will see that cout changes to 0

and sum to 1110 as shown below.

11. After simulating the design quit the simulator by typing quit -f at the QHSIM command prompt.

2. ***********To define a clock with 50% duty cycle use the following commands:

force clock 1- repeat 100

force clock 0 50 - repeat 100

Where clock is the name of the clock node in your design. The two commands above should be given in

succession. The first command schedules a one to appear on the clock node when the simulation starts. The

second command forces it to zero after time 50ns. Thus a clock with value 1 for first 50ns and value 0 for

second 50ns is formed with a clock period 100ns. Examples: To define a clock with 25% duty cycle

force clock 1 -repeat 100

force clock 0 25 -repeat 100

To define a clock with 75% duty cycle

force clock 1 -repeat 100

force clock 0 75 -repeat 100

Synthesis

The VHDL synthesis may be performed by AUTOLOGIC II software. Before you invoke the program,

you need to setup some variables. Follow the steps listed below to ensure the functionality of the program.

1. Make sure that you are in mentor directory. If not, then change your directory to mentor.

2. Issue following command to create new HDL design library where the compiled and synthesized

model will reside.

allib adder_models

3. Next create a map file by typing following command. It will create a mapping file called autologic.ini

in the current directory, mentor.

almap adder_models "/user3/home/ppatel/mentor/adder_models"

where /user3/home/ppatel/ should be replaced with your home-directory path.

4. Now, you will compile your vhdl model. Make sure that the source file name has the extension of vhdl

(if not, then use: mv orig_filename my4bit_full_adder.vhdl). Compile the source file by,

alcom my4bit_full_adder.vhdl -work adder_models -nosynchk

Once the compilation is successful, you will invoke the autologic program (in a batch mode) by typing

following multi-line command:

alui –nodisplay –t cmosn <<!

opn design my4bit_full_adder.vhdl

opt area

sav design –eddm –map work eddm –schematic

quit –f

!

This opens autologic II window in a batch mode, opens the design named my4bit_full_adder.vhdl,

synthesizes it, optimizes for the area, and saves the synthesized design in schematic form in eddm

directory. The design can be opened using cmosn_da program in the eddm/my_full_vhdl directory. It can

also be simulated using cmosn_quicksim program.