nanowire diameter

advertisement

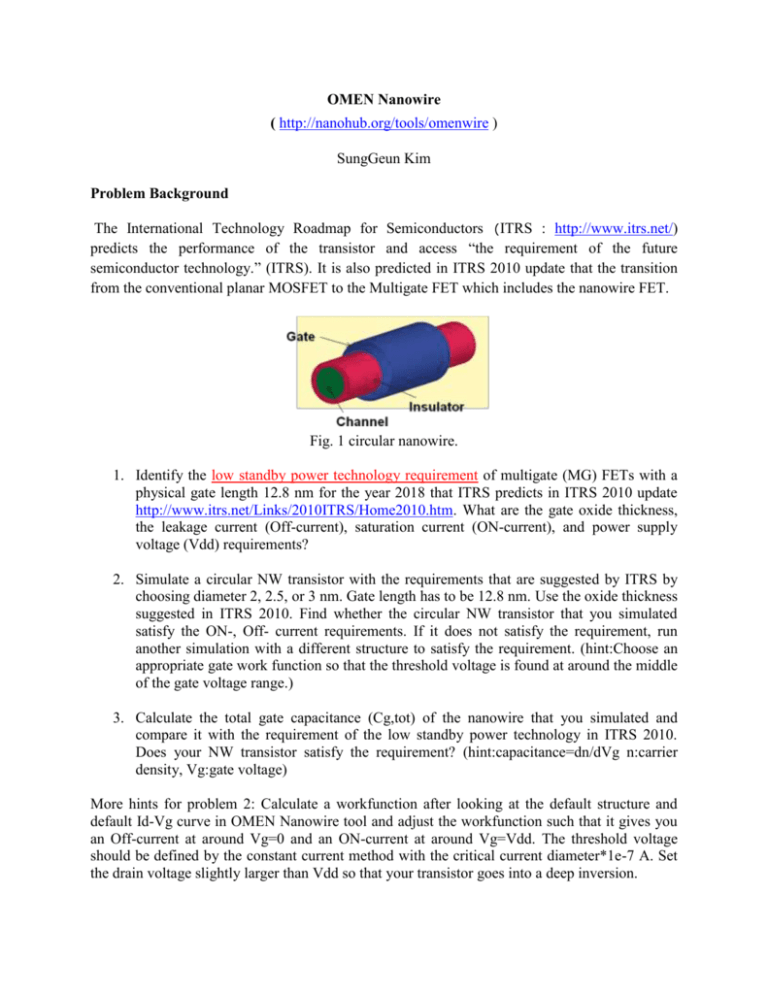

OMEN Nanowire ( http://nanohub.org/tools/omenwire ) SungGeun Kim Problem Background The International Technology Roadmap for Semiconductors (ITRS : http://www.itrs.net/) predicts the performance of the transistor and access “the requirement of the future semiconductor technology.” (ITRS). It is also predicted in ITRS 2010 update that the transition from the conventional planar MOSFET to the Multigate FET which includes the nanowire FET. Fig. 1 circular nanowire. 1. Identify the low standby power technology requirement of multigate (MG) FETs with a physical gate length 12.8 nm for the year 2018 that ITRS predicts in ITRS 2010 update http://www.itrs.net/Links/2010ITRS/Home2010.htm. What are the gate oxide thickness, the leakage current (Off-current), saturation current (ON-current), and power supply voltage (Vdd) requirements? 2. Simulate a circular NW transistor with the requirements that are suggested by ITRS by choosing diameter 2, 2.5, or 3 nm. Gate length has to be 12.8 nm. Use the oxide thickness suggested in ITRS 2010. Find whether the circular NW transistor that you simulated satisfy the ON-, Off- current requirements. If it does not satisfy the requirement, run another simulation with a different structure to satisfy the requirement. (hint:Choose an appropriate gate work function so that the threshold voltage is found at around the middle of the gate voltage range.) 3. Calculate the total gate capacitance (Cg,tot) of the nanowire that you simulated and compare it with the requirement of the low standby power technology in ITRS 2010. Does your NW transistor satisfy the requirement? (hint:capacitance=dn/dVg n:carrier density, Vg:gate voltage) More hints for problem 2: Calculate a workfunction after looking at the default structure and default Id-Vg curve in OMEN Nanowire tool and adjust the workfunction such that it gives you an Off-current at around Vg=0 and an ON-current at around Vg=Vdd. The threshold voltage should be defined by the constant current method with the critical current diameter*1e-7 A. Set the drain voltage slightly larger than Vdd so that your transistor goes into a deep inversion.