2000 S1 - Massey University

advertisement

CP

2000/159.203

Alb

MASSEY UNIVERSITY

ALBANY CAMPUS

EXAMINATION FOR 159.203 COMPUTER SYSTEMS

Semester 1 - 2000

Time Allowed: THREE (3) hours

ANSWER ALL QUESTIONS.

Please wait until you are instructed before opening this exam paper.

When instructed, turn over to p.2, etc...

1

CP

2000/159.203

Alb

Question_1

(a)

Give the truth table for a THREE input NAND gate. Draw the NAND gate and show how it

can be configured to operate as an inverter.

[ 2 marks]

(b)

Given the Boolean expression: X = (A + ŪE).AU

Draw the logic circuit of the above expression and then show, using DeMorgan's theorem,

that it is equivalent to the expression: X = Ā + Ū

[ 2 marks]

(c)

Draw a circuit for an Asynchronous counter which counts from 0dec to 15dec.

[ 2 marks]

(d)

Redraw your circuit for an Asynchronous counter, to include circuitry which causes it to

count from 0dec to 9dec and then stop counting.

[ 3 marks]

(e)

Explain briefly, including the appropriate logic symbols, the operation of the following

devices, and for each one, give an example of where it might be used.

Tri State Buffer

Multiplexor

Decoder

[ 6 marks]

Question_2

You are required to control a repeating sequence which changes in response to two switches (Y,Z).

If Y = 0, Z = 0 the sequence is A > B > C > D

If Y = 1, Z = 0 the sequence is D > C > B > A

The general sequence is modified by Z. If Z = 1 then A is followed by C so that one of the letters is

omitted from the sequence.

For the controller of the above system:

(a)

Draw an ASM chart.

(b)

Give Boolean expressions for the states.

[ 3 marks]

[ 3 marks]

(c)

Design a circuit, using multiplexors, which will follow the sequences.

[ 5 marks]

(d)

Now consider that your repeating sequences will be controlled by a microcontroller. Write

the 2051 Assembler code which will control the sequences, assume the following:

Port_1 is an input with P1.0 = Y, P1.1 = Z

Port_0 is an output where P0.0 and P0.1 indicate the present state of your system.

[ 7 marks]

Information about the 2051 instruction set can be found in tables at the end of the paper.

Turn over to p.3, etc...

2

CP

2000/159.203

Alb

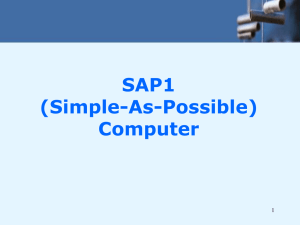

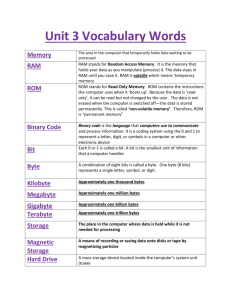

Question_3

Pico-computer architecture

WEMEM

OEMEM

Bus

OEPC

Tristate

buffer

OECONST

Tristate

buffer

Program INCPC

counter LDPC

OEACC

Tristate

buffer

LDACC Accumulator

const

mux

1

OEPORT

Tristate

buffer

Memory

Input Port

CO/C1

0

zero

detect

EQZ

Arithmetic

Logic Unit

xor

invertor

LDABR A Buffer

Register

sub

LDMAR Memory

Address

Register

(a)

The first instruction of a program is CLR. Explain, in detail, how this instruction is fetched

and implemented on the Pico-computer, after RESET has been pressed.

[ 6 marks]

(b)

Describe in general terms how you would implement a new instruction INCA, where the

value of the Accumulator is incremented. (Assume the instruction has already been fetched)

[ 4 marks]

Question_4

(a)

Given that large amounts of data are transferred over a standard telephone system, explain in

detail the concepts of two different methods of reducing the file transfer time.

[ 4 marks]

(b)

Given the data 0 1 0 1 1 0 0 you are required to use the Hamming process for error

detection and correction.

Generate the Hamming code, and show the final data to be sent.

Show how code, containing a single bit error, can be detected and corrected

[ 4 marks]

Turn over to p.4, etc...

3

CP

2000/159.203

Alb

Question_5

Information about the 2051 instruction set can be found in tables at the end of the paper.

(a)

Write a program, in 2051 assembler, that will check a string of hexadecimal data bytes for

errors.

The data is located from address 40h onwards.

The first byte of data indicates the number of bytes of the following string, the last byte of

the string is the modulo 256 (8 bit) checksum.

If the string contains no errors, halt your program with the value 00H in the accumulator,

otherwise the accumulator should contain the value FFH.

[ 7 marks for programming]

[ 2 marks for useful comments]

[ 2 marks for using a looping structure]

(b)

The 2051 has an on board timer which can be used by itself, or in conjunction with the serial

Port. Explain, briefly the various functions of the 2051 Timer.

[ 4 marks]

(c)

Write a piece of 2051 assembler code to enable interrupts from timer T0 after a Reset.

[ 2 marks]

+++++++++++

4

CP

2000/159.203

Alb

AT89C2051 Reference

Program Memory:

Data Memory:

07FFH

7FH

2FH

0023H

Serial Port

Timer 1 001BH

Interrupt Ext Int 1

0013H

Locations

Timer 0 000BH

Ext Int 0

0003H

RESET 0000H

Program Counter:

Bit-addressable

space (0-7F)

20H

{

11 18H

Bank

Select 10{ 10H

bits in

01{ 08H

PSW

00{ 00H

1FH

17H 4 banks of

registers

0FH R0 - R7

07H

Reset value of

Stack Pointer

16 bit register restricted to 0000H -> 07FFH

Special Function Registers (SFR) Space:

Byte Address

|

Name

|

Description

|

Bits

81H

|

SP

|

Stack Pointer

|

not bit addressable

82H

|

DPL

|

Low byte of DPTR

|

not bit addressable

83H

|

DPH

|

High byte of DPTR

|

not bit addressable

87H

|

PCON

|

Power control

|

not bit addressable

88H

|

TCON

|

Timer control

|

TF1-TR1-TF0-TR0-IE1-IT1-IE0-IT0

89H

|

TMOD

|

Timer mode control

|

not bit addressable

8AH

|

TL0

|

Timer 0 low byte

|

not bit addressable

8BH

|

TL1

|

Timer 1 low byte

|

not bit addressable

8CH

|

TH0

|

Timer 0 high byte

|

not bit addressable

8DH

|

TH1

|

Timer 1 high byte

|

not bit addressable

90H

|

P1

|

Parallel port 1

|

P1.7

98H

|

SCON

|

Serial control

|

SM0-SM1-SM2-REN-TB8-RB8-TI -RI

99H

|

SBUF

|

Serial buffer

|

not bit addressable

A8H

|

IE

|

Interrupt Enable

|

EA -

B0H

|

P3

|

Parallel port 3

|

P3.7

B8H

|

IP

|

Interrupt priority

|

-

D0H

|

PSW

|

Program Status Word

|

CY -AC -F0 -RS1-RS0-OV -F1 -P

E0H

|

ACC

|

Accumulator

|

ACC.7

->

ACC.0

F0H

|

B

|

B register

|

B.7

->

B.0

Interrupt control register

IE:

EA

ES,ETx

->

-

P1.0

-ES -ET1-EX1-ET0-EX0

->

-

P3.0

-PS -PT1-PX1-PT0-PX0

Global bit to enable interrupts

Serial interrupt (either RI or TI), Clock interrupt on overflow

5

CP

2000/159.203

Alb

Power control register

PCON:

set to 2 will stop the processor

6

CP

2000/159.203

Alb

Timer control and mode registers - 2 timers, 0 and 1

TCON: TF0/TF1

TR0/TR1

TMOD: mode1-mode0

mode = 0

mode = 1

mode = 2

Timer overflow flag timers 0/1

Timer run control bit. Set by software to switch timer ON

2 4-bit nibbles. Timer 1 high order nibble, Timer 0 low order.

13 bit timer

16 bit timer

8 bit auto-reload timer. THx -> TLx on overflow. Used by Serial

i/o as bit rate (*32). 0FDH in THx gives 9600bps for 11.059Mhz clock

Serial control register

SCON: SM0-SM1-SM2-REN-TB8-RB8 should be set to 010100 for normal operation

TI

set when the character has been transmitted

RI

set when a character is received

Addressing Modes:

Rn

direct

@Ri

#data

#data16

addr11

addr16

rel

bit

= Register R0 - R7 of the currently selected register bank.

= 8-bit internal data location's address. This could be an internal Data

RAM location (0-127) or a SFR.

= 8-bit internal Data RAM location addressed indirectly through R0 or R1.

= 8-bit constant included in instruction.

= 16-bit constant included in instruction.

= 11-bit destination address. Used by ACALL and AJMP.

The branch will be within the same 2K byte page of Program Memory as

the first byte of the following instruction.

= 16-bit destination address. Used by LCALL and LJMP.

A branch can be anywhere within the 2K byte Program Memory address

space.

= Signed (two's complement) 8-bit offset byte. Used by SJMP and all

conditional jumps. Range is -128 to +127 bytes relative to first

byte of the following instruction.

= Direct addressed bit in internal Data RAM or SFR.

| Byte | Cycle | C OV AC

Arithmetic

ADD

A,Rn

| Add register to Accumulator

|

1

|

1

| X

X

X

ADD

A,direct

| Add direct byte to Accumulator

|

2

|

1

| X

X

X

ADD

A,@Ri

| Add indirect RAM to Accumulator

|

1

|

1

| X

X

X

ADD

A,#data

| Add immediate data to Accumulator

|

2

|

1

| X

X

X

ADDC A,Rn

| Add register to Acc. with Carry

|

1

|

1

| X

X

X

ADDC A,direct

| Add direct byte to Acc. with Carry

|

2

|

1

| X

X

X

ADDC A,@Ri

| Add indirect RAM to Acc. with Carry |

1

|

1

| X

X

X

ADDC A,#data

| Add immediate data to Acc. / Carry

|

2

|

1

| X

X

X

SUBB A,Rn

| Subtract reg. from Acc. with borrow |

1

|

1

| X

X

X

SUBB A,direct

| Sub. direct byte from Acc. / borrow |

2

|

1

| X

X

X

SUBB A,@Ri

| Sub. indirect RAM from Acc./ borrow |

1

|

1

| X

X

X

SUBB A,#data

| Sub. imm. data from Acc. / borrow

|

2

|

1

| X

X

X

INC

A

| Increment Accumulator

|

1

|

1

|

INC

Rn

| Increment register

|

1

|

1

|

INC

direct

| Increment direct byte

|

2

|

1

|

INC

@Ri

| Increment indirect RAM

|

1

|

1

|

DEC

A

| Decrement Accumulator

|

1

|

1

|

DEC

Rn

| Decrement register

|

1

|

1

|

DEC

direct

| Decrement direct byte

|

2

|

1

|

DEC

@Ri

| Decrement indirect RAM

|

1

|

1

|

INC

DPTR

| Increment Data Pointer

|

1

|

2

|

MUL

AB

| Multiply A and B

|

1

|

4

| 0

7

X

CP

2000/159.203

DIV

AB

| Divide A by B

|

1

|

4

| 0

DA

A

| Decimal adjust Accumulator

|

1

|

1

| X

8

X

Alb

CP

2000/159.203

Alb

| Byte | Cycle | C OV AC

Logical

ANL

A,Rn

| AND register to Accumulator

|

1

|

1

|

ANL

A,direct

| AND direct byte to Accumulator

|

2

|

1

|

ANL

A,@Ri

| AND indirect RAM to Accumulator

|

1

|

1

|

ANL

A,#data

| AND immediate data to Accumulator

|

2

|

1

|

ANL

direct,A

| AND Accumulator to direct byte

|

2

|

1

|

ANL

direct,#data | AND immediate data to direct byte

|

3

|

2

|

ORL

A,Rn

| OR register to Accumulator

|

1

|

1

|

ORL

A,direct

| OR direct byte to Accumulator

|

2

|

1

|

ORL

A,@Ri

| OR indirect RAM to Accumulator

|

1

|

1

|

ORL

A,#data

| OR immediate data to Accumulator

|

2

|

1

|

ORL

direct,A

| OR Accumulator to direct byte

|

2

|

1

|

ORL

direct,#data | OR immediate data to direct byte

|

3

|

2

|

XRL

A,Rn

| Exc-OR register to Accumulator

|

1

|

1

|

XRL

A,direct

| Exc-OR direct byte to Accumulator

|

2

|

2

|

XRL

A,@Ri

| Exc-OR indirect RAM to Accumulator

|

1

|

1

|

XRL

A,#data

| Exc-OR immediate data to Acc.

|

2

|

1

|

XRL

direct,A

| Exc-OR Accumulator to direct byte

|

2

|

1

|

XRL

direct,#data | Exc-OR imm. data to direct byte

|

3

|

2

|

CLR

A

| Clear Accumulator

|

1

|

1

|

CPL

A

| Complement Accumulator

|

1

|

1

|

RL

A

| Rotate Accumulator left

|

1

|

1

|

RLC

A

| Rotate Acc. left through Carry

|

1

|

1

| X

RR

A

| Rotate Accumulator right

|

1

|

1

|

RRC

A

| Rotate Acc. right through Carry

|

1

|

1

| X

SWAP A

| Swap nibbles within the Accumulator |

1

|

1

|

NOP

| No operation

1

|

1

|

|

| Byte | Cycle | C OV AC

Boolean

CLR

C

| Clear Carry

|

1

|

1

| 0

CLR

bit

| Clear direct bit

|

2

|

1

|

SETB C

| Set Carry

|

1

|

1

| 1

SETB bit

| Set direct bit

|

2

|

1

|

CPL

C

| Complement Carry

|

1

|

1

| X

CPL

bit

| Complement direct bit

|

2

|

1

|

ANL

C,bit

| AND direct bit to Carry

|

2

|

2

| X

ANL

C,/bit

| AND complement of dir. bit to Carry |

2

|

2

| X

ORL

C,bit

| OR direct bit to Carry

|

2

|

2

| X

ORL

C,/bit

| OR complement of dir. bit to Carry

|

2

|

2

| X

MOV

C,bit

| Move direct bit to Carry

|

2

|

1

| X

MOV

bit,C

| Move Carry to direct bit

|

2

|

2

|

JC

rel

| Jump if Carry is set

|

2

|

2

|

JNC

rel

| Jump if Carry not set

|

2

|

2

|

JB

bit,rel

| Jump if direct bit is set

|

3

|

2

|

9

CP

2000/159.203

JNB

bit,rel

| Jump if direct bit is not set

|

3

|

2

|

JBC

bit,rel

| Jump if dir. bit is set & clear bit |

3

|

2

|

10

Alb

CP

2000/159.203

Alb

| Byte | Cycle | C OV AC

Data transfer

MOV

A,Rn

| Move register to Accumulator

|

1

|

1

|

MOV

A,direct

| Move direct byte to Accumulator

|

2

|

1

|

MOV

A,@Ri

| Move indirect RAM to Accumulator

|

1

|

1

|

MOV

A,#data

| Move immediate data to Accumulator

|

2

|

1

|

MOV

Rn,A

| Move Accumulator to register

|

1

|

1

|

MOV

Rn,direct

| Move direct byte to register

|

2

|

2

|

MOV

Rn,#data

| Move immediate data to register

|

2

|

1

|

MOV

direct,A

| Move Accumulator to direct byte

|

2

|

1

|

MOV

direct,Rn

| Move register to direct byte

|

2

|

2

|

MOV

direct,direct| Move direct byte to direct byte

|

3

|

2

|

MOV

direct,@Ri

|

2

|

2

|

MOV

direct,#data | Move immediate data to direct byte

|

3

|

2

|

MOV

@Ri,A

| Move Accumulator to indirect RAM

|

1

|

1

|

MOV

@Ri,direct

| Move direct byte to indirect RAM

|

2

|

2

|

MOV

@Ri,#data

| Move immediate data to indirect RAM |

2

|

1

|

MOV

DPTR,#data16 | Load Data Pointer with 16-bit const |

3

|

2

|

| Move indirect RAM to direct byte

MOVC A,@A+DPTR

| Move Code byte rel. to DPTR to Acc. |

1

|

2

|

MOVC A,@A+PC

| Move Code byte rel. to PC to Acc.

|

1

|

2

|

PUSH direct

| Push direct byte onto stack

|

2

|

2

|

POP

direct

| Pop direct byte from stack

|

2

|

2

|

XCH

A,Rn

| Exchange register with Accumulator

|

1

|

1

|

XCH

A,direct

| Exchange direct byte with Acc.

|

2

|

1

|

XCH

A,@Ri

| Exchange indirect RAM with Acc.

|

1

|

1

|

| Exchange low order digit indirect

|

| RAM with Accumulator

|

XCHD A,@Ri

|

1

|

|

1

|

| Byte | Cycle | C OV AC

Branching

ACALL addr11

| Absolute subroutine call

|

2

|

2

|

LCALL addr16

| Long subroutine call

|

3

|

2

|

RET

| Return from subroutine

|

1

|

2

|

RETI

| Return from interrupt

|

1

|

2

|

AJMP addr11

| Absolute jump

|

2

|

2

|

LJMP addr16

| Long jump

|

3

|

2

|

SJMP rel

| Short jump (relative address)

|

2

|

2

|

JMP

@A+DPTR

| Jump indirect relative to the DPTR

|

1

|

2

|

JZ

rel

| Jump if Accumulator is zero

|

2

|

2

|

JNZ

rel

| Jump if Accumulator is not zero

|

2

|

2

|

CJNE A,direct,rel | Compare direct byte to Accumulator

CJNE A,#data,rel

|

| and jump if not equal

|

| Compare immediate data to

|

| Accumulator and jump if not equal

CJNE Rn,#data,rel | Compare immediate data to register

| and jump if not equal

|

11

3

|

|

|

2

|

3

|

|

CJNE @Ri,#data,rel| Compare immediate data to indirect

|

|

|

2

|

3

|

|

| X

| X

|

2

| X

|

CP

2000/159.203

| RAM and jump if not equal

|

3

|

2

| X

DJNZ Rn,rel

| Decr. register and jump if not zero |

2

|

2

|

DJNZ direct,rel

| Decrement direct byte and jump if

|

| not zero

|

|

3

|

Alb

|

2

|

Constants:

Numbers:

Decimal - 34, Binary - 01110101B, Hexadecimal - 0A8H

Characters:

‘A’ - ‘Abc’ - ‘A’,00DH,00AH (mixed mode)

Operators:

()’s + - / * MOD SHR SHL NOT AND OR XOR

Assembler directives and controls

$MOD2051

Include file MOD2051 - defines 2051 symbols

;

Everything following a semicolon is a comment

Label:

Labels of statements used for program branches.

TEN

EQU

10

EQUates 10 with the symbol TEN

ON_FLAG

BIT

6

Assigns bit 6 (either data or SFR space) to the symbol ON_FLAG

BUFFER

DATA

32

Assigns byte 32 (either data or SFR space) to the symbol BUFFER

RESET

CODE

0

Assigns 0 in code space to the symbol RESET

DSEG

Makes the data space the currently selected segment

CSEG

Makes the code space the currently selected segment

BSEG

Makes the bit addressable area of data space the cur sel seg.

SP_BUFFER:

DS

6

Reserves 6 bytes of storage in data space. DSEG must be active.

IO_MAP:

DBIT

8

Reserves 8 bits of storage in bit space. BSEG must be active.

MESS1:

DB

‘Hi’

Store byte constants in code space.

ORG

56H

Specify a value for the cur sel segments location counter.

12