pll

ENEE 719-Fall 2001-Project 2

Phase-Locked Loop (PLL)

Akin Aktürk and Zeynep Dilli

Introduction:

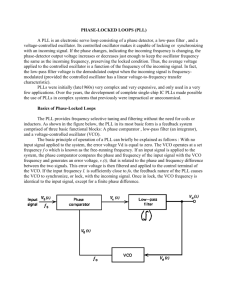

Digital phase-locked loops constitute an important block in communication circuits. They are used to recover the clock signal of the transmitted signal at the receiver end, thus provide data synchronization at both sides of communication circuits.

The block diagram of a PLL is shown in fig. 1.

‘Data in’ is the reference signal, which is either the received signal or the output of a local oscillator. The phases of the reference signal and the dynamically corrected clock are compared at the phase detector (PD), where a high output signal is produced in conjunction with the phase difference of the input waveforms. The resulting signal is passed through a loop filter, which is a low-pass filter used to add a pole to the overall system. The introduction of an extra pole in addition to the one introduced by the voltage-controlled oscillator (VCO) is necessary to the end of gaining further control over the feedback loop, thus preventing the locking of the output waveform on higher harmonics of the reference clock. VCO transforms the phase information into actual clock signals whose oscillation frequency is controlled via the voltage output of the PD after being averaged by the loop filter. The oscillations at the output of the VCO are fed back to the PD after a specified number of cycles, N. This number is set via the counter and controls the multiplication factor over the reference clock that the output signal is locked onto.

Figure 1: Block Diagram of a PLL

The closed loop gain of the PLL can be estimated using the gains of the individual subblocks:

Phase detector: K

PD

Loop filter: K

F

K

1

LPF s p

VCO:

K

VCO s

The overall closed loop gain becomes: H ( s )

clock

data

K

PD

K

VCO

K

F s

1

K

PD

K

VCO

K

F

N

This is a second order transfer function due to the s terms introduced by the VCO and the loop filter. Theoretically, a first order PLL, without a loop filter, can also work. However, as it was pointed out, the second order system is easier to control and would allow tracking of fast variations in the time domain, thus preventing the system from locking onto higher harmonics of the reference signal.

Phase Detector (PD) and The Loop Filter:

The schematic of the phase detector (PD) is shown in the upper left corner of fig. 2 . It is composed of two D flip-flops and an effective ‘AND’ gate, which provides the feed back to their ‘CLR’ pins. Both the phase and the frequency of the inputs, A and B, affect the output of the PD. PD has two outputs, which are the ‘Q’s of the D flip-flops and are named for reference purposes as ‘upper’ and ‘lower’ according their position on the page.

When ‘A’ leads ‘B’, the upper output enters a high state after the first appearance of the rising edge at input ‘A’. It would stay high until another rising edge emerges at the input

‘B’. This would cause the lower output to change state to high, which in turn causes the high level at the output of the ‘AND’ gate and the high enabled ‘CLR’ pins of the D flip- flops. The high level at the ‘CLR’ pins resets the upper and lower outputs of the flipflops. Then the output signals propagate to the ‘CLR’ pins via the ‘AND’ gate by causing a switch from high to low, which can be thought of as entering a ‘watch’ mode for the

PD. In the watch mode, both outputs are low and the circuit waits for a rising edge to change state of the either of the outputs. In summary, the upper output stays high between the consecutive rising edges of the inputs ‘A’ and ‘B’, while the lower output has an instantaneous peak during the rising edge of the input ‘B’. Similar arguments hold when

‘B’ leads ‘A’, except the roles of the upper and lower outputs are interchanged. This type of PD is capable of detecting phase differences of

2

, because it only checks the rising edges of the input signals.

After the PD, we utilized a charge pump at the input of the loop filter. It is used to decrease the sensitivity of the charging and the discharging of the capacitors of the loop filter to the supply variations. The current sources for the pumps can be seen in the lower portion of fig. 2 . They are designed to supply 75

A.

The loop filter is shown at the right hand side of fig. 2 . When the upper output of the PD is high, ‘A’ leads ‘B’ and the capacitors are charged through the current source at the source of the PMOS, whose drain is connected to the input of the filter. Likewise, when the lower output of the PD is high, ‘B’ leads ‘A’, the capacitors are discharged through the current source at the source of the NMOS, whose drain is also connected to the input of the filter. Both outputs of the PD cannot be high at the same time, since this would reset the outputs due to the feedback to the ‘CLR’ pins of the flip-flops. However, both outputs can be low, and this case would cause the input node of the filter to be floating, hence the accumulated charges on the capacitors are kept fixed, if the leakage via the

5k

resistor is ignored. The resistors are utilized to smooth out output voltage during rapid transients of the input signal.

Figure 2: Phase Frequency Detector and the Loop Filter

Figure 3: PD and Loop Filter responses to input transients

The responses of the PD and the loop filter to some input transients are shown in fig. 3 .

The first two rows represent the input waveforms to the PD. Let’s say the first and the second rows denote inputs ‘A’ and ‘B’, respectively. When ‘A’ leads ‘B’, charges are

pumped to the filter via the upper portion of the charge pump. This results in voltage increases at the input and the output of the loop filter, which are shown in the third and the forth rows, respectively. This voltage increase stops when the rising edge of the ‘B’ appears at the input of the D flip-flops. The direction of the output voltage could be inverted if the rising edge of the ‘B’ shows up at the input before the ‘A’ during the watch state of the PD, where both outputs are initially low. In summary, if ‘A’ has the first positive edge trigger at the watch state of the PD, output voltage increases until the outputs of the PD are reset due to the rising edge of the ‘B’. Inversely, if ‘B’ has the first positive edge trigger at the watch state of the PD, output voltage decreases until the outputs of the PD are reset due to the rising edge of the ‘A’. During the watch state output voltage stays constant, except some deviations in the voltage level due to the discharging of the capacitors through the loop resistor. As the figure shows, the loop filter smoothes out its input, so the output voltage does not have abrupt transitions. Finally, the last row shows the currents of the charge pumps during the charging and the discharging of the output. Both charge pumps supply 74

A. The symmetricity has been accomplished by adjusting the W/L ratios of the current mirrors. So the gain of the overall block can be summarized as follows:

K

PDI

I pump

2

74

A

2

Voltage Controlled Oscillator (VCO):

The schematic of the VCO is shown in fig. 4 . It is a current starved ring oscillator. The oscillation frequency of this circuit can be written as follows: f

OSC

I

D

NC tot

VDD

Here, N is 7 and VDD is 2.5V. C tot

depends on the utilized technology, so we have no control over this parameter. The frequency of the oscillations is controlled by V in

via I

D

.

So, we focused our efforts on designing symmetric current mirrors with linear I-V in curves over the range of input voltages that would give the oscillations around the operating range, which is between 100MHz and 200MHz for this design. Our investigations show that the boundaries of the operating range correspond to VCO input voltages of 1V and1.2V, respectively. So, the W/L ratios of both current mirrors shown in fig. 5 are adjusted such that a symmetric linear I-V in

curve, represented in fig. 6 , is achieved for the input voltages in the range of 1V-1.2V. Actually, the determination of the W/L ratios of the current mirrors requires a coupled solution of the system, because the V in

-f osc

relation also depends on the amount of the charges pumped via the mirrors.

Figure 4: The schematics of the VCO

Figure 5: Schematics of the Current Pumps

Figure 6: I-V in

for Current Pumps

However, the mirrors can be designed roughly at first, then the input voltages that result in desired oscillations can be noted and finally, the mirrors can be adjusted and the oscillations can be checked again for any deviations.

The proposed design for the VCO has the V in

-f osc

relation shown in fig. 7 . It has a quite linear curve.

250

200

150

100

50

0.9

0.95

1 1.05 1.1

1.15 1.2

1.25 1.3

Vin (V)

Figure 7: Vin-fosc Relation

The VCO gain can also be formulized by the help of fig. 7 , as follows:

K

VCO

( 196

103 ) MHz

( 1 .

2

1 .

0 ) V

Counter:

The schematics of the utilized 10-bit input, ripple carry type counter can be seen in fig. 8 .

Actually, this is a down counter. First, setting or resetting each flip-flop depending on the input value at that node loads a number to the D flip-flops. Later, the countdown starts.

The output is taken from the Q of each D flip-flop. For this configuration, D and the Qbar are connected together to trigger the change in Q value for each cycle. When zero is reached, it is detected by the OR gates and results in reloading of the counter.

For this project, we designed a 10-bit input counter because the design criterion was to achieve clock frequencies of 110MHz to130MHz using the reference clock of 200kHz.

This directly translates to N values of 500 to 650. This number range can be represented in the binary system using at least 10 bits.

Figure 8: The Schematics of the 10-Bit Input Counter

Simulation Results:

Each sub-block in fig. 1 is designed using the guidelines described before. The overall circuit shown in fig. 9 is simulated using the previous designs with N set to 600, which is

1001011000 in binary.

Before going into the details of the simulation results, a quick look at the design equations would be useful. Since there are two capacitors at the loop filter, this is a third order PLL, where the extra s comes from the VCO. When the utilized values are plugged into the equations, we calculated the natural frequency and the damping factor as 125kHz and 0.15, respectively. Although, the damping value seems to be much lower than the optimum value of 0.707, our first issue was to obtain fast locking, so we did not worry much about the damping value but the natural frequency.

The inputs to the PD are shown in fig. 10 . The upper plot is the reference clock or the input ‘A’ to the PD. Its frequency is 200kHz. The lower plot is the output of the counter, where a high peak is introduced at the output every time 600 cycles are counted at the input due to the sinusoidal output of the VCO.

H

K

F

( s )

s

2

clock

data

s

K

1

N

RC

1 sRC

1

C

2

1 s ( C

1

PDI

K

K

C

VCO

PDI

2

)

K

K

VCO

F

K

F

K

PDI

K

VCO

( sRC

1

1 )

H ( s )

K

PDI

RC

1

C

2 s

3 s

2

( C

1

C

2

)

RC

1

C

2

74

A

2

, K

VCO

s

93 MHz

0 .

2 V

K

PDI

K

VCO

NC

2

, R

K

PDI

K

VCO

5 k

, C

1

NRC

1

C

2

0 .

5 nF , C

2

3 n

K

PDI

K

VCO

NRC

1

C

2

n

125 kHz

1 .

87 nF

2

n

2

K

PDI

K

VCO

NC

2

n

RC

1

0 .

15

Figure 9: Overall PLL Circuit

Figure 10: Reference Clock and the Output of the Counter

Figure 11: Loop Filter and VCO Inputs

Figure 12: VCO Output at the Start and the End of the Simulation

In fig. 11 , the input and the output of the loop filter can be examined. The input, which is the first plot, is the voltage probed at the drains of the MOSFETs of the tri-state buffer with the charge pumps attached to their sources. The loop filter works like a low pass filter, so the output is like the input without the sharp jumps during the transitions. The output voltage increases when the reference clock leads the generated clock and inversely, the output voltage decreases when the reference clock lags the generated clock.

The flat regions on the output waveform corresponds to the so-called “watch state” of the

PD, where both outputs are low and are the charge pumps are disconnected from the input of the filter. In summary, the simulated VCO input increases and then has swings around the steady state value with decreasing amplitudes in time and finally reaches the steady state value in about 450

s.

The outputs of the VCO at the beginning and at the end of the simulation are shown in fig. 12 . It is interesting to note that the output of the VCO stays at a dc offset value until about 16

s, from where on the input voltage passes the 0.6-0.7V threshold value for the start of the oscillations. At the end of the simulation, the VCO output is observed to have oscillations with a frequency is of about 120MHz, which is the designed value with our setting of N=600.

In conclusion, the PLL has been designed block by block and simulated using PSPICE. It has been shown that the initial design criterion is achieved by generating a clock signal at

120MHz using the reference signal of 200kHz.