- Flintbox

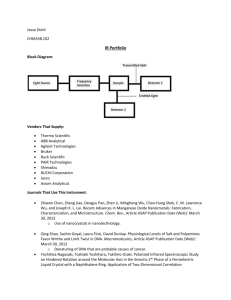

advertisement

395 Pine Tree Road, Suite 310 Ithaca, NY 14850 Main: 607-254-4698 Fax: 607-254-5454 www.cctec.cornell.edu Low-Voltage Flash Memory: 3.2V write and erase voltage (NON-CONFIDENTIAL INFORMATION ONLY) D-2768 Overview: Flash memory has advantages for many applications. Compact and non-volatile, it is broadly used in consumer electronics and on integrated circuits. Demand for flash memory modules for cameras and MP3 players is exploding. Unfortunately, the current high voltage required for the write and erase functions of flash is incompatible with the low voltage requirements of logic circuits. Moreover, high voltage requirements increase power consumption, force the use of additional circuitry, and increase manufacturing costs by necessitating thicker dielectrics layers and increased separation of circuits to prevent cross talk. Drs. Kan, Liu and Narayanan have invented an easily implemented method for significantly reducing the actual voltage required for write and erase functions, from the 12V to 15V required by current flash memory to 4V or less without charge pumps or degrading the retention characteristics. This invention will reduce manufacturing costs for and increase the ability of designers to integrate flash memory with logic circuits. Technology: Cornell’s technology is a novel design scheme for chip contacts that Fringing field enhances tunneling through the metal/semiconductor barrier by utilizing the large built-in electric fields at the interface of metals with different work functions. To construct this new contact, nanocrystals of one metal are Metal 2 formed on a semiconductor surface at the electrode interface and are then Metal 1 surrounded by a relatively thick layer of a second metal with a different work Oxide function which is deposited on top of the nanocrystals. The resulting structure is shown in Figure 1. The work function difference between the metals sets up a large Metal 3 electric field (see Figure 2) in the silicon close to the triple interface of the two metals and silicon. This field is very similar to the fringing field between two capacitor plates and can be significantly higher than the original metalsilicon Schottky fields. The field creates a barrier significantly thinner than Figure 1 the normal barrier and thus enhances field emission. Figure 3 shows the tunneling currents through a MOS capacitor for different voltages applied across the capacitor. Without the Original Contact Metal nanocrystals, the voltage required to obtain a 1.00E-6 A/cm2 tunneling current density is -15.3V. The other two curves show the results obtained for different densities and geometries of embedded nanocrystals. In the best, the voltage required to obtain the same 1.00E-6 A/cm2 tunneling Metal current density is a mere -3.2V. Nanocrystal Applying this approach to the control gate of flash memory cells significantly reduces the barrier to charge injection encountered during write and erase functions and improves the tunneling enough to Si Substrate significantly reduce overall voltage requirements for write and erase functions. Figure 4 shows an example of an EEPROM integrating Figure 2: Contact structure nanocrystals into its design. Office of the Vice Provost for Technology Transfer and Economic Development Tunneling Enhancement by Embedded Metal Nanocrystals Capacitor size: 50um x 50um, TOX=1 80A 1.00E-03 Reaching current compliance Tunneling Current Density (A/cm2) 1.00E-04 1.00E-05 C1 C2_1 1.00E-06 C2_2 C2_3 1.00E-07 1.00E-08 1.00E-09 -20 -18 -16 -14 -15.3V Figure 3 Further enhancing the value of this design, the charge transmission characteristics of flash memory constructed using nanocrystals are asymmetric; forward injection is dramatically enhanced by the fringing field while backward leakage is not seriously affected. This means that while the write and erase voltages can be reduced by a factor of 3 to 5 times, the integrity of the stored charge over time is basically unchanged from that of standard designs. -12 -10 -8 -6 -6.2V Vg (V) Reduction V erase -4 -4.9V -2 0 -3.2V =- Oxide insulator Nanocrystals Control gate Floating gate Drain Source Silicon substrate Figure 4: Flash memory cell Advantage: This new contact design is easily implemented on standard chip processing equipment, but will have significant impact on flash memory cost and performance. It increases the ease with which flash and logic can be integrated into the same chip. It lowers power consumption and increases write and erase speed. It lowers manufacturing cost by allowing thinner layers of insulator and by eliminating the need for additional circuits to boost chip voltage for high write and erase (e.g. 9V to 20V) voltages. Patent and Licensing Status: U.S. and foreign rights are available. Exclusive and nonexclusive licenses will be considered. Contact: Martin Teschl E-mail: mt439@cornell.edu Phone: 607-254-4454 2