ECE362/CS362/MATH391

advertisement

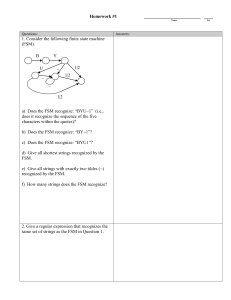

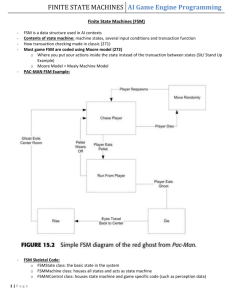

ECE 462/CS 462/MATH 491 LOGIC DESIGN Course Goals This course is a technical elective for electrical and computer engineering, computer science and mathematics majors. The goals are to impart advanced theoretical concepts in the design of digital logic circuits that will prepare a student for graduate research work in logic optimization, simulation and testing, asynchronous circuits, and finite-state machine theory. For explanation of the letters in parentheses after each Instructional Objective please see the legend at the bottom of this document. Instructional Objectives A. By half-way through the semester (roughly after 7 weeks), students will be able to do the following in relation to combinational circuits. 1. Generate four different types of canonical representations of Boolean expressions, namely, Sum of Fundamental Products, Complete Sum of Prime Implicants, Ordered Binary Decision Diagram (BDD) and Reed-Muller Canonical (RMC) forms. (a,b,j) 2. Execute by hand the Quine-McCluskey logic minimization algorithm involving generation of prime implicants and minimal cover. (a,b,c) 3. Generate by hand all prime implicants from a given Boolean sum of products expression using Iterative Consensus method. (a) 4. Formulate minimal cover problem into a Boolean algebraic form, using Petric's Method. (a) 5. Compute Maximal Set of Permissible Functions (MSPF) and Compatible Set of Permissible Functions (CSPF) in logic circuit. (a,c) 6. Determine the existence of static logic hazard in combinational circuits using analytical and simulation methods. (a,k) 7. Design two-level combinational circuits that are minimal and hazard-free. (c) 8. Determine if a Boolean function is totally symmetric and express it in a compact notation. (a) 9. Derive several properties of Unate Boolean functions in relation to prime implicants and minimal sums. (a,j,k) 10. Compute Boolean Difference of a function with respect to a variable and derive a test vector for a stuck-at fault on a node. (a) 11. Derive a test vector for stuck-at fault in a network using path sensitization method. (a,b,j,k) 12. Perform a simple decomposition of a Boolean funciton into two disjoint functions (a) 13. Express a Boolean function as a Threshold Function (if one exists) by formulating a system of inequalities and solving it or prove that a solution does not exist. (a) B. By the end of the second half of the semester (after another 7 weeks) students will be able to do the following in relation to sequential circuits. 1. Analyze a simple latch and express its behavior in equation and tabular forms. (a,b) 2. Identify a potential hazard problem in widely used clocked SR and D latches and construct three different solutions to eliminate this hazard using delay insertion in circuits, additional logic gate and constraining the clock and clock-bar signals. (a,c) 3. Analyze Fundamental Mode asynchronous circuits for state behavior, Critical Races and Essential Hazards. (a,j) 4. Design fundamental mode SR and D flip-flops and analyze them for essential hazards. (c) 5. Analyze pulse mode circuits designed using edge-triggered flip-flops. (a,b) 6. Explore sequential circuit design alternatives, double-latch and single-latch two-phase designs, and single-latch single-clock designs. (j) 7. Derive state tables from word description of finite state machine (FSM) behavior. (a,c) 8. Derive general capabilities of finite state machines (FSMs). (b) 9. Simplify a completely specified FSM by removing unreachable states and equivalent states. (a,c) 10. Derive state equivalence partition of a completely specified FSM. (a,c) 11. Determine if two FSMs are equivalent in their behavior. (a,b) 12. Reduce the number of states of an incompletely specified FSM by computing maximal compatibility classes of states. (a,c) 13. Derive a Synchronizing (Reset) Sequence for a given FSM, or show that such a sequence doesn't exist. (a,b) 14. Derive a Homing Sequence for a given FSM which when applied to the FSM can uniquely identify the final state by observing the outputs. (a,b) 15. Derive a Distinguishing Sequence for a given FSM which when applied to the FSM can uniquely identify the starting state by observing the outputs. (a,b) 16. Devise a Machine Identification Experiment for an FSM. (a,b) 17. Devise a Checking Experiment to check the malfunction of an FSM assuming the number of internal states do not increase as a result of the malfunction. (a,b) 18. Identify the cost and complexity of testing sequential circuits and devise Design for Test solutions to reduce the cost and complexity of testing. (a,c,j) 19. Express a set of binary strings in the compact Regular Expression Form. (a,b) 20. Prove that the set of input sequences that take an FSM from one state to another state is a Regular Set. (a) 21. Derive the Regular Expression for the set of input sequences recognized by a given FSM. (a,b) 22. Design a non-deterministic machine that recognizes a regular expression. (a,c) 23. Design a FSM that recognizes a regular expression. (a,c) Legend for Outcomes a. Ability to apply knowledge of mathematics, science and engineering b. Ability to design and conduct experiments as well as analyze and interpret data c. Ability to design a system to meet desired goals j. Knowledge of contemporary issues k. Ability to use the techniques, skills, and modern engineering tools necessary for engineering practice Revised Spring 2005