x signal

advertisement

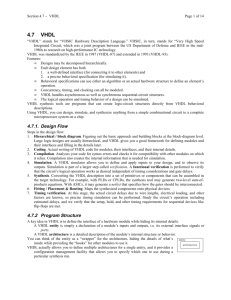

1. a. In the VHDL language a number of architecture bodies may refer to the same design entity. Explain the intention of this feature. [4 marks] Different architecture bodies, describing the same design, may describe the design in more or less detail, and at varying levels of abstraction. In the early stages of a design the component may be described in a high level behavioural manner which is not synthesisable. As the design progresses a detailed synthesisable architecture will be developed. Alternative design strategies may also be explored with different architecture bodes. b. Explain what is meant by concurrent and sequential statements, and where such statements may be used. Include in your discussion the conditions necessary for each type of statement to be executed. [6 marks] Concurrent statements appear within an architecture body, sequential statements appear within a process body (and also subprogram bodies). A concurrent statement is executed whenever a signal on the right hand side of the assignment changes, or for a process, when a signal to which the process is sensitive changes. Sequential statements are executed in order within the process or subprogram body. c. A VHDL architecture body contains the statements: z <= x; x <= y after 10 ns; Assuming that the signal y changes value at time 25 ns, at what times are the above statements executed and when do the signals x and z change value, and why? [4 marks] The signal x will change at time 35 nS. Since y appears on the right hand side of the second concurrent assignment statement that statement will be executed at time 25 nS, and will schedule a change to x at time 35 nS. Since x then changes at time 35 nS this causes the first concurrent assignment statement to be executed at time 35 nS, this will schedule a change to z for time 35 nS + delta, and so z changes at time 35 nS + delta. d. A certain design requires two clock signals referred to as clka and clkb. During the first 10% of the clock period both clocks are low, then clka is high for 40% of the clock period, for the next 10% of the clock period both signals are low, for the final 40% of the clock period clkb is high. Assume the clock period is 10 nS. Sketch these signals and then write VHDL statements (including any declarations) needed to generate such clock waveforms. [6 marks] First declare the signals clka and clkb to be of type std_logic and initialise to logic ‘0’. signal clka : std_logic := ‘0’; signal clkb : std_logic := ‘0’; and then in the architecture body: clkgen : process begin wait for 1 nS; clka <= ‘1’; wait for 4 nS; clka <= ‘0’; wait for 1 nS; clkb <= ‘1’; wait for 4 nS; clkb <= ‘0’; end process clkgen; 2. a. Describe what is meant by a sensitivity list in the context of a VHDL process. [4 marks] A sensitivity list on a process determines when the process resumes execution after suspension. A change on any signal in the sensitivity list will cause the process to resume execution. The process is suspended when the last sequential statement within the process has executed. b. A process describing combinational logic is required. The input to this combinational logic is to be a std_logic_vector signal x. The result is to be a signal y which is true if and only if there are two consecutive logic ‘0’s in the input array. Write the VHDL code for this process explaining the function of each statement. [8 marks] cl : process(x) variable yvar : std_logic; begin yvar := ‘0’; -- initialise y to logic ‘0’ for n in x’left to x’right – 1 loop if((x(n) = ‘0’) and (x(n+1) = ‘0’)) then yvar := ‘1’; end if; end loop; y <= yvar; end process cl; c. A VHDL testbench for a block of combinational logic must generate all possible inputs to the combinational logic. The combinational logic has three inputs b, c and d. Each input must be applied to the combinational logic for 10 nS. Write a process which generates these inputs and then terminates. [8 marks] fourin : process begin b <= ‘0’; c <= ‘0’; d <= ‘0’; wait for 10 nS; d <= ‘1’; wait for 10 nS; c <= ‘1’; d <= ‘0’; wait for 10 nS; d <= ‘1’; wait for 10 nS; b <= ‘1’; c <= ‘0’; d <= ‘0’; wait for 10 nS; d <= ‘1’; wait for 10 nS; c <= ‘1’; d <= ‘0’; wait for 10 nS; d <= ‘1’; wait for 10 nS; wait; end process fourin; 3. a. Explain what is meant by synthesisable VHDL code. Include an example of code which is synthesisable, and an example of code which may not be synthesised. [4 marks] Synthesisable VHDL code may be converted by a synthesis tool, a computer program, into a list of logic gates and the interconnections between which implement the circuit described by the original VHDL. An example of a synthesisable statement is simply: x <= y and z; and an example of a non-synthesisable statement is: x <= y and z after 15 nS; The latter statement is not synthesisable due to the inclusion of the assignment delay. b. A certain design requires an N bit register. The register should load new data on the rising edge of a clock signal clk. A reset line named rst_n is also required. When this line is at logic ‘0’ the register should, on the next rising edge of clk, set the register contents to all logic ‘0’. Write a complete VHDL entity declaration and architecture body for this design. [12 marks] library ieee; use ieee.std_logic_1164.all; entity regn is generic(N : integer); port(clk : in std_logic; rst_n : in std_logic; d : in std_logic_vector(N – 1 downto 0); q : out std_logic_vector(N – 1 downto 0)); end entity regn; architecture rtl of regn is begin rn : process(clk) begin if(clk’event and clk = ‘1’) then if rst_n = ‘0’ then q <= (others => ‘0’); else q <= d; end if; end if; end process rn; end rtl; c. Describe the use of the VHDL report statement. Modify the above code to print a message whenever the register is reset. [4 marks] The report statement prints a given VHDL string on the simulator console and sets an error level of either FAILURE, ERROR, WARNING or NOTE. The report statement is a simple method of printing a short string for informational purposes or as simulation errors are detected. To report resets in the above example simply add the statement: report “RegN reset” severity note; after the “if rst_n = ‘0’ “ statement. 4. a. Two M bit signals, a and b, are alternately passed to an M bit output bus on succeeding cycles of a clock signal named clk. The output bus is name z. Write a complete synthesisable VHDL description of the circuit. [10 marks] library ieee; use ieee.std_logic_1164.all; entity outmux is generic(M : natural); port(clk :in std_logic; rst_n : in std_logic; -- needed for synthesisable description. a, b : in std_logic_vector(M – 1 downto 0); z : out std_logic_vector(M – 1 downto )); end outmux; architecture rtl of outmux is begin om : process(clk) variable outswitch : std_logic; begin if clk’event and clk = ‘1’ then if rst_n = ‘0’ then outswitch := ‘0’; else outswitch := not outswitch; end if; if outswitch = ‘0’ then z <= a; else z <= b; end if; end if; end process om; end rtl;