section51final

advertisement

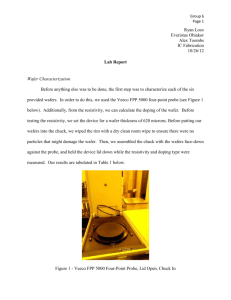

5. Fabrication The device fabrication process had two distinct components: the silicon process and the PDMS process. All silicon processing except for ion implantation was completed on campus in the Integrated Circuits Laboratory (ICL) and Technology Research Laboratory (TRL). Wakefield, MA. Ion implantation was done at Implant Sciences Corporation in The PDMS processing was done on campus in the Exploratory Materials Laboratory (EML). 5.1 Silicon process The silicon process used four inch, <100> n-type wafers. Before any processing was done, a four-point probe was used to measure the sheet resistivity of one wafer in the starting lot. A bulk resistivity of 11.1 ohm/cm was measured, indicating a weak n-type doping of around 5x1015 cm-3. The first fabrication step was an RCA clean for ten wafers before they could be introduced into the ICL field oxide tube. Next, a 500Å thermal oxide was grown on the wafers. This purpose of this oxide layer was to prevent implant damage to the silicon. The oxide was grown in a wet ambient for 7 minutes, and was measured to be 470Å with the UV1280. Next, alignment marks were patterned in the silicon, to which masks 1, 2, 3, and 4 could later be registered. This was accomplished by patterning resist over the oxide, etching through the 500Å of oxide with a one minute BOE dip, and plasma (SF6) etching 5000Å into the silicon with the AME5000. After etching one wafer in the AME5000 for 50 seconds (at a characterized etch rate of 105Å/sec), it was observed that the alignment marks were not being etched into the silicon, perhaps due to a photolithography problem. Profilimetry revealed that the patterned areas of the photoresist were too shallow; as the resist had been developed for a full minute, underexposure was suspected. Progressively longer test exposures were performed on several wafers, until it was determined that a 15 second exposure was necessary for proper patterning. Later, it was realized that the chrome masks were being underetched during the transfer process from transparencies. This resulted in the clear areas of the masks being somewhat cloudy, requiring the longer exposure time. After resolving the exposure problem, the wafers were ashed, photoresist was reapplied, and they were re-exposed to mask #0 for 15 seconds. The one minute BOE dip was repeated, and the wafers were etched in the AME5000. After ashing the photoresist, the depth of the alignment marks was measured with the profilimeter, indicating an acceptable etch depth of 4600Å at the center of the wafer and 4500Å at the edges. Once the alignment marks were in place, the wafers were sent out for three successive ion implants. First, the wafers were patterned with mask #1 to define the ptype the sensor regions. A Boron implant of dose = 5x1013 cm-2 and energy = 100 keV was performed. When the wafers were returned, they were dipped twice in Piranha to strip the photoresist and clean for further processing in TRL. The wafers were then patterned with mask #2 to define the conductive p+ traces which would connect the active regions and gold channel electrode to their respective gold traces. The wafers were implanted again with Boron at the same energy, but with a higher dose of 5x10 15 cm-2. Instead of stripping the resist (which had hardened from the implant process) with a double Piranha dip which was used earlier, the wafers were ashed in the TRL asher for 2 hours, which removed all photoresist. Then a single Piranha dip was done for cleaning. Finally, the wafers were patterned with mask #3 to define the n+ field implant. Phosphorus was implanted with dose 5x1015 cm-2 and energy 125keV, and the resist was ashed before a single Piranha dip. After the final ion implant, the thin 500Å oxide was stripped with a 65 second BOE dip, re-exposing the bare silicon (along with the implanted regions and the alignment marks that were etched earlier). The wafers were cleaned with a Piranha dip and an RCA clean, and a 10,000Å thermal oxide was grown at 1050C. This step also served to drive in the dopants. An actual oxide thickness of approximately 8750Å was measured with the UV1280. The Tencor profilimeter also used to measure a 4000Å etch depth over the alignment marks, and a 150-250Å step height over the n+ implanted areas. In the next process step, the wafers were coated with photoresist and patterned with mask #4. This mask defined the thick oxide cuts that would expose the active areas of the sensors, and connect the metal traces to the heavily doped n- and p-type traces. The oxide was wet etched with a 10 minute BOE dip. In the first process run, we determined that the oxide was not etched deep enough, due to a slower BOE etch rate than expected; we originally thought that the 7:1 etchant had an etch rate of 1000Å/min, while the actual etch rate is closer to 700Å/min. Fig. 5.1 shows an AFM scan of one of the shallow contact cuts in the first batch of wafers. The thickness of the oxide was measured to be approximately 8700Å, while the contact cut reached a depth of only 6900Å. To correct this problem, the etch time was lengthened to 14 minutes in the second process run. When the longer etch time was used, it was observed that the backside of the wafer de-wetted, indicating that the hydrophobic silicon beneath the oxide had been successfully exposed. Once the oxide contact cuts were etched, the photoresist was stripped with Piranha, and a fresh coat of resist was applied. The wafers were then patterned with mask #5, to define the gold traces and bias electrode. After a short 3 minute ash to clean (or "de-scum") the areas where metal would be deposited, the wafers were dipped in BOE for 10 seconds to etch any remaining oxide at the metal contact points. Gold was deposited with an e-beam evaporator, on top of a thin layer of chromium (to promote adhesion). In the first process run, 100Å of chromium was first deposited at a rate of 2.5Å/sec, then 4000Å of gold at a rate of 4Å/sec. Unfortunately, the gold peeled off during the subsequent liftoff step, most likely due to to bad chromium coverage. We learned that the e-beam should be swept over the surface of the chromium solid during deposition, due to the fact that Cr goes directly from a solid to a liquid (unlike gold, which melts). We mistakenly focused the beam in one spot, which created a deep hole in the chromium sample and resulted in non-uniform evaporation. After stripping the remaining metal with gold and chromium etchants, resist was re-applied and the wafers were patterned. The metals were re-deposited, with the chromium thickness increased to 300Å to ensure proper gold adhesion. The gold thickness was also increased to 5000Å, to reduce trace resistance. The last step was metal patterning. Rather than etching away the unwanted metal, a liftoff process was used. After gold was deposited, the wafer was dipped in acetone and agitated in an ultrasonic bath for approximately ten minutes. The gold that was deposited on top of photoresist was released as the resist was stripped from the wafer. The gold that was deposited in clear areas remained on the wafer. Once the gold had lifted off, the wafer was transferred first to another container of acetone where it was rinsed, and then the wafer was rinsed in methanol, isopropanol, and water. The first time we tried the liftoff process, the second acetone dip was not done, and gold particles remained on the wafer (Fig. __). When the second acetone dip was used, nearly all gold particles were washed away. The main drawback of using gold liftoff is that the patterned regions have jagged edges. As the minimum feature size of our device is quite large, however, rough edges are really not a problem. The use of an image-reversal photoresist would have improved the edge definition of the patterned metal, but this would have required a negative image of mask #5 to be printed and transferred to chrome. Furthermore, the rough edges that we observed (Fig. __) were more likely due to the use of transparency masks, which is discussed in section 5.3. After metal patterning, simple diode tests were performed on the wafers to check for electrical connectivity. This was done with a probe station and multimeter in TRL. Thick photoresist was then spin-coated on the wafer and softbaked. This layer served to protect the wafer from damage which may occur during dicing.