各功能模組、基本線路之模式,進而深入研究低耗電、快速元件之設計

advertisement

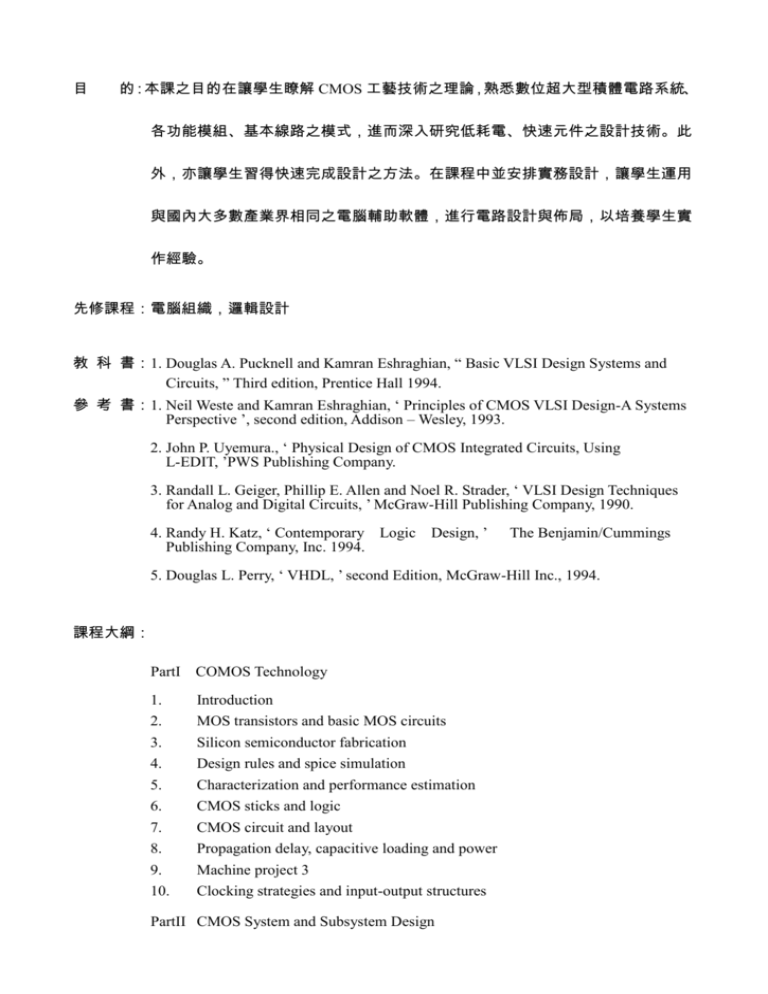

目 的:本課之目的在讓學生瞭解 CMOS 工藝技術之理論,熟悉數位超大型積體電路系統、 各功能模組、基本線路之模式,進而深入研究低耗電、快速元件之設計技術。此 外,亦讓學生習得快速完成設計之方法。在課程中並安排實務設計,讓學生運用 與國內大多數產業界相同之電腦輔助軟體,進行電路設計與佈局,以培養學生實 作經驗。 先修課程:電腦組織,邏輯設計 教 科 書:1. Douglas A. Pucknell and Kamran Eshraghian, “ Basic VLSI Design Systems and Circuits, ” Third edition, Prentice Hall 1994. 參 考 書:1. Neil Weste and Kamran Eshraghian, ‘ Principles of CMOS VLSI Design-A Systems Perspective ’, second edition, Addison – Wesley, 1993. 2. John P. Uyemura., ‘ Physical Design of CMOS Integrated Circuits, Using L-EDIT, ’PWS Publishing Company. 3. Randall L. Geiger, Phillip E. Allen and Noel R. Strader, ‘ VLSI Design Techniques for Analog and Digital Circuits, ’ McGraw-Hill Publishing Company, 1990. 4. Randy H. Katz, ‘ Contemporary Logic Design, ’ Publishing Company, Inc. 1994. The Benjamin/Cummings 5. Douglas L. Perry, ‘ VHDL, ’ second Edition, McGraw-Hill Inc., 1994. 課程大綱: PartI COMOS Technology 1. 2. Introduction MOS transistors and basic MOS circuits 3. 4. 5. 6. 7. 8. 9. 10. Silicon semiconductor fabrication Design rules and spice simulation Characterization and performance estimation CMOS sticks and logic CMOS circuit and layout Propagation delay, capacitive loading and power Machine project 3 Clocking strategies and input-output structures PartII CMOS System and Subsystem Design 11. 12. Design of adders Design of latches, registers and counters 13. 14. Multipliers PLAs, finite state machines 期中考 15. 16. 17. 18. 19,20 Microprocessor design Data path, control and buses Review of midterm examination Finite state machines for CPUs Controller implementation 21,22 Test and testability PartIII CAD Tools 23,24 Hardware design languages 25,26 Presentation 27 Conclusions 1. H. C. Chung, Y. H. Chang and Y. K. Lin “ Scalability of a Phase_reconfigurable Multiprocessor Architecture on Jacobi Algorithm, ” Procs. Of ICS, Dec. 12-15, 1994, pp. 200-205. 2. Y. K. Lin and C. L. Wu, “ A VLSI Graphics Processor for High Resolution Dynamic Graphics, ” Procs, of ICPP, Dec. 12-15, 1994, pp. 479-484. 3. H. C. Chung, C. L. Wu, J. Rakes, P. J. Zievers and Y. K. Lin, “ Design and Evaluation of Multiprocessor Architecture with Decentralized Control, ” Procs. of ICPP, 1994, pp. I-97-I-100. 4. H. C. Chung, J. Rakes, P. J. Zievers, Y. K. Lin and C. L. Wu, “ Architecture Features and Evaluation of a Variable_topology Multiprocessor for Real_time Application, ” 36th Midwest Symposium of CSP., Vol. 1, August 16-18, 1993, pp. 1-4. 5. H. C. Chung, Y. K. Lin, S. Szygenda and C. L. Wu, “ An Effective Modeling for Design Error Simulation, ” 6th VLSI Design CAD Symposium, August 17-19, 1995, pp. 89-92. 6. H. C. Chung, Y. K. Lin and C. L. Wu, “ High speed ROM-based Control Unit for Modern Processors, ” 6th VLSI Design CAD Symposium, August 17-19, 1995 pp. 193-196. 7. 楊明賢,劉順仁,林瀛寬,葛丕昌,“ 浮點運算快速傅立葉轉換器度(FFT), ”新新雙月刊, 第二十五卷第三期,May 1997, pp. 96-112. 8. C. M. Tai, J-C. Chen, Issac S-H. Chou, S-R. Ker, J-R. Chen, H-H. Tung T-M. Chiang, C-B. Lin, R-B. Lin and Y. K. Lin, “ Development of a 0.25 um Cma standard cell Library, ” Proc CSIA’98, Chip Technolisy, pp. 73-78.