Lab4

advertisement

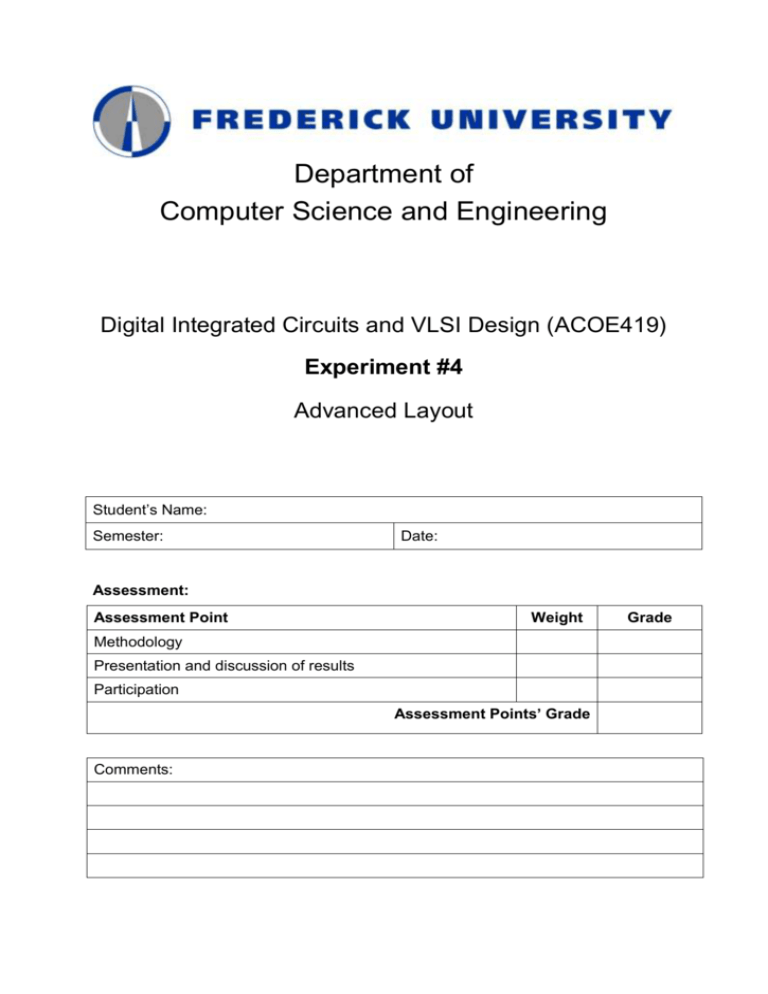

Department of Computer Science and Engineering Digital Integrated Circuits and VLSI Design (ACOE419) Experiment #4 Advanced Layout Student’s Name: Semester: Date: Assessment: Assessment Point Weight Methodology Presentation and discussion of results Participation Assessment Points’ Grade Comments: Grade Digital Integrated Circuits and VLSI Design Lab4- ACOE419 Experiment #4: Advanced Layout Objectives: The objective of this experiment is to show students how to use the Electric VLSI system to design more advanced layouts. Procedure: Use the Electric VLSI system available at http://www. Layout tips: First place nodes, then connect them using arcs and finally move them to their optimum position. Execute DRC often, for example after each step, because it is easier to find and correct errors. MOSIS design rule summary: Exercise 1: a) Draw a stick diagram for the compound gate implementing the logic function Y ABC D . 1 Digital Integrated Circuits and VLSI Design Lab4- ACOE419 Insert stick diagram b) Launch the Electric environment and create a new cell, by using the Cell menu => new cell. Name the cell. Select “layout” in the components view and “mocmos” in the “Components” view. Toggle the grid by pressing Ctrl+G. The distance between grid dots is λ. c) Draw the layout for the stick diagram of (a) d) Select “Tools => DRC => Check Hierarchically”. If there are error messages, find the errors in the schematic. e) Verify the layout using the spice deck provided at .... Insert simulation screenshot here Questions 1. Does the gate function as expected? 2 Digital Integrated Circuits and VLSI Design Lab4- ACOE419 2. How much was the overshoot of Y in the simulation? 3. In the simulation, measure the values of the following delay parameters: Rising propagation delay (tpdr = time from 50% of input crossing to 50% of output crossing when rising) Falling propagation delay (tpdf = time from 50% of input crossing to 50% of output crossing when falling) Rise time (tr = time required to go from 20% to 80% of value) Fall time (tf = time required to go from 80% to 20% of value) Open the log file, and compare the times you measured with the ones measured by the simulator. 3