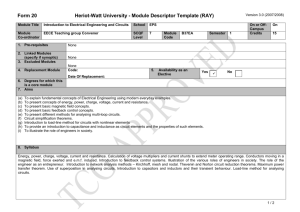

Word Doc - UCL Computer Science

advertisement