High Temperature Electronics Assembly and Packaging

advertisement

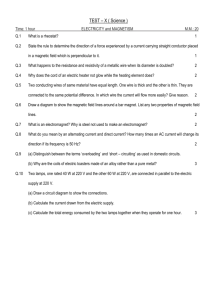

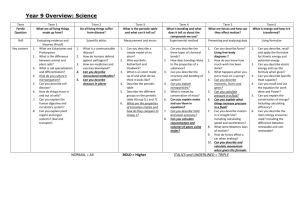

Extreme Environment Electronics Assembly and Packaging Packaging of SOI, SiC All compositions are and GaN components and in weight percent circuits for High Temperature: Silicon 97%Au, 3%Cu Carbide and Gallium 72%Au, 26%Cu, 2%Ni Nitride based electronics can operate at temperatures of 500-600oC, while 53%Sn, 35%Ni, 12%Au silicon-on-insulator (SOI) 55%Ni, 41%Sn, 4%Cu technology can be used up 32%Cu, 28%Ni, 26%Au, 14%Sn to 300oC, providing high levels of integration for analog, digital control and power electronics. AuSn - 2,000hrs@400C However, to build Ti/TiW/Au– Au(20 m)/Ni/Cu functional electronic products, the devices must be packaged and interconnected. This research area is evaluating materials and processes for interconnect substrate fabrication, die attach, wire bonding and packaging. Liquid phase transient and thermocompression bonding are being explored for traditional die attach as well as for a sandwich approach where substrates are bonded to both sides of the device, eliminating the need for wire bonding. Substrates – For power modules, direct bond copper on Al2O3 and AlN and active metal braze copper on Si3N4 substrates are being evaluated. A key issue is the thermal cycle performance over a wide temperature range due to the coefficient of thermal expansion (CTE) mismatch between the copper and the ceramics. Surface finishes for the copper compatible with high temperatures in air are also an issue. For low power applications (digital, analog, control), thick film on AlN, Al2O3 and SiN4 is being investigated. Die attach – AuGe and AuSi are being studied for SOI die attach, while liquid phase transient (LPT) bonding using Au-Sn and Au-In is being developed for applications above 300oC. No degradation in die shear strength after 2000 hours at 400oC has been achieved with Au-Sn LTP bonding. Thermocompression bonding of patterned bumps is also being used to achieve even higher temperature capability. Wire bonding – Au and Pt wire (1 mil for SOI and 10 mil for SiC power die) are being investigated. The normal Al bond pads on the SOI are electroless Ni/electroless Au plated, providing a monometallic interface for Au wire bonding. SiC and GaN are typically fabricated with Au wire bond pads. Au wire has better electrical conductivity than Pt, but Pt has better high temperature mechanical strength. Packaging – Individual and multichip packaging is being developed for high temperature applications. These packages are ceramic based to avoid issues with glass-to-metal seals in metal packages. Packaging of Si and SiGe components and circuits for Low Temperature: SiGe devices have been demonstrated to operate at 10oK. The current activities center around developing single and multichip packages that operate over the temperature range from -230oC to +120oC for lunar applications. Substrates – Multilayer copper/polyimide on Si, AlN and Si3N4 substrates are being fabricated and tested for use down to -230oC. A key issue is the CTE match of the material set over the wide temperature range required for the lunar environment. Die attach, wire bonding and flip chip – Indium based die attach is being used with thermosonic gold wire bonding for chip & wire assembly. Indium based solders are also being used for flip chip assembly. Indium remains malleable down to cryogenic temperatures. With a CTE match between the die and the substrate, underfill will not be required. Packaging – Commercially available Al2O3 ceramic packages are being used. AlN packages would provide a better CTE match, but only a very limited number of packages are available as open tooling. A metallized Al2O3 lid has been developed to matcht he CTE of the package. The lid is solder sealed with Pb/In.