Chapter 5

advertisement

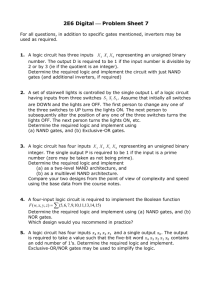

CHAPTER 5 MSI AND PLD COMPONENTS Introduction - - Medium Scale Integration components perform specific digital functions commonly needed in the design of digital systems. A programmable logic device (PLD) is an integrated circuit with internal logic gates that are connected through electronic fuses. o The word programming refers to a hardware procedure that specifies the internal configuration of the device. o The gates in a PLD are divided into an AND array and an OR array that are connected together to provide an AND-OR sum of products. o Programming the device involves the blowing of internal fuses to achieve a desired logic function. o There are three programmable logic devices. o They differ in the placement of fuses in the AND-OR array. Fig. 5 – 1, Page 154. Programmable Read-only Memory (PROM): Has a fixed AND array and programmable fuses for the output OR gates. PROM implements Boolean functions in sum of minterms. Programmable Array Logic (PAL): Has a fused programmable AND array and a fixed OR array. The AND gates are programmed to provide the product terms for the Boolean functions that are logically summed in each OR gate. Programmable Logic Array (PLA): Most flexible, where both AND and OR arrays can be programmed. The product terms in the AND array may be shared by any OR gate to provide the required sum of products implementation. Advantage of using PLDs is: o They can be programmed to incorporate complex logic functions within one LSI circuit. Decoders and Encoders - A decoder is a combinational circuit that converts binary information from n input lines to a maximum 2n unique output lines. If the n-bit decoded information has unused or don’t-care combinations, the decoder output will have fewer than 2n outputs. The decoders presented here are n-to-m-line decoders, where m ≤ 2n. Their purpose is to generate the 2n (or fewer) minterms of n input variables. Example: Consider the 3-to-8-line decoder circuit of Fig. 5-8 page 166. Truth Table of 3-to-8-Line Decoder x Inputs y z D0 D1 D2 Outputs D3 D4 D5 D6 D7 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 - 0 1 0 1 0 1 0 1 0 0 0 0 1 0 0 0 The three inputs are decoded into eight outputs. A particular application of this decoder would be a binary-to-octal conversion. The output line whose value is equal to 1 represents the minterm equivalent of the binary number available in the input line. Ex: Implement a full-adder circuit with a decoder and two OR gates. x y z C S 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 0 1 0 1 1 1 0 1 1 0 1 0 0 1 - We obtain the functions for this combinational circuit in sum of minterms: S (x, y, z) = (1, 2, 4, 7) C (x, y, z) = (3, 5, 6, 7) - Since there are 3 inputs and total of 8 minterms, we need a 3-to-line decoder. Figure 5 – 9 shows the implementation of a full-adder with a decoder. The OR gate for output S forms the sum of minterms 1, 2, 4, and 7. The OR gate for output C forms the sum of minterms 3, 5, 6, and 7. Demultiplexers - It is a circuit that receives information on a single line and transmits this information on one of 2n possible output lines. The selection of a specific output line is controlled by the bit values of n selected lines. Most IC decoders include one or more enable inputs to control the circuit operation. A 2-to-4-line decoder with an enable input constructed with NAND gates is in Fig. 5 – 10, Page 169. All outputs are equal to 1 if enable input E is 1, regardless of the values of inputs A and B. When the enable input is 0, the circuit operates as a decoder with complemented outputs. The X’s under the A and B are don’t-care conditions. Normal decoder operation occurs only when E = 0, and the outputs are selected when they are in the 0 state. Truth Table E A B D0 D1 D2 D3 1 0 0 0 0 X 0 0 1 1 X 0 1 0 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 0 - D0 = 0, complemented outputs D1 = 0, D2 = 0, D3 = 0, If the selection lines AB = 10, output D2 will be the same input value as E, all other outputs are maintained at 1. A decoder with an enable input is referred to as a decoder/demultiplexer because they are obtained from the same circuit. It is the enable input that makes the circuit a demultiplexer. Decoder/demultiplexer circuits can be connected together to form a large decoder ciruit. Encoders - It is a digital circuit that performs the inverse operation of a decoder. - An encoder has 2n (or fewer) input lines and n output lines. - The output lines generate the binary code corresponding to the input value. - Example: An encoder of an octal-to-binary truth table is as follows: - It has eight inputs, one for each of the octal digits, and three outputs that generate the corresponding binary numbers. Truth Table of Octal-to-Binary Encoder Inputs D0 D1 D2 D3 D4 D5 D6 D7 Outputs x y z 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 1 1 1 1 0 1 0 1 0 1 0 1 - - 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 1 1 0 0 1 1 It is assumed that only one input has a value of 1 at any given time. It is implemented with OR gates whose inputs are determined directly from the truth table. When input is 1, 3, 5, 7 output z = 1. When input is 2, 3, 6, 7 output y = 1. When input is 4, 5, 6, 7 output x = 1. Then the Boolean functions are: z = D1 + D3 + D5 + D7 y = D2 + D3 + D6 + D7 x = D4 + D5 + D6 + D7 See Fig. 5 –13 Page 171. Only one input can be active at any given time. If two inputs are active simultaneously, the output produces an undefined combination. Priority order solves the problem. If both D3 and D7 are at the same time, the output will be 111 because D7 has higher priority than D3. Multiplexers - Multiplexing means transmitting a large number of information units over a smaller number of channels or lines. It is abbreviated as MUX. A digital multiplexer is a combinational circuit that selects binary information from one of many input lines and directs it to a single output line. There are 2n input lines and n selection lines whose bit combinations determine which input is selected. A 4-to-1-line is in Fig. 5 –16 Page 174. Each of the four input lines, I0 to I3, is applied to one input of an AND gate. Selection lines s1 and s0 are decoded to select a particular AND gate. The table lists the input-to-output path for each possible bit combination of the selection lines. Function Table s1 0 0 1 1 - - s0 0 1 0 1 Y I0 I1 I2 I3 Fig. 5 – 16 (c), shows the MSI function that is used in the design of a digital system. Ex: If s1 s0 = 10, then AND gate is associated with input I2 has two of its inputs equal to 1 and the third input is connected to I2. The other three AND gates have at least one input equal to 0, which makes their outputs equal to 0. The OR gate output is now equal to the value of I2, thus providing a path from the selected input to the output. A multiplexer is also called a data selector, since it selects one of many inputs and steers the binary information to the output line. A 2n-to-1-line MUX is constructed from an n-to-2n decoder by adding to it 2n input lines, one to each AND gate. The output of the AND gates are applied to a single OR gate to provide the 1-line output. It is then implied that it also contains n selection lines. A MUX may have an enable input to control the operation of the unit. When the enable unit is in a given binary state, the outputs are disabled. The enable input sometimes called strobe, which can be used to expand two or more multiplexers to a digital multiplexer with a large number of inputs. Read Only Memory (ROM) - It is a device that includes a decoder and the OR gates within a single IC package. Essentially a memory device in which permanent binary information is stored. The binary information must be specified by the designer and then is embedded in the unit to form the interconnected pattern. ROMs are programmed for a specific configuration. Its contents remain intact even if the power is off. Fig. 5 – 21 Page 181 shows its block diagram. It consists of n input lines and m output lines. Each bit combination of the input variables is called an address. Each bit combination of the output lines is called a word. The number of bits per word is equal to the number of output lines, m. An address is a binary number that denotes one of the minterms of n variables. The number of distinct addresses possible with n input variables is 2n An output word can uniquely be selected by a unique address, and since there are 2n distinct addresses in a ROM, there are 2n distinct words that are said to be stored in the unit. - Ex: a 32 X 8 ROM consists of 32 words and of 8 bits each. This means there are 8 output lines and that there are 32 distinct words stored in the unit, each of which may be applied to the output lines. There are 5 input lines in a 32 X 8 ROM because 25 = 32, and with 5 variables, we can specify 32 addresses or minterms. If the input address is 00000, word number 0 is selected and appears on the output lines. If the input address is 11111, word number 31 is selected and appears on the output lines. There are 30 other addresses that can select the other 30 words. - ROM is sometimes specified by the total number of bits it contains, which is 2 n X m. Ex: a 2048-bit ROM may be organized as 512 words of 4 bits each. It means that the unit has 9 input lines and 4 output lines to specify 29 = 512 words. - Fig. 5 –22 Page 182 shows the internal logic construction of a 32 X 4 ROM. o The five input variables are decoded into 32 lines by means of 32 AND gates and five inverters. o Each output of the decoder represents one of the minterms of a function of 5 variables. o Each one of the 32 addresses selects one and only one output from the decoder. o The address is a 5-bit number applied to the inputs, and the selected minterm out of the decoder is the one marked with the equivalent decimal number. o The 32 outputs of the decoder are connected through fuses to each or gate. o Each OR gate has 32 inputs. Ex: Design a combinational circuit using a ROM. The circuit accepts a 3-bit number and generates an output binary number equal to the square of the input square. - First derive the Truth Table for the combinational circuit. Inputs A2 A1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 - A0 0 1 0 1 0 1 0 1 B5 0 0 0 0 0 0 1 1 B4 0 0 0 0 1 1 0 1 Outputs B3 B2 0 0 0 0 0 1 1 0 0 0 1 0 0 1 0 0 B1 0 0 0 0 0 0 0 0 B0 0 1 0 1 0 1 0 1 Decimal 0 1 4 9 16 25 36 49 3 inputs and 6 outputs are to needed to accommodate all possible numbers. Output B0 is always equal to A0; so there is no need to generate B0 with a ROM since it is equal to an input variable. Output B1 is always equal to 1, so this output is always known. - The minimum size ROM needed must have 3 inputs and four outputs. Three inputs specify 8 words; so ROM size must be 8 x 4. The truth table below specifies all the information needed for programming the ROM. ROM Truth Table A2 A1 A0 F1 F2 F3 F4 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 1 1 0 0 0 0 1 1 0 1 0 0 0 1 0 1 0 0 0 0 1 0 0 0 1 0 - The block diagram is shown in Fig. 5 – 24 (b) page 185. Programmable Logic Array (PLA) - A block diagram is shown in Fig. 5 – 25. It consists of n inputs, m outputs, k product terms, and m sum terms. - PLA doesn’t provide full decoding of the variables and doesn’t generate all the minterms as in the ROM. - The product terms constitute a group of k AND gates and the sum terms constitute a group of m or gates. - The size of the PLA is specified by the number of inputs, the number or product terms, and the number of outputs (the number of sum terms is equal to the number of outputs.) - A typical PLA has 16 inputs, 48 product terms, and 8 outputs. - The number of programmed fuses is 2n x k + k x m + m whereas that of ROM is 2n X m. - Fig. 5 – 26 shows the internal construction of a specific PLA. It has 3 inputs, three product terms, and two outputs. PLA program Table - It is superior to ROM for circuits that have a large number of don’t-care conditions. - Ex: Consider the truth table of the combinational circuit, shown in Fig. 5 – 27 (a). - The simplified functions in sum of products are obtained from the maps of Fig. 5 – 27 (b). - There are 3 distinct terms in this combinational circuit: AB’, AC, and BC. - The circuit has three inputs and two outputs; so the PLA of Fig. 5 – 26 can be used to implement this combinational circuit. - The PLA program table is shown in Fig. 5 – 27 (c). - The first column lists the product terms numerically. - The second column specifies the required paths between inputs and AND gates. The third column specifies the paths between the AND gates and the OR gates. Under each output variable, we write a T (for true) if the output inverter is to be bypassed, and C (for complement) if the function is to be complemented with the output inverter. Ex: A combinational circuit is defined by the functions F1 (A, B, C) = (3, 5, 6, 7) F2 (A, B, C) = (0, 2, 4, 7) Implement the circuits with PLA having three inputs, four product terms, and two outputs. 00 01 0 11 10 1 1 1 1 1 01 11 10 F1 = AC + AB + BC 00 0 1 1 1 1 F2 = B’C’ + A’C’ + ABC 0 1 00 01 0 0 11 10 0 1 0 F’1 = B’C’ + A’C’ + A’B’ 00 01 11 0 0 0 1 0 10 0 F’2 = B’C + A’C + ABC PLA program Table Product Term B’C’ 1 A’C’ 2 A’B’ 3 ABC 4 A 0 0 1 Inputs B 0 0 1 C 0 0 1 Outputs F1 F2 1 0 1 0 1 1 C T T/C PROGRAMMABLE ARRAY LOGIC (PAL) - Fig. 5 – 29 shows the conventional and array logic symbols for a multiple-input AND gate. - The PAL is a programmable logic device with a fixed OR array and a programmable AND array. - Because only the AND gates are programmable, the PAL is easier to program, but is not flexible as the PLA. - Figure 5-30 shows the logic array configuration of a typical PAL. - It has 4 inputs and 4 outputs. Each has a buffer and an inverter gate. - There are 4 sections in the unit, each being composed of a three wide AND-OR array. - This is the term used to indicate that there are three programmable AND gates in each section and one fixed OR gate. - Each AND gate has 10 fused programmable inputs. - Unlike the PLA, a product term cannot be shared among two or more OR gates. - Therefore, each function can be simplified by itself without regard to common product terms. - The number of product terms in each section is fixed, and if the number of the terms in the function is too large, it may be necessary to use two sections to implement one Boolean function. - Ex: Using a PAL in the design of a combinational circuit, consider the following Boolean functions given in sum of minterms: w(A, B, C, D) = (2, 12, 13) x (A, B, C, D) = (7, 8, 9, 10, 11, 12, 13, 14, 15) y (A, B, C, D) = (0, 2, 3, 4, 5, 6, 7, 8, 10, 11, 15) z (A, B, C, D) = (1, 2, 8, 12, 13) 00 A A 00 01 11 10 1 01 C 11 C 10 1 B B 1 D D 01 C 11 1 1 D 1 1 1 D w = ABC’ + A’B’CD’ 00 A A x = A + BCD 00 01 11 10 1 1 C 10 1 1 B B A A 00 01 11 10 00 1 1 01 1 1 D C 11 1 1 1 1 D C 10 1 1 C 11 C 10 1 B B 1 y = A’B + CD + B’D’ 00 A A 00 01 11 10 01 1 1 1 1 D z = ABC’ + A’B’CD’ + AC’D’ + A’B’C’D’ = w + AC’D’ + A’B’C’D - B B D The table below shows the PAL programmable table for the 4 Boolean functions. PAL Programmable Table Product Term A AND Inputs B C D W 1 2 3 1 0 - 1 0 - 0 1 - 0 - - w = ABC’ + A’B’CD’ 4 5 6 1 - 1 - 1 - 1 - - x=A + BCD 7 8 9 0 - 1 0 1 - 1 0 - y = A’B’ + CD + B’D’ 10 11 12 1 0 0 0 0 0 1 1 - z=w + AC’D’ + A’B’C’D Outputs - The table is divided into 4 sections with three products in each. The first two sections need only two product terms to implement the Boolean function. The last two sections need three product terms. (Function w was reduced to 3 terms.) The fuse map is shown in Fig. 5 – 31. For each 1 or 0 in the table, we mark the corresponding intersection in the diagram with the symbol for an intact fuse. For each dash, we mark the diagram with blown fuses in both the true and complement inputs. If the AND gates is not used, we leave its input fuses intact.