Implementation of Low Power Consuming Hybrid CMOS

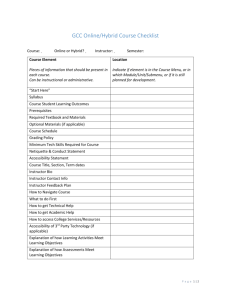

International Journal of Science, Engineering and Technology Research (IJSETR) Volume , Issue , Implementation of Low Power Consuming Hybrid CMOS-SET Devices for Stair Case Lighting: A Case Study for Decision Making Subsystems Dr. Jayanta Gope, Sanjay Bhadra, Md Wasim Reja, Aquil Peyami Abstract— Single Electronic Device (SED) promises massive revolution in turning ‘Mesophysics’ into ‘actuality’ and have paved its path in the field of next gen nano device technology. No doubt, that the future would appreciate the privilege of nano-scale devices with the invasion of SET over CMOS. With the very inception of this technology Researchers now articulate the art of fabrication of electronic devices in tiny die area generating extreme low power consumption and thereby shrinking the device size to nano region. Researchers now emphasize to incorporate this technology in consumer electronics. The tunneling technology of SET is endorsed into Single Electron Devices at present. But amid all fabrication of SET has been shortly hampered owing to the lacking of stipulated fabrication of SET in room temperature environment. Precisely the Researchers are in a frame of mind to incorporate a hybrid structure of CMOS and SET. The MIB model in this regard is eminent. Moreover the initialization of MIB modeling has intrinsically mothered Hybrid CMOS-SET based logic realizations which are considered as an alternative of CMOS technology. Concurrently, Researchers are piloting the human brains decision-making capability into chip designing metaphor. Here the authors empirically demonstrated one such course of action in this study. The simple case study of stair-case-lighting has been enunciated based on the decision-making competency. The letter proposes a novel architecture of Hybrid CMOS SET based stair-case-lighting nano IC. Index Terms—SET, SED, Hybrid CMOS-SET, MIB, Decision Making. I. INTRODUCTION SED is anticipated as effectively flourishing Technology in contemporary electronics with modern physical effects of electron charge transport. It renders countless development in device integrity [1-16]. But to the contrary of all good things SET possess numerous open challenges for the future sophisticated solutions. Size reduction physiognomies of SEDs stemmed to be blessings; reasonably it is not anonymity Manuscript received. Dr. Jayanta Gope, Department of ECE, Camellia School of Engg and Tech,, Barasat, West Bengal University of Technology (e-mail: jayantagope.etce..ju@gmail.com). Kolkata, India, +91 9831205967 Mr. Sanjay Bhadra Department of EE, Camellia School of Engg and Tech,, Barasat, West Bengal University of Technology Kolkata, India, Md Wasim Reja, Department of EEE, Camellia School of Engg and Tech,,Barasat, West Bengal University of Technology. Kolkata, India, Aquil Peyami, Department of EEE, Camellia School of Engg and Tech,, Barasat, West Bengal University of Technology Kolkata, India, as no amount of compromise was introduced in the performance of the devices. It confines all virtue of large scale electronic circuits that consist in modern era. The simple structure ensures that it utilizes the chance to manipulate the movement and position of a single electron or a fewer number of electrons. The straightforward circuit formation demonstrates single electron charging effects in the single electron box; more conveniently a metal granule having 1nm thick insulator in the middle. Chronically it is referred as the tunnel junction that attaches a metal granule in one side of the surface. It is the phenomenal strategy of SET that the electrons can liberally tunnel in and tunnel out from the tunnel junction. Owing to such indispensable heights, SED structures popularized as the most likely contender for imminent ULSI circuits. Already many reports on SET suggested that the future is of SED based nano electronics. But apparently fabrication of SET is not a cup of tea. The major shortcomings are (i) low gain, (ii) the high output impedance and (iii) the background charges. Unlikely, SETs have high output impedance as well as they are sensitive to random background charges. This are stipulated confinements of SET and such are raffled with other large scale fabrication problems and it is anticipated that whether SETs will take over FETs in applications where large voltage gain or low output impedance is necessary. Such hindrances have catastrophically bothered the device scientists worldwide; it is now in the hands of time to some extent and thus it has to go under extensive research before commercially designing a SET based dense integrated circuits using the existing lithography technique. Scientists are made to bother once again about the ample substitution of CMOS by SET in very near future [17 and 18]. Necessity is the mother of all inventions - to overcome intrinsic limitations and difficulties of SET fabrication, scientists have reconnoitered a novel perception of ‘Hybrid CMOS-SET'; they amended the fundamental topology of SET by combining CMOS with SET it to transport new functionalities of electron which clues to better device manufacturing. Such incorporations prolific the pathway in device research to transform CMOS to SET in present context. The conception of hybrid CMOS-SET modeling is in its elementary stage but even though empirical studies initiated both in industry and academia and have by now marked its way. Accordingly, Toshiba validated the presentation of a hybrid MOS-SET inverter [19] which 1 All Rights Reserved © 2012 IJSETR International Journal of Science, Engineering and Technology Research (IJSETR) Volume , Issue1, steered new likelihood of hybridization in low power VLSI design. The authors here have limited themselves in incorporating this new technology in brain mapping to obtain simplest decision making ICs. That is why the staircase is considered here for easement. The authors hereby humbly submit that more complex decision making algorithms can be considered using the same device. II. HYBRID CMOS-SET CO-INTEGRATION Major scientific publications exposed the raw truth for the coming decades, i.e., existing CMOS that ranges in 100 nm will be forced to share its present dominance with SETs in next generation ICs [20] although CMOS and SETs are relatively converse in nature. SET by nature is a low-power consuming device [21 and 22]. It demonstrates higher speed and robustness along with high integration density like advanced new functionalities. To the contrary CMOS possess unbeatable characteristics like high voltage gain no background charge. Thus CMOS is blessed to compensate exactly the intrinsic limitations of SETs. And so, combining and hybridizing of SET and CMOS is likely to usher new functionalities [23 and 24] in next generation device technology. To exploit SET to function as a switch it is customary to push the SET into the Coulomb blockade state i.e., the ‘OFF’ condition and accordingly channel it to conduct current i.e., the ‘ON’ condition. Once done, it is ready to mimic MOSFET like logic realization to model a hybrid CMOS-SET logic family. The straight forward design approach is that the hybrid CMOS-SET threshold logic is formed by a PMOS transistor as the load resistance of an SET. Worth stating that these devices has PMOS transistor connected as a load to the SET which is typically distinct from any other evolved post CMOS devices. Thus some design rules has been set by Researchers and that is exclusively implied before practical hybrid CMOS-SET circuit demonstration. Eventually the novel structures resemble CMOS inverter, but there are two basic metamorphoses, i.e., (i) the ‘Pull Up’ transistor is nothing but a composite SET structure and (ii) the VDD is defined by the SET device parameters. A SET-MOS quaternary transmission gate [25] is highly accredited and mostly cited in reputed journals. Researchers at Delft University in Netherlands proposed a SPICE simulation package for SET circuit [26] using the Orthodox theory. The authors include some of the orthodox logic gates made up of Hybrid CMOS-SET structures for the clarifications of their proposed design of nano IC in Fig 1 to 3. III. DECISION MAKING IN STAIRCASE SWITCHING A staircase is controlled by two switches, one at the top of the stairs, and another, at the bottom of the stairs. Let Switch1 and Switch 2 be the two corresponding switches, representing the state ‘0’ and ‘1’. The lamp is to be lighted with the operations of Switch 1 and Switch 2. It is clear that this lamp glows i.e., it is ON at state ‘1’ and OFF in state ‘0’. The maneuver is tabled in table-1. Table-1 Table for staircase switching Switch1 0 0 1 1 Switch2 0 1 0 1 Light up 0 1 1 0 The authors have derived the logic realization given by Light up = Switch 1 Switch2 Switch1 .Switch2 As per the conditions enumerated there persist two levels of realizations only, thus the authors adhered in reducing the number of logical states for simple implementation. Furthermore, this adds up making the circuit least costly and more effective. IV. PROPOSED HYPOTHETICAL ARCITECTURE OF IC OF THE STAIRCASE SWITCHING The proposed model comprise of 11 CMOS transistors and 11 SETs lying in situ in a nano region. The modus operandi of the model cultivates the MIB orthodox theory. The robustness of the circuit largely relies upon straightforward architecture and the authors here mobilized the circuit configuration in a dedicated way. All the interfacings were deliberately articulated and was periodically endorsed so that highest amount of merits of the Hybrid CMOS-SET architecture can be achieved in designing this particular decision making algorithm. This painstaking task was lastly put forward for corroboration. The diagram is depicted in Fig.4. V. RESULT AND DISCUSSION The proposed model is validated using MIB compact model as per AHDL for SET simulation and BSIM 4.6.1 is used to simulate CMOS transistor in tanner periphery. The resistance R (TD&TS) for SET is considered to be 1MΩ. The capacitance C (TD & TS) is equal to 0.1aF and the CL1 and CL2 is considered to be 0.27aF and 0.125aF respectively. For easement and clarity the logic 0 is typically 0V and logic 1 is 0.8V and the V g is limited to the value of logic 1 i.e., 0.8V. In case of the CMOS the Vdd is -220mV whereas W/L ratio is approximated to 100nm/65nm. Besides, other strategically design specs are kept identical to the default values of BSIM 4.6.1. The logic operation that occurs periodically exhibits the switching ON and OFF conditions of Switch1 and Switch2.The output of the proposed model resembles that only when either Switch1 or Switch 2 is ON the lighting takes place. But in no other conditions the staircase is lightened. Such phenomenon is quite linear to general consideration of decision making. Hereby the authors report the highest probability of logical operations being perfectly realized using advanced low power consuming dedicated Hybrid CMOS-SET device configuration. For more complexity the same model can be utilized with increased number of inputs. The power consumptions and power dissipation of the proposed model is tabled in Table 2 for perusal. 2 All Rights Reserved © 2012 IJSETR International Journal of Science, Engineering and Technology Research (IJSETR) Volume , Issue , TABLE 2 POWER DISSIPATION OF SET-MOS HYBRID CIRCUITS Circuit type Power Supply No. of SET Power Dissipation 0.01V No. of MO S 3 AND Gate OR Gate NOT Gate 3 1.02E-09 W 0.01V 3 3 1.02E-09 W 0.01V 1 1 [13] [14] [15] 1.02E-09 W [16] [17] VI. CONCLUSION This letter investigated the implementation of hybrid CMOS-SET logic gates comprising of single electron MOS transmission logic gates. The motivation was to incorporate this novel device architecture in decision making operations. Staircase switching is quite simple but possess maximum amount of reality in case of decision making. Thereby the authors intended to optimize the logical renderings offered by hybrid CMOS-SET in staircase switching. Computer simulation revealed perfect logical operations of the designed circuit. The outcomes are in good agreement with the conventional CMOS switching. Rather comparative study revealed enhanced performance which pathways complex decision making arrangements to be incorporated in near future based on Hybrid CMOS-SET devices. REFERENCES [18] [19] [20] [21] [22] [23] [24] M. A. Kastner, “The single electron transistor and artificial atoms”, Ann. Phy. (Leipzig), vol. 9, pp. 885-895, 2000. [2] Amiza Rasmi & Uda Hashim “Single-electron transistor (SET): Literature Review” journal 2005, Koieg University, Malaysia. [3] K. K. Likharev : IBM J. Res. Devel., vol 32 , 144 , 1988 [4] Kawarabayashi, J. ; Kadoi, T. ; Watanabe, K.-I. ; Uritani, A. ; Iguchi, T., “Single electron transistor for cryogenic detector read-out”, IEEE Nuclear Science Symposium Conference Record, 2001 [5] Morris, J.E. ; Wu, F. ; Radehaus, C. ; Hietschold, M. ; Henning, A. ; Hofmann, K. ; Kiesow, A., “Single electron transistors: modeling and fabrication”, 7th International Conference on Solid-State and Integrated Circuits Technology, 2004. [6] Teruhisa Matsui, Jun Kawarabayashi, Kenichi Watanabe and Tetsuo Iguchi, “Evaluation of Single-Electron Transistor as Nanoscale Thermometer for a Cryogenic Radiation Detector”, Journal of NUCLEAR SCIENCE and TECHNOLOGY, Supplement 6, pp. 73–77 September 2008. [7] P. Hadley, G. Lientschnig, and M. Lai, “Single-Electron Transistors,” pp. 1–8. [8] Liu, R.S. ; Pettersson, H. ; Suyatin, D. ; Michalak, L. ; Canali, C.M. ; Samuelson, L., “Nanoscaled ferromagnetic single-electron transistors”, 7th IEEE Conference on Nanotechnology, 2007. IEEE-NANO 2007. [9] Daw Don Cheam ; Karre, P.S.K. ; Palard, M. ; Bergstrom, P.L., “Mass Production of Room Temperature Single Electron Transistors using Step & Flash Imprint Lithography and Lift-Off Technique”, 8th IEEE Conference on Nanotechnology, 2008. NANO '08. [10] Yaqing Chi ; Bingcai Sui ; Liang Fang ; Zhou Hailiang ; Haiqing Zhong ; He Sun, “A compact analytical model for multi-island single electron transistors”, IEEE 8th International Conference on ASIC, 2009. ASICON '09. [11] Haiqin Zhong ; Yaqing Chi ; He Sun ; Chao Zhang ; Liang Fang, “Macromodeling of realistic single electron transistors for large scale [1] [12] [25] [26] circuit simulation”, 3rd International Nanoelectronics Conference (INEC), 2010 Xiaobao Chen ; Zuocheng Xing ; Bingcai Sui, “A model for energy quantization of single-electron transistor below 10nm”, IEEE 9th International Conference on ASIC (ASICON), 2011. Ono, Y. ; Takahashi, Y., “Single-electron pass-transistor logic and its application to a binary adder” Symposium on VLSI Circuits, 2001. Digest of Technical Papers. 2001. Dae Hwan Kim ; Suk-Kang Sung ; Kyung Rok Kim ; Jong Duk Lee ; Park, Byung-Gook, “Single-electron transistors based on gate-induced Si island for single-electron logic application”, IEEE Transactions on Nanotechnology,2002. Degawa, K. ; Aoki, T. ; Higuchi, T. ; Inokawa, H. ; Takahashi, Yasuo, “A single-electron-transistor logic gate family and its application - Part I: basic components for binary, multiple-valued and mixed-mode logic”, 34th International Symposium on Multiple-Valued Logic, 2004. Lageweg, C. ; Cotofana, S. ; Vassiliadis, S., “Binary addition based on single electron tunneling devices” 4th IEEE Conference on Nanotechnology, 2004. Eugene S Soldatov, Vladimir V Khanin, Artem S Trifonov, Sergei P Gubin, V V Kolesov, D E Presnov, S A Iakovenko, G B Khomutov and A N Korotkov, “Room temperature molecular single-electron transistor”, Eugene S Soldatov et al 1998 Phys.-Usp. 41 202. Y. Takahashi, et. al, “Silicon single-electron devices,” Journal of physics: Condensed matter, pp.R995-R1033, 2002. Uchida, K., et al., “Programmable Single-Electron Transistor Logic for Future Low-Power Intelligent LSI: Proposal and Room-Temperature Operation,” IEEE Trans. Elec. Dev., Vol. 50, No. 7, pp. 1623–1630, 2003. A.M. lonescu, M. Declercq, S. Mahapatra, K. Banejee, J. Cautier, “Few electron devices: towards hybrid CMOS-SET integrated circuits”, DAC2002, pp. 88-93. S. Mahapatra, A.M. lonescu, K. Banejee, M.J.Declerq, “Modelling and analysis of power dissipation in single electron logic”, Technical Digest of lEDM 2002. K. Uchida, 1. Koga, R. Ohba, A. Toriumi, “Programmable single-electron transistor logic for low-power intelligent Si LSI”, ISSCC 2002, Vol. 2, pp. 162453. H. Inokawa, A. Fujiwara, Y. Takahashi, “A multiple-valued logic with merged single electron and MOS transistors” IEDM 2001, pp. 147-150. M. Goossens, “Analog neural networks in single-electron tunneling technology”, Dell? University Press, Nederlands. Santanu Mahapatra and Adrian Mihai Ionescu “Realization of multiple valued logic and memory by hybrid SETMOS architecture” IEEE transactions on Nanotechnology, Vol. 4, No. 6, November 2005. G.Lientsching, I.Weymann and P.Hadley “Simulating Hybrid Circuits of Single Electron Transistors and Field Effect Transistors” – Japanese Journal of Applied Physics, vol. 42, pp 6467 – 6472, 2003. Dr. Jayanta Gope, PhD (Engg.), & Chartered Engineer has received his PhD Degree in Nanotechnology from Jadavpur University, Kolkata and is presently associated with Camellia School of Engineering and Technology. His field of interest includes Nano device modeling, Single Electronic devices, Spintronic Devices, Hybrid CMOS-SET. He has already published around 40 International research articles in this category. He is nominated as Editorial Board Member and Reviewer of some esteemed Journals and is guiding 4 PhD Scholars in the field of Nanotechnology. He is a life Member of ‘CE’& ‘ISCA’. Mr. Sanjay Bhadra,(M.E-Elect Control-JU),MBA(IT-JU) MIE,MIETE is presently associated as Asst.Prof(EE) in Camellia School of Engineering and Technology. He has active interest in Signal processing and nano devices. Mr. Md Wasim Reja, is a final year student of B.Tech in Electrical and Electronics Engineering Department of Camellia School of Engineering and Technology, West Bengal, India. Mr. Aquil Peyami is a final year student of B.Tech in Electrical and Electronics Engineering Department of Camellia School of Engineering and Technology, West Bengal, India. 3 All Rights Reserved © 2012 IJSETR International Journal of Science, Engineering and Technology Research (IJSETR) Volume , Issue1, LIST OF FIGURES Fig.1 Hybrid CMOS-SET based OR realization Fig.2 Hybrid CMOS-SET based NOT realization Fig.3 Hybrid CMOS-SET based AND realization Fig.4 Hybrid CMOS-SET based staircase switching IC 4 All Rights Reserved © 2012 IJSETR

0

0

No more boring flashcards learning!

Learn languages, math, history, economics, chemistry and more with free StudyLib Extension!

- Distribute all flashcards reviewing into small sessions

- Get inspired with a daily photo

- Import sets from Anki, Quizlet, etc

- Add Active Recall to your learning and get higher grades!

Related documents

Add this document to collection(s)

You can add this document to your study collection(s)

Sign in Available only to authorized usersAdd this document to saved

You can add this document to your saved list

Sign in Available only to authorized users