Electronics Exercises & Examples: Introduction & Diodes

advertisement

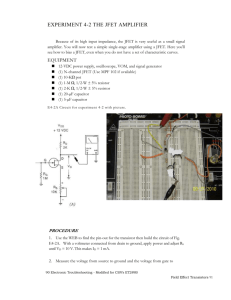

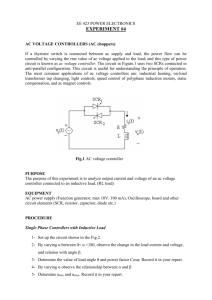

Chapter 1 Introduction to electronics 題庫內附圖(Fig)編號與電子學課本相同,請參考課本 EXERCISES 1. For the signal-source representations shown in Figs.1.1 (a) and 1.1(b), what are the open -circuit output voltages that would be observed? If, for each, the output terminals are short-circuited (i.e., wired together),what current would flow? For the representations to be equivalent, what must the relationship be between vs ,is, and Rs? 2. Find the frequencies ƒ and ω of a sine-wave signal with a period of 1 ns. 3. The UHF (Ultra High Frequency) television broadcast band begins with channel 14 and extends from 470 MHZ to 806MHZ. If 6 MHZ is allocated for each channel, how channels can this band accommodate? 4. Consider a 4-bit digital word D = b3b2b1b0 (see Eq.1.3) used to represent an analog signal VA that varies between 0V and +15V. (a) Give D corresponding to VA = 0V, 1V,2V, and 15V (b)What change in VA causes a change from 0 to 1in: (i)b0,(ii)b1,(iii)b2,and(iv)b3? (c) If VA = 5.2 V, what do you expect D to be? What is the resulting error in representation? 5. An amplifier operating from a single 15V supply provides a 12V peak-to -peak sine-wave signal to a 1kΩ load and draws negligible input current from the signal source. The dc current drawn from the 15V supply is 8mA.What is the power dissipated in the amplifier, and what is the amplifier efficiency? 6. A transducer characterized by a voltage of 1 V rms and a resistance of 1 MΩ is available to drive a 10-Ω load. If connected directly, what voltage and power levels result at the load? If a unity-gain ( i.e., Avo = 1) buffer amplifier with 1-MΩ input resistance and 10-Ω output resistance is interposed between source and load, what do the output voltage and power levels become? For the new arrangement find the voltage gain from source form source to load, and the power gain ( both expressed in decibels ). 7. An amplifier with a voltage gain of +40 dB, an input resistance of 10 kΩ, and an output resistance of 1kΩ is used to drive a 1-kΩ load. What is the value of Avo? Find the value of power gain in dB. 8. For the cascade amplifier of Example 1.3, let VS be 1 mV. Find Vi1, Vi2, Vi3, and VL. 9. Consider a current amplifier having the model shown in the second row of Table 1.1. Let the amplifier be fed with a signal current-source is having a resistance Rs, and let the output be connected to a load resistance RL. Show that the overall current gain is given by 10. Consider a transresistance amplifier having the model shown in the third row of Table 1.1. Let the amplifier be fed with a signal current-source is having a resistance Rs, and let the output be connected to a load resistance RL. Show that the overall current gain is given by 11. Consider a voltage amplifier having a frequency response of the low-pass STC type with a dc gain od 60 dB and a 3-dB frequency of 1000Hz. Find the gain in dB at ƒ=10 Hz, 10kHz,100kHz, and 1MHz. 12. Consider the situation illustrated in Fig. 1.27. Let the output resistance of the first voltage amplifier be 1kΩ and the input resistance of the second voltage amplifier (including the resistor shown) be 9kΩ. The resulting equivalent circuit is shown in Fig.E1.23 where Vs and Rs are the output voltage and output resistance of the first amplifier, C is coupling capacitor, and Ri is the input resistance of the second amplifier. Convince yourself that V2/Vs is a high-pass STC function. What is the smallest value for C that will ensure that the 3-dB frequency is not higher100 Hz? 13. Find the dynamic power dissipated in an inverter operated from a 5V power supply. The inverter has a 2pFcapacitance load and is switched at 50MHz. EXAMPLES 1. Consider an amplifier operating from ±10V power supplies. It is fed with sinusoidal voltage having 1V peak and delivers a sinusoidal voltage output of 9V peak to a 1kΩ load. The amplifier draws a current of 9.5mA from each of its two power supplies. The input current of the amplifier is found to be sinusoidal with 0.1mA peak. Find the voltage gain, the current gain, the power gain, the power drawn from the dc supplies, the power dissipated in the amplifier, and the amplifier efficiency. 2. Figure 1.18 depicts an amplifier composed of a cascade of three stages. The amplifier is fed by a signal source with a source resistance of 100kΩ and delivers its output into a load resistance of 100Ω. The first stage has a relatively high input resistance and a modest gain factor of 10. The second stage has a higher gain factor but lower input resistance. Finally, the last, or output, stage has unity gain but a low output resistance. We wish to evaluate the overall voltage gain, that is, vL/vS, the current gain, and the power gain. 3. Figure 1.25 shows a voltage amplifier having an input resistance R i, an input capacitance Ci, a gain factor μ , and an output resistance Ro. The amplifier is fed with a voltage source Vs having a source resistance Rs, and a load of resistance RL is connected to the output. (a) Derive an expression for the amplifier voltage gain Vo/Vs as a function of frequency. From this find expression for the dc gain and the 3-dB frequency. (b) Calculate the values of the dc gain, the 3-dB frequency, and the frequency at which the gain becomes 0dB (i.e., unity) for the case Rs = 20kΩ, Ri = 100 kΩ, Ci = 60 pF, μ = 144V/V, Ro =200 Ω, and RL = 1 kΩ. (c) Find vo(t) for each of the following inputs: (i) vi = 0.1 sin 102 t,V (ii) vi = 0.1 sin 105t,V (iii) vi = 0.1 sin 106t,V (iv) vi = 0.1 sin 108 t,V Chapter 3 Diodes 題庫內附圖(Fig)編號與電子學課本相同,請參考課本 EXERCISES 1. For the circuit in Fig. 3.3(a), sketch the transfer characteristic υO versus υ I. 2. In the circuit of Fig. 3.3(a), let υI have a peak value of 10V and 10V and R = 1 kΩ. Find the peak value of iD and the dc component of υO. 3. Figure E3.5 shows a v for an ac voltmeter .It utilizes a moving-coil meter that gives full-scale reading when the input average current flowing through it is 1mA. The sine-wave voltage moving-coil meter has a 50-Ω resistance. Find the value of R that result in the meter indicating a full-scale reading when the input sine-wave voltage υI is 20V peak-to-peak. (Hint: The average value of half-sine waves is VP/Π.) 4. A silicon junction diode with n =1 has υ = 0.7V at I = 1mA. Find the voltage drop at I = 0.1 mA and I = 10 mA. 5. The diode in the circuit of Fig. E3.9 is a large high-current device whose reverse leakage is reasonably independent of voltage. If V = 1 V at 20℃, find the value of V at 40℃ and at 0℃. 6. Consider a diode that is 100 times as large ( in junction area) as that whose characteristics are displayed in Fig.3.12. If we approximate the characteristics in a manner similar to that in Fig. 3.12 (but over a current range 100 times as large), how would the model parameters VD0 and rD change? 7. Repeat Exercise 3.4 using the 0.7-V-drop model to obtain better estimates of I and V than those found in Exercise 3.4 (using the ideal- diode model). 8. Consider a diode with n = 2 biased at 1 mA. Find the change in current as a result of changing the voltage by (a) -20mV , (b) -10mV, (c) -5mV, (d) +5mV, (e) +10mV, and (f) +20mV. In each case, do the calculations (i) using the small-signal model and (ii) using the exponential model. 9. A zener diode whose nominal voltage is 10V at 10mA has an has an incremental resistance of 50Ω. What voltage do you except if the diode current is halved? Doubled? What is the value of VZO in the zener model? 10. A shunt regulator utilizes a zener diode whose voltage is 5.1V at a current of 50mA and whose incremental resistance is 7Ω. The diode is fed from a supply of 15-V nominal voltage through a 200Ω resistor. What is the output voltage at no load? Find the line regulation and the load regulation. 11. For the full-wave rectifier circuit in Fig. 3.26(a), neglecting the effect of rD, show the following : (a) The output is zero for an angle of sin -1(VD/VS) centered around the zero-crossing points of the sine- wave input. (b) The average value (dc component) of υO is VO≒(2/π)Vs-VD. (c) The peak current through each diode is (Vs-VD)/R. Find the fraction (percentage) of each cycle during which υO > 0, the value of VO, the peak diode current, and the value of PIV, all for the case in which υs is a 12-V (rms) sinusoid, VD ≒ 0.7V, and R =100Ω. 12.Derive the expressions in Eqs.(3.33),( 3.34),and(3.35). 13.Consider the operational rectifier or superdiode circuit of Fig. 3.31(a), with R = 1 kΩ. For υI = 10mV, 1V, and -1V ,what are the voltage that result at the rectifier output and at the output of the op amp? Assume that the op amp is ideal and its output saturation at ±12V. The diode has a 0.7-V drop at 1-mA current, and the voltage drop changes by 0.1V per decade of current change. 14. Assuming the diodes to be ideal, the transfer characteristic of the circuit shown in Fig.E3.27. 15. Calculate the intrinsic carrier density ni at 250K,300K, and 350K. 16. Find the resistivity of (a) intrinsic silicon and (b) p-type silicon with NA = 1016 /cm3. Use ni =1.5×1010/ cm3, and assume that for intrinsic silicon μn = 1350 cm2 /V.s. (Note that doping results in reduced carrier mobilites.) 17. For a pn junction with NA = 1017/ cm3 and ND = 1016 /cm3, operating at T = 300K, find (a) the value of Cjo per unit junction area (μm2 is a convenient unit here) and (b) the capacitance Cj at a reverse-bias voltage 0f 2 V, assuming a junction area of 2500cm2 . Use ni =1.5×1010/ cm3, m=0.5, and the value of VO found in Exercise 3.32 (VO = 0.728V). 18. Use PSpice investigate the operation of the voltage doubler whose Capture schematic is shown in Fig.E3.35(a). Specifically, plot the transient behavior the voltages υ2 and υout when the input is a sinusoid of 10-V peak and 1-kHz frequency. Assume that the diodes are of the 1N4148 type ( with Is = 2.682 nA, n= 1.836,Rs =0.5664Ω, Vo= 0.5V, Cjo =4pF, m = 0.333, ιT =11.54 ns, VZK = 100V,IZK = 100μA). EXAMPLES 1. Figure 3.4(a) shown a circuit for charging a 12-V battery. If υs is a sinusoid with 24-V peak amplitude, find the fraction of each cycle during which the diode conducts. Also, find the peak value of the diode current and the maximum reverse-bias voltage that appears across the diode. 2. A silicon diode said to be a 1-mA device display a forward voltage of 0.7V at a current of 1mA. Evaluate the junction scaling constant Is in the event that n is either 1 or 2. What scaling constants would apply for a 1-A diode of the same manufacture conducts 1 A at 0.7V? 3. Repeat the problem in Example 3.4 utilizing the piecewise-linear model whose parameters are given in Fig.3.13 (VDO = 0.65V, rD =20Ω). Note that the characteristics depicted in this figure are those of the diode described in Example 3.4(1mA at 0.7V and 0.1V/decade). 4. Consider the circuit shown in Fig. 3.19. A string of three diodes is used to provide a constant voltage of about 2.1V. We want to calculate the percentage change in this regulated voltage caused by (a) a ±10% change in the power-supply and (b) connection of a 1-kΩ load resistance. Assume n =2. 5. Consider a peak rectifier fed by a 60-Hz sinusoid having a peak value Vp =100V. Let the load resistance R =10kΩ. Find the value of the capacitance C that will result in a peak-to-peak ripple of 2 V. Also, calculate the fraction of the cycle during which the diode is conducting and the average and peak values of the diode current. Chapter 5 Bipolar Junction Transistor (BJTs) EXERCISES 1. Consider an npn transistor with υBE = 0.7V at iC = 1mA. Find υBE at iC = 0.1mA and 10mA. 2. Measurement of an npn BJT in a particular circuit shows the base current to be 14.46μA, the emitter current to be 1.460mA, and the base- emitter voltage to be 0.7V. For these conditions, calculate α, β, and Is. 3. A particular transistor is said to have αF≒1 and αR =0.01. Its emitter scale current (ISE) is approximately 10-15A. What is its collector scale current (ISc)? What is the size of the collector junction relative to the emitter junction? What is the value of βR? 4. (a) Use the EM expressions in Eqs. (5.26) and (5.27) to show that the iC-υCB relationship sketched in Fig.5.9 can be described by iC = αF IE+ IS ﹝αF – (1/αR)﹞e υCB/VT . Neglect all terms not containing exponentials. (b) For the case Is =10-15A, IE = 1 mA, αF≒1, and αR =0.01, find iC for υCB =-1V, +0.4V, +0.5V, +0.54V, +0.57V. Also find the value of υCB at which iC = 0. (c) At the value of υBC that makes iC zero, what do you think iB should be? Verify using Eq.( 5.28). 5. For a pnp transistor having IS = 10-11A and β=100, calculate υEB for iC =1.5A. 6. In the circuit shown in Fig.E5.11, measurement indicates VB to be +1.0V and VE to be +1.7V. What are α and β for this transistor? What transistor? What voltage VC do you except at the collector? 7. Find the value of υCB at which iC of an npn transistor operated in the CB configuration with IE = 1 mA is reduced (a) to half its active-mode value and (b) to zero. Assume αF ≒1 and αR =0.1. The value of VBE was measured for υCB = 0 < see measuring setup in Fig.5.18(a) > and found to be 0.7V. Repeat (a) and (b) for αR =0.01. 8. Consider the circuit in Fig.5.19(a). At VCE =1V, VBE is adjusted to yield a collector current of 1mA. Then, while VBE is kept constant, VCE is raised to 11V. Find the new value of IC. For this transistor, VA=100V. 9. Measurements made on a BJT operated in saturation with a constant base- current drive provide the following data: at iC =5 mA, υCE =0.17V; at iC =2 mA, υCE =0.11V. What are the value of the offset voltage VCEoff and saturation resistance RCEsat in this situation? 10. For the situation described in Example 5.2, while keeping IC unchanged at 1 mA, find the value of RC that will result in a voltage gain -320V/V. What is the largest negative signal swing allowed at the output ( assume that υCE is not to decrease below 0.3)? What (approximately) is the corresponding input signal amplitude? (Assume linear operation). 11. Consider the circuit in Fig.5.32 for the case VCC = +5V, RB =RC = 1 kΩ, and β = 100. Calculate the base current, the collector current, an the collector voltage. If the transistor is saturated, find βforced. What value should RB be raised to in order to bring the transistor to the edge of saturation? D12. Redesign the circuit of Fig. 5.34(a) (i.e., find new value for RE and RC) to establish a collector current of 0.5mA and a reverse-bias voltage on the collector-base junction of 2V. Assume α≒1. D13. For the circuit in Fig. 5.37(a), find the largest value to which RC can be raised while the transistor remains in the in the active mode. D14. The circuit of Fig. 5.38(a) is to be fabricated using a transistor type whose β is specified to be in the range of 50 to 150. That is, individual units of this same transistor type can have β values anywhere in this range. Redesign the circuit by selecting a new value for RC so that all fabricated circuits are guaranteed to be in the active mode. What is the range of collector voltages that the fabricated circuits may exhibit? 15. For the circuit in Fig. 5.41, find the total current drawn from the power supply. Hence fin the power dissipated in the circuit. 16. Solve the problem in Example 5.12 with the voltage feeding bases changed to +10V. Assume that βmin = 30, and find VE, VB, IC1, IC2. 17. The bias arrangement of Fig. 5.45 is to be used for a common-base amplifier. Design the circuit to establish a dc emitter current of 1 mA and provide the highest possible voltage gain while allowing for a maximum signal swing at the collector of ±2V. Use +10V and -5V power supplies. 18. For the circuit in Fig. 5.47(a) with VCC =10V, I = 1mA, β =100, RB =100 kΩ, and RC =7.5kΩ, find the dc voltage at the base, the emitter, and the collector. For VEE =10V, find the require value of R in order for the circuit of Fig. 5.47(b) to implement the current-source I. 19. A BJT having β =100 is biased at a dc collector of 1 mA. Find the value of gm,re, and rΠ at the bias point. 20. To increase the voltage gain of the amplifier analyzed in Example 5.16, the collector resistance RC is increased to 7.5kΩ. Find the new values of VC , Aυ, and the peak amplitude of the output sine wave corresponding to an input sine wave υi of 10mV peak. 21. Consider the circuit in Fig.5.59 for the case: VCC = VEE =10V, I = 1mA, RB =100 kΩ, and RC =8kΩ, and β =100. Find all dc currents and voltages. What are the allowable signal swings at the collector in the both direction? How do these values change as β is changed to 50? To 200? Find the values of the BJT small-signal parameters at the bias point (with β =100). The Early voltage VA =100V. 22. Consider the CE amplifier of Fig. 5.60(a) when biased as in Exercise 5.41. In particular, refer to Fig.E5.41 for the bias currents and the values of the elements of the BJT model at the bias point. Evaluate Rin(without and with RB taken into account), Aυo (without and with ro taken into account), Rout (without and with ro taken into account), and Ais (without and with RB taken into account). For RL = 5 kΩ, find Aυ. If Rsig = 5 kΩ, find the overall voltage gain Gυ. If the sine-wave υΠ is to be limited 5mV peak, what is the maximum allowed peak amplitude of υ sig and the corresponding peak amplitude of υo. 23. Consider the CB amplifier of Fig. 5.62(a) when design using the BJT and component values specified in Exercise 5.41. Specifically, refer to Fig. E5.41 for the bias quantities and the values of the components of the BJT small-signal model. Let Rsig = RL = 5 kΩ. Find the values of Rin, Aυo, Ro, Aυ, υi /υs and Gυ. To what value should Rsig be reduced to obtain an overall voltage gain equal to that found for the CE amplifier in Exercise 5.43, that is, -39V/V? 24. The emitter follower in Fig. 5.63(a) is used to connect a source with Rsig = 10 kΩ to a load RL = 1 kΩ. The transistor is biased at I = 5mA, utilizes a resistance RB = 40 kΩ, and has β =100 and VA = 100V. Find Rib, Rin, Gυo, and Rout. What is the largest peak amplitude of an output sinusoid that can be used without the transistor cutting off? If in order to limit nonlinear distortion the base- emitter signal voltage age gain become if RL is changed to 2 kΩ? To 500Ω? 25. For a BJT operated at IC = 1mA, determine ƒT and CΠ if Cμ =2pF and ︳ hƒe∣= 10 at 50MHz. 26. For the amplifier in Example 5.18, find the value of RL that reduces the midband gain to half the value found. What value of ƒH result? Note the trade-off between gain and bandwidth. 27. Consider the inverter of Fig. 5.74 when υI is low. Let the output be connected to the terminals of N identical inverters. Convince yourself that the output level VOH can be determined using the equivalent circuit shown Fig. E5.53. Hence show that For N =5, calculate VOH using the component values of the example circuit discussed earlier (i.e., RB =10 kΩ, RC =1kΩ, VCC =5V). Note that this arrangement is historically important, as a precursor to the TTL logic form. It is called Resistor-Transistor Logic or RTL. EXAMPLES 1. The transistor in the circuit of Fig. 5.15(a) has β=100 and exhibits a υBE of 0.7V at iC = 1mA. Design the circuit so that a current of 2 mA flows through the collector and a voltage of +5V appears at the collector. 2. The transistor in Fig. 5.33 is specified to have β in the range of 50 to 150. Find the value of RB that results in saturation with an overdrive factor at least 10. 3. We wish to analyze the circuit of Fig. 5.35(a) to determine the voltages at all nodes and the current through all branches. Note that this circuit is identical to that of Fig. 5.34 except that the voltage at the base is now +6V. Assume that the transistor β is specified to be at least 50. 4. We desire to analyze the circuit of Fig. 5.37(a) to determine the voltages at all nodes and the current through all branches. 5. We want to analyze the circuit of Fig. 5.39 to determine the voltages at all nodes and the current through all branches. The minimum value of β is specified to be 30. 6. We wish to analyze the circuit in Fig. 5.41(a) to determine the voltages at all nodes and the current through all branches. 7. We wish to design the bias network of the amplifier in Fig. 5.44 to establish a current IE = 1 mA using a power supply VCC = +12V. The transistor is specified to have a nominal β value of 100. 8. To gain more insight the operation of transistor amplifiers, we wish to consider the waveforms at various points in the circuit analyzed in the previous example. For this purpose assume that υi has a triangular waveform. First determine the maximum amplitude that υi is allowed to have. Then, with the amplitude of υi set to this value, give the waveforms of iB(t), υBE(t), iC(t), andυC(t). 9. A transistor amplifier is fed with a signal source having an open- circuit voltage υsig of 10mV and an internal resistance Rsig of 100 kΩ. The voltage υi at the amplifier input and the output voltage υo are measured both without and with a load resistance RL = 10 kΩ connected to the amplifier output. The measured results are as follows: Without RL With RL connected Vi(mV) 9 8 Vo(mV) 90 70 10. We wish to select appropriate value for CC1,CC2, and CE for the common-emitter amplifier whose high- frequency response was analyzed in Example 5.18. The amplifier has RB = 100 kΩ, RC = 8 kΩ, RL = 5 kΩ, Rsig = 5 kΩ, β0=100, gm =40 mA/V, and rΠ =2.5 kΩ. It is required to have fL = 100Hz.