IEEE Transactions on Magnetics

advertisement

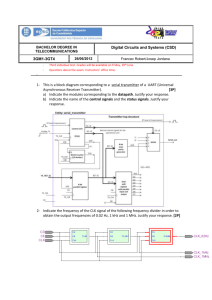

1 DEVELOPMENT OF SYNTHESIZABLE IP CORES FOR UART 1 V.Rama Gowri .B., 2P.K.Suresh, 3Prof. M.Murali M.Tech Scholar, BABA Institute of Technology & Sciences, Visakhapatnam, AP-India 2 Assisstanr Professor, ECE Dept, BABA Institute of Technology & Sciences, Visakhapatnam, AP-India 3 HOD, ECE Dept, BABA Institute of Technology & Sciences, Visakhapatnam, AP-India 1 transmission of serial & parallel data. UART is a serial Abstract--A soft processor is configured from the logic communication protocol which is extensively used for data resources inside the FPGA. Soft cores are simpler (more communication as it uses full duplex communication in primitive) and slower than their hard-core counterparts. However, they have the advantage that you only need to serial link, which gives us advantages like use of less no. of transmission lines, increased transmission distance, and implement a core if you need it and that you can instantiate as many cores as you require until you run out of resources in the form of programmable logic blocks. A hard microprocessor more reliability and also it reduces the distortions in a signal[8]. core is implemented as a dedicated, predefined block. A hard core processor does not provide the flexibility of modification In electronic industry basically intellectual property(IP) to suit the application. In addition, only specific FPGAs will core is a reusable part, where it can be used alone or in have the option of having a hard-core; therefore, the choice of group. These can be basic building blocks of several chip vendors and FPGAs are limited. MIPS (originally an acronym designs or logic designs. These can be configured in two for Microprocessor without Interlocked Pipeline Stages) is a reduced instruction set computer (RISC) instruction set architecture (ISA) developed by MIPS Technologies (formerly MIPS Computer Systems, Inc.). The early MIPS architectures ways such as soft cores and hard cores. As there is a tremendous growth in embedded Systems with which the complexity increase so the better idea is to use the were 32-bit, with 64-bit versions added later. The number of reconfigurable and reusable cores as these are technology instructions executed by the MIPS is high and it fulfills the independent need of real time applications. By observing all the above applications[4][3]. The above can be obtained with the constraints and available features our objective is to develop advent use of soft cores. of course hard cores also often peripherals and synthesize a verilog code for embedded good predictability of chip performance but whose processors which includes peripherals like programmable application function cannot be modified fruitfully. So soft timer, serial port communication and parallel port and can be customized for specific cores are preferred because of their reusability. communication at very low cost. In this paper the UART serial communication controller is designed and tested thoroughly. All the simulation and synthesis of these IP cores are carried In UART design, for achieving the speed matching of the out in XILINX 13.3 and implemented in FPGA development processor and UART interface. It takes asynchronous First board. In First Out (FIFO)s as buffers to realize data exchange Index Terms-- FPGA; Soft cores; IP; UART. between UART and external devices.[1].In the design of . high speed UART ,before synthesizing the overall design the I. INTRODUCTION baud rate generator is incorporated into the UART Serial port is responsible for its serial data transmission, design[2].Field Programmable Gate Array(FPGAs) are where a serial port is a global tool in a computer. This serial increasingly used for implementing embedded systems. Soft port is provided with UART, which manages the data core processors for FPGAs are becoming popular due to reduced design cost, flexibility.[6] Now a days ,embedded processor cores are integrated into most system-on-chip 2 (SoC) applications. Reusing of generic processors is often preferred due to time to time market constraints[4]. A soft core processor is used for customizing a given application and synthesized for a target. Soft core processors provide several advantages like reduced cost, flexibility, platform independence and great immunity to obsolescence. So soft Fig. 1. Baud Rate Generator cores are used for embedded applications[3]. A nonpipelined Reduced Instruction Set Computer (RISC) The BAUD rate generator divides down the system clock to processor is used for signal processing applications. These provide the bit clock (Bclk) with a period equal to one bit RISC processors are designed for executing Instruction set time and also Bclk8, which has frequency eight times the and it can be realized using VerilogHDL.[7] Because of Bclk popular applications of IP cores, these are frequently used in programmable transmits and receive bit timing device. SOC applications.[5] In this paper, synthesizable IP cores of Given the programmed value, it generates a periodic pulse, low cost peripherals are used for embedded SoC which determines the baud rate of the UART transmission. applications. For that Verilog description language is used in This pulse is used by the receiver and transmitter circuit to order to pursuit & integrate soft cores with RISC processor. generate a sampling pulse for sampling the received serial In these soft cores, with the help of Verilog code by data and to determine the bit width of the transmit data. The dumping in any FPGA and whose operation can be verified first process increments the divide-by-13 counter on the and it can be further reprogrammed UART module includes rising edge of the clock. The second process increments three sub modules such as baud rate generator, transmitter divide-by-256 counter on the rising edge of clkdiv13. A module & receiver module. The following is the descriptions concurrent statement generates the MUX(multiplexer) regarding the modules mentioned above. output, BclkX8. The third process increments the divide-by- frequency. The Baud Rate Generator is a 8 counter on the rising edge of BclkX8. UART includes II. Description of UART another part called transmitter. This is generally a shift The baud rate is defined as the no. of distinct symbols register that shifts it out bit by bit with a specific rate. UART transmitted per second irrespective of form of encoding. A transmitter fetches data in parallel format and instructs the symbol is one of several voltage, frequency (or) phase UART to transmit it in a serial format with respect to frame changer. Before going to the synthesizing process the format. This frame format generally includes start bit, stop programmable baud rate generate must be included as a bit, parity bit and ideal state. major part with UART[2], which is primarily used for dividing the system clock by accepting the clock input and given bit clock (Bclk) whose frequency is 8 times the bclk frequency. This periodic pulse is used for knowing the baud rate of UART transmission. This generated pulse is further Fig. 2. Serial data Transmission useful for receiver control and transmitter control of UART, to determine the bit width of the transmit data and also for setting receiver based rate. III. State Machine Charts The transmission of data will be initiated by checking the holding register (TXD hold reg) (Or FIFO) for the data. If it holds the data, then the start bit will be included which is 3 responsible for alerting the receiver to receive the data to be sent. Now, the data i.e. in the holding register is to be loaded into the transmit register through the local bus and the “Transmit data read “would set enable. This signal indicates the starting of a sequence and a new value will be loaded. To send the frame in bit by bit format the Baud rates of baud rate generator and transmitter must be synchronized. After synchronization Least Significant Bit (LSB) will be transmitted first. After sending the data bit, the transmitter at last sends the parity bit which is used by the receiver to check the error if present in it. In order to escape from the incorrectly formatted received data, transmitter must add at least one stop bit. If the holding register holds another symbol, the above process will be repeated; otherwise the transmitter will jump into an ideal state. The following occurs, when Micro Controller is ready. The Micro controller will remain in ideal mode till TDRE Fig. 3. SM Chart for Transmitter (Transmit data register enable) = 1 and it loads data into TDR and clears TDRE.The UART transmits data from TDR Receiver: The receiver must be responsible for data to TSR & sets TDRE.Eight data bits will be included by transmission to receive data in serial format by ignoring start stop bit (“0”) & Stop bit (“1”) Now, In the ideal state, State bit and stop bit. A receiver has to generate a local clock in Machine waits till TDR is loaded and TDRE in order to be synchronized with transmitter whenever the start cleared.When TDRE is set State Machine checks for bit is received. This is because of the Asynchronous synchronization in SYNCH state when it gets raising edge behavior of UART. Baud rates must by synchronized before bit clock (Bclk) then LSB will be transmitted for one bit at a transmitting or receiving the data. According to the baud time. Now in TDATA state Bclk is checked and the TSR is clock of the baud rate generator, receiver receives the data shifted to the next bit which is to be transmitted and after detecting the start bit. It will be completed after the simultaneously bit counter will be incremented. When Bct = stop bit is received. In order to check the correctness of data 9, eight bit data including stop bit will be transmitted. After parity bit is used. In case of invalid stop bit (or) error, the successful transmission Bct will be cleared and SM reverts frame error will be enabled. After receiving the data, “ back to its ideal mode. Receiver data Write” in going to be set .The following will be procedure for UART receiver to receive data a) Once the start bit is reached from transmitter, it detects the remaining bits serially and shifts them into RSR b) When all bits including stop bit is received,the RSR will be loaded into RDR, & RDRF will be set. c) The Micro Controller will check the RDRF flag, and RDR is read and flag is cleared once it is checked. 4 SM will remain ideal till RXD is loaded. once it is set ‘0’ processor is realized using Verilog HDL for executing start bit will be detected. If the bits in the RXD are not instruction sets[7]. synchronized with local bit lock (Bclk), there may occur a problem if RXD changed the clock edge. In order to overcome the above problem each bit must be sampled eight times, on the rising edge of bclk8. Fig .5. Output Test-Bench of UART The above shows the output waveform of UART. On the transmitter side we have applied a input bit stream of Figure 2. The whole diagram of the system 10101100.The corresponding output at receiver side is also the same which can be read from the above diagram. With IV. RESULTS AND ANALYSIS the inclusion of the Baud Rate Generator with the delay of We used verilog hard ware description language for clock pulse ,the input appears at the receiver. implementation. Hardware description languages are useful in verifying FPGA circuits[2]. The HDL is also used to VII. CONCLUSION develop the Register-Transfer Level(RTL) model of UART protocol, which is used to test transmission and reception of The significance of the IP cores and its application with different data frames. And also test bench wave forms are advantages is demonstrated using the design and synthesis of generated for the above mentioned modules. Xilinx ISE 131 UART. This UART design is building block of entire soft is used for synthesis of above mentioned IP cores. The cores for the complete architecture of the processor. The synthesizable soft cores of embedded peripherals are results pertaining to the SM charts and the output wave developed and are interfaced with the RISC processor to forms for the corresponding inputs are mentioned in the enhance the advantages such as low cost, reliability & Figures presented in the results section. compatibility. The characteristics of soft cores can also be observed. Reduced instruction set computer (RISC) architectures are the basic building blocks of high performance processors. RISC has a simplified instruction set, with register- to register arithmetic instructions. Here memory only can be accessed by load and store instructions Here we are going to determine the importance of a reconfigurable processor core (soft core) based on RISC architecture as initiative for application specific processor design. As complex instructions could not be performed efficiently on 8 bit processor here we prefer RISC processor. Here RISC IX. REFERENCES [1] He Chun-zhi, Xia Yin-shui and Wang Lun-yao, " A universal asynchronous receiver transmitter design, “ in Electronics, Communications and Control (ICECC), 2011 International Conference , Ningbo, Sept. 2011,pp. 691 – 694. [2] Norhuzaimin, J. and Maimun, H.H. “The design of high speed UART,” in Applied Electromagnetics, 2005. APACE 2005. Asia-Pacific Conference, Johor, Dec. 2005. [3] Anderson, I.D.L.,Khalid, M.A.S. and Tong, J.G, “SoftCore Processors for Embedded Systems,” Microelectronics, 2006. ICM '06. International Conference, Dhahran, Dec. 2006,pp.170 – 173. [4] Le Gal,B and Jego,c., “Softcore Processor Optimization According to Real-Application Requirements,” Embedded Systems Letters, IEEE Vol:5, Issue: 1 ,pp.4 – 7, March 2013. [5] Xuemin Pang Daojie Yu, Jianbing Li and Yuhua Guo, " Design and Application of IP Core in SoC Technology,” Information Science and Engineering (ISISE), 2010 5 International Symposium , Shanghai, 24-26 Dec. 2010,pp. 71 – 74. [6] Al Rayahi, O.A. and Khalid, M.A.S., "UWindsor Nios II: A soft-core processor for design space exploration,” Electro/Information Technology, 2009. eit '09. IEEE International Conference, Windsor, ON, 7-9 June 2009,pp. 451 – 457. [7] Sakthikumaran, S., Salivahanan, S.and Bhaaskaran, V.S.K., “16-Bit RISC processor design for convolution application,” in Recent Trends in Information Technology (ICRTIT), 2011 International Conference, Chennai, Tamil Nadu, ,pp. 394 – 397, 3-5 June 2011. [8] Fang Yi-yuan and Chen Xue-jun, “ Design and Simulation of UART serial communication module based on VHDL” in Intelligent Systems and Applications(ISA),2011 3rd International Workshop,wuhan,pp. 1-4 ,28-29 May 20