Short-circuit dissipation of static CMOS circuitry and its impact on the

advertisement

468

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. SC-19, NO. 4, AUGUST 1984

Short-Circuit Dissipation of Static CMOS

Circuitry and Its Impact on the Design

of Buffer Circuits

HARRY

J. M. VEENDRICK

Abstract —This paper gives a detailed dkcussion of the short-circuit

compouentin the totaf powerdissipationin CMOS circuits, on the basisof

an elementaryCMOS inverter. Designconsiderationsare givenfor CMOS

buffer circuits, based upon the results of the dissipation discussion,to

increasecircuit performance.

LIST OF PARAMETERS

A

a

b

process-determined

ratio between

@ of NMOS

P,

h

~ of PMOS

~ of nMOST

input

ALP

rise or fall time of an input

To

rise or fall time of an output

Tr

rise time of a signal

v dd

supply

~,

input

v out

VT

VT.

v

output voltage

threshold voltage

transistor

channel width

with

capacitance

equal channel

length

INTRODUCTION

of the Nth

inverter

of a

D

of a string

total power

URING

the last

on node N

of inverters

dissipation

periods

when no signal transients

Manuscript received October 19, 1983; rewsed December 28, 1983.

The author is with Philips Research Laboratones, 5600 JA Eindhoven,

The Netherlands.

0018 -9200/84/0800-0468

CMOS

technology

has

technologies

for

is its

low

occur.

However,

static

during

during

signal there will always be a short-cir-

cuit current flowing from supply to ground in static CMOS

circuits. So far only limited analyses and discussions have

appeared in the literature

on this power component

of

static CMOS circuits [1].

In integrated circuits it is always necessary to drive large

circuitry,

etc.), often at

capacitances (bus lines, “off-chip”

high clock frequencies. Such driving circuits (buffers) will

take a relatively large part of the total power consumption

of the chip. It is clear that optimization

requires a different approach as compared

of CMOS

dynamic power dissipation

short-circuit

power dissipation

period-time

of a signal ( = l/~)

years

due to the absence of dc currents

an edge of an input

current

five

become one of the most dominant

VLSI circuits.

The most important

reason for this

power dissipation,

mean value of the short-circuit

current

maximum value of the short-circuit

current

gate length of the nMOST

gate length of the pMOST

gate length minus effective channel length of the

nMOST

gate length minus effective channel length of the

pMOST

P

Pl

P2

T

of the Nth inverter

and

( = I/T)

number

of the Nth inverter

of the Nth (symmetri-

gate oxide capacitance

N

of the pMOST

of a string

total capacitance on node N

input capacitance of the first inverter

short-circuit

signall

voltage

w PN

and pMOST

signall

voltage

G:N

string

load capacitance

PN

fall time of a signall

T,

width

frequency

ALn

and

rise or fall time of a signall

T-

transistor

gate capacitance

parasitic

I

I mean

I max

Ln

Lp

in (11)

time

r

threshold voltage of nMOST

threshold voltage of pMOST

channel width of the nMOST

/3 of a transistor

channel

CL

CN

co

c 0x

defined

Lp and Ln [(A9)]

cal) inverter

c gN

constant

ratio between parasitic

nodal capacitance

load capacitance

gain factor (pA/V2

) of an MOS Itransistor

i

lb

USED

t

tion

logic [2]. These buffer

to obtain

detailed

inverter

minimum

power

discussion on power

will be given first.

circuits

of such circuits

to optimization

need extra atten-

dissipation.

dissipation

Therefore,

a

of a basic CMOS

lAlthough the rise and fall times are commonly defined to be the time

between the 10 and 90 percent level of the signal extremes, in this paper

these parameters are defined as the total duration of a linearized edge.

$01.00

01984 IEEE

469

VEENDRICK: SHORT-CIRCUIT DISSIPATION OF STATIC CMOS CIRCUITRY

-Wjd

the

-G-

~“

transistor

will

be in

saturation

this

during

of time.

Using

v@Jt

1

NMOS

period

PMOST

the simple

MOS formula,

this leads to

NMOST

-

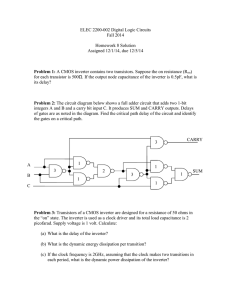

Fig. 1.

(4)

v.~

Basic CMOS inverter

This current

will reach its maximum

half the supply

“nk=i-k-n

tion

voltage

that the inverter

of the input

!

1! !

I _=2*;

Assuming

Fig. 2.

Current behavior of an inverter without load

input

A static CMOS

OF A BASIC CMOS

inverter

the absence of transients

on the input:

f’I(t)dt

t~

equal

conduct.

However,

during

there will be a time period

pMOST

from

will

supply

without

voltage

~,

conduct,

to ground,

load.

(Vi.)

This

in which

causing

both the nMOST

(1)

as long

is higher than a threshold

and lower than a threshold

If we load the inverter

(Fig.

tance C~,’ then the dissipation

it can be derived

and

short-circuit

Clearly,

as the

input

Equations

of the circuit

Pz = Imem”V.

(2)

I

Since there is a difference

without

in the short-circuit

load

and that

dissipation

of an inverter

with

load, we start our discussions on the basis of an inverter

with zero load capacitance. For simplicity

we assume that

the inverter

fundamentally

is symmetrical

Bn=Bp=B

During

current

(an asymmetrical

different),

the period

which

inverter

O to l~m,

Fig. 2 that

and

(7)

t2=;.

t-v~)+

(8)

the output

1 .~”(vdd–2vT

‘em = fi

vdd

)3”;.

(9)

p2=+”(vdd–2v~)3”;

.

(lo)

As l/T=

f,

(10) shows that this dissipation

also proportional

to the frequency

Vdd and VT are process-determined,

component

is

of switching,

Because

the only design param-

eters that affect P2 are /.? and the input rise and fall times

(~) of the inverter.

For an inverter

with capacitive

load, the ~‘s of the

transistors are determined by requirements

on output rise

and fall times. In this case the short-circuit

dissipation

(3)

depends only on the duration of the input signal edges. As

will be shown further on, these edges should not be too

long, especially in the case of driver circuits that have a

means that

and VTH=– VT,=VT.

from

(6)

is not

(tl – t2;Fig. 2) in which the short-circuit

Z increases

between

its transients

From (2) and (9) the following expression can be derived

for the short-circuit

dissipation of a CMOS inverter without

load:

due to para-

design.

of an inverter

relation

(5), (6), and (7) lead to

PI does not depend on

contributions

sitic output capacitances,

such as junction

capacitances).

Pz, however, strongly depends on

The second component

the inverter

~f = ~) of the

(q=

has the solution

consists of two

dissipation:

from

(5)

a capaci-

(1)

component

times2

and a linear

I mean —

-~~;:”’’”d’(+r-v,)d(~

which

of Fig. 1 with

Pl = C~”V2” f and

design (apart

(~n(t)–vT)2dt.

voltage ( V~n) above

dissipation:

the dynamic

the inverter

from

VT

tl=.—— -r

v dd

components:

dynamic

rise and fall

as

to flow

( lV~Pl) below Vdd.

output

of

T (equal to one period

voltage (Vin) and time (i) during

on the input,

a short-circuit

flows

result

fin(t)=+t,

as shown in Fig. 2 for an inverter

current

Another

power during

when the input

a transient’

a time

=;J:’;

(symmetrical)

1) is at high level ( V~~), only the NMOS transistor conducts, and when the input is at low level, only the pMOST

will

during

INVERTER

does not dissipate

due to the assump-

was symmetrical.

signal) can thus be written

signal

the input

DISSIPATION

value when ~n equals

= Vdd/2),

this assumption

is that the current behavior during the

with respect to the

time period tl – t3 will be symmetrical

time t2.

The mean current

If;

(~.

large ~ value. In the derivation

of (10), we started with an

voltage

(V&,) will be larger than the input voltage ( ~,) minus the

threshold voltage (VT) of the nMOST. As a consequence,

2The definitions of rise and fall times used here are different from those

in common use (see the list of parameters used).

470

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. SC-19, NO. 4, AUGUST 1984

V(jd=!iv

[WI]

pMosT VT.Vfn= -Vlp. 0.8 Vo[t

v,” -it

‘“Y:

~ ‘/% ’/$=170

UA/v2

/

L.

I

~

2

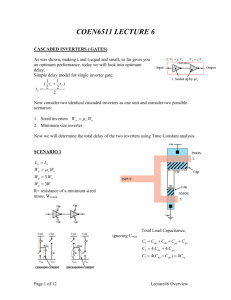

Fig. 3.

T,= TO= 10 n5ec

The inverter used in the example

1(+.-

;,.:

,,,~

/

r

,’

71= TO= 5 nsec

6\

~

240

7, .5

220

[nsec]

/

CL=0

20

~o 1

18i

dynamic

&

L’

/

dlsslpatlon

=0.s..)

(~,

/’

2

i’

2

,

L68yj2

T

‘

Fig. 6.

Inverter dissipation

time -

Fig. 4.

Short-circuit

current

as a function

capacitances.

of different

inverter

‘rO.

transient

capacitances

-f - 5@c]

to ground

it is obvious

of the input

hme

what

happens

when

following

we load

will

signal.

depend

with zero load

versus load

on the rise and fall

Fig. 6 shows this characteristic

values of the input

rise and fall times ( 71). The

the load capacitance

example

the inverter

with

examines

different

to equal input

and out-

characteristics

are

on the figure.

From

these characteristics

operation

input

capacitances.

corresponds

put rise and fall times for the different

indicated

The

inverter

dashed line shows the dynamic dissipation

(~= 10 MHz),

while the solid lines show the actual inverter dissipation

(dynamic plus short-circuit

dissipation).

The points where

Inverter output voltage behawor for different inverter load

capacitances.

load.

a high level

that the dissipation

characteristic

for different

without

from

with a fall time of 5 ns.

capacitance

times

values of the load

is switched

As expressed in (10) for a CMOS

inverter

of the inverter load capaci-

curves for different

when the input

capacitance,

Fig. 5.

2FT]

load

the output

[v]~

as a function

tance.

“d

of the inverter

we can conclude

that if the

is such that the output

signal and

signal have equal rise and fall times, the short-circuit

dissipation

will

be only

a fraction

( <20

percent)

of the

Example

total dissipation.

However, if the inverter is more lightly

loaded, causing output rise and fall times that are relatively

The discussions that follow are based upon the inverter

whose parameter values are shown in Fig. 3. Its operation

short as compared to the input rise and fall times, then the

short-circuit

dissipation

will increase to the same order of

was simulated

are presented

magnitude as the dynamic dissipation.

Therefore, to minimize dissipation, an inverter used as part of a buffer should

current

with a circuit analysis program, Some results

in Fig. 4. The figure shows the short-circuit

behavior,

during

a time interval

tl – td (see Fig. 2),

as a function of the load capacitance CL, for input rise and

fall times of 5 ns. Curve @ shows the behavior of the

inverter

without

load. At any time this current is the

maximum

short-circuit

current that can occur. This means

that all other current

characteristics

for different

load

capacitances must be within this curve. Curve @) shows

the short-circuit

current behavior of the inverter when it is

loaded with a characteristic

capacitance CL of 500 fF. In

this case the rise and fall

times

on the output

equal to the rise and fall times on the input.

node

are

Fig. 5 shows

be designed in such a way that the input

are less than

or about

equal

rise and fall times

to the output

rise and fall

times in order to guarantee a relatively small short-circuit

dissipation.

Fig. 7 shows the linear relationship

[according to (10)]

between the short-circuit

dissipation and the input rise and

fall times (7, ) derived by means of circuit simulations.

In

this case the kverter

of Fig. 3 was loaded with a capacitance of 500 fF. From Fig. 5 it was known that a load

capacitance

output

of 500 fF causes 5 ns rise and fall times of the

signal,

when the inverter

input

rise and fall times

VEENDRrCK: SHORT-ClRCUIT Dissipation

OF sTATIc cMos CIRCUITRY

[NJ

CL= 500 fF

160.

dynamic

lLO.

~

(

‘–-

120.----------------------------

4-——i~

,“t*r”al

s

100

0

n.

80

ix

~1

60 ~

v

LO

*

~

short-c!rcwt

4+6

8

T,=TO=5

nsec

1012

14

16

1’820i22L

262830

$2@Se~

Fig. 8.

—

Inverter dissipation as a function of the input nse and fall times.

~, = TO= 5 ns, is indicated

7 and the corresponding

short-circuit

only about 10 percent of the dynamic

This

result

of designing

way that the input

a string

and output

on

dissipation

is

dissipation.

capacitance

and therefore

dissipation,

it can also be applied

of inverters

mum,

is for the maximum

T, = TO. It has empirically

designs

the short-circuit

calculated

cgN+

Cparwl

Inverter string acting as a buffer circuit.

in such a

not

lead to an optimum

design.

and silicon

Design

optimization

minimum

dissipation

approach,

as will be shown in the following.

It has been derived

area requires

in the Appendix

of

the inverter

dissipation

design”

determined

by the following

for

a different

that a “minimum

string

is completely

three equations:

rise and fall times of each

inverter are equal to obtain minimum

dissipation can very

well be applied to the design of static CMOS buffers.

Although (10) was derived for an inverter with zero load

with

#

71

are equal to 5 ns, This point,

Fig.

bo.dlny

the nodal capoc!tances miude the

POrasrtlc trodd capacltOneef.(CpOq )

CM=

2

Fig. 7,

L8u 11., or

str, n~)

%cL+cpdrN

20.

o

+buff., @wwt.r

log ,. yt.

dissipation

short-circuit

to inverters

been found

is half

where

1

vdd–vTn”

designed

that

for

such

‘=

of the maxi-

(

2VT

2(vdd–vTfl)-v

vdd-iT

,,

‘ln

v

[

1}

(11)

with (10).

is constant

for a given technology.

DESIGN CONSIDERATIONS

In integrated

capacitances,

circuits

it is always necessary to drive large

like bus lines or “off-chip”

circuitry.

More-

1%.1

—=*.

b.

(l+b). cox.LnN

. (LnN(l+3a2)-ALnN-3aALPN}

over, this must often occur at high speed, which will take a

relatively

large part

chip.

Particularly

large

number

of the total

power

dissipation

in the case of bus lines, which

of inputs

of the different

control

subcircuits

d

and

on a

b,v N —

CN

—.

()

chip, it is necessary to have short signal rise and fall times

[(10)] to minimize dissipation.

‘

Suppose

we want

line or “off-chip”

to drive

fiN-1

such a bus interconnection

a signal coming from an where ~,?J represents

internal node A. Let us assume that the logic gate, having

6N- l/~N

is the Weriw

node A as output, is capable of charging a capacitance CO rise and fall times and

in a time t to 95 percent of the supply voltage. From the string. For a practical

foregoing results we know that if we use an inverter string

ions are made for the

as a buffer

circuitry

with

vTn=–vT,

rise and fall times on the bus line (or bonding

(Fig.

problem

8) loaded

~

of

the

last

inverter

stage,

factor at equal input and output

N is the number of inverters of the

application

the following

parameters

of (11), (12), and (“13):

assumpt-

now

with

is how

to design

a capacitance

an inverter

CL, with

~ ns rise and

between the P‘s of the successive inverters (tapering

was needed to guarantee a‘ minimum

propagation

vdd=5v

string

fall times on each node, driven from an internal logic gate

capable of charging and discharging the input capacitance

CO in the same time. In [3] it was derived that a factor of e

factor)

delay

time for such an inverter string. However, it is well understood that in terms of dissipation and silicon area this will

=lv

V= 0.05* Vdd [in (11)]

pad) to be driven.

The

the

(13)

co

between node A and the bus line, the rise

circuit

and fall times on each node of the string should be equal to

the required

1(12)

of the

&

=42 pA/V2

A =1

I

/3,0 =14 PA/V2

COX= 700 pF/m2

Ln = 2.5 pm

Required

ALn = 0.5 pm

rise and fall times:

the constants

ALP =1 pm.

~ = 5 ns. Practical

a and b are a = 3/2.5

values for

and b = 0.1.

472

IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. SC-19, NO, 4, AUGUST 1984

With

(12) this leads to

q$-qjiq+’.

B.

—=11.5.

&-1

This tapering

dependent;

factor,

nearly

as it is often called, is strongly

all parameters

the process. Different

to different

CMOS

tapering

of the driver

is as follows

according

by

Fig. 9.

Co= 100 fF and CL (Fig.

5 ns rise and fall times (r)

(inverter

(with

string),

8)

COMPARISON OF THE PERFORMANCES OF Two

on

then the design

I

c.f

( humber

(l+

7.

5

I

b). C.=llpF

stage (N)

is determined

by

power

I

P.. =PPN=fi~=

4.4*~O-3

A/V’,

creased

and

will

by 1 ns as compared

LP– ALP

Wp

~=/3PD =315’

The (N – i) inverters

‘0

_ 630pm

LP

~–

(-)

are now determined

3pm

In this paper

static

A-l

For this example,

as shown

therefore,

in Fig.

(This,

needed for this example

of

course,

has to be

string should be

9 to guarantee

a very

small

short-circuit

dissipation and a minimum area consumption,

The parasitic

nodal capacitances

are also depicted

in

Fig. 9.

By means of circuit

simulations

circuit

performance

found

the mean power dissipa-

a simple

when

formula

circuits.

A detailed

with

that if each inverter

way that the input

short-circuit

dynamic

of

a quick

dissipation

dissipation

of

of this short-

capacitances.

of the

It was

of a string is designed in such a

and output

( <20

rise and fall times are equal,

will

be much

percent).

This

less than

result

the

has been

applied to a practical

design of a CMOS driving circuit

(buffer),

which is commonly

built up of a string of inverters. An expression has also been derived for a tapering

factor between two successive inverters of such a string to

minimize

parasitic

power

dissipation.

power, and area) than is possible

propagation

delay.

e is a much

discharge

parasitic

for

dissipation

discussion

different

tapering factors: a factor of 11.5, which is derived in this

paper (process-determined)

from optimization

of power

dissipation

and area, and a factor e, which is derived [3]

from optimization

of the propagation

delay.

In this example the most important

improvement

due to

choosing a tapening factor equal to 11.5 instead of a factor

and a reduced

is derived

is given based upon the behavior

loaded

tion has been calculated at a clock frequency of ~ = l/T =

10 MHz. Table I shows the results of a comparison of two

area ( < 1/4)

(power,

by optimiza~ion

short-circuit

cluded that optimization

leads to a better overall

smaller

of the

like buffers,

AND CONCLUSIONS

the maximum

dissipation

inverter

the

the inverter

of

CMOS

circuit

fF and C~ = 11 pF we find from

will be equal to N =1.83.

rounded off to N = 2.)

optimization

circuits,

equal

delay.

SUMMARY

by the tapering

calculation

of inverters

been in-

“

B.

—=11.5.

(13) that the number

overall

con-

the power

factor

driving

and area) then can be achieved

the propagation

factor

the given CO =100

power

minus

to a tapering

we can state that

of CMOS

lead to a better

delay,

.&

parasitic

is the total power consumption

In summarizing,

‘Oepower dissipation

‘“(%l.=%:

Wp

This

I

dissipation which was actually meant (C~V2~).

In our case, the propagation

delay has only

or (see Appendix)

(&~n)N=%=105

1

( = 1/4).

consumption

sumption

designed

I

to (11):

Thus, the last inverter

With

e

I

invertersl

t’

()

factor

{actortl.5

the above assumptions):

CN=CL+CPXN=

INVERTER STRINGS

WITH DIFFERENT TAPERING FACTORS

to Fig. 8:

according

The designed inverter string for a practicaf example.

lead

TABLE I

situation,

equals 10 pF and we want

procedure

in (12) are determined

processes may therefore

factors.

If, in a practical

the output

process

Finally,

it is con-

in terms of power dissipation

performance

(in terms of speed,

by minimization

of the

APPENDIX

It can easily be derived

a capacitive

[1] what

transistor

is needed to

load C~ from the supply voltage

Vdd

473

VEENDtUCK: SHORT-CIRCUIT DISSIPATION OF STATIC CMOS CIRCUITRY

to a voltage

From

V in the time ~~:

2VT

% = $ “ ~dd2vT

2(vdd–vTn)–v’

“

“ { vdd–;Tn+ln

v

[

)

w)

(21) and (22) we derive

C~_l = (1 + b). (WP&~

This, combined

cN_,

with

(A1O) yields

*l+a.

(3aL~~

2vTn

1

Vdd–v=

1)

2(vdd–vTn)–v

n “ {, vdd–vT

n ‘ln

Equations

-3ALP~)

.(l+b).cox.

LnN – AL~~

(-

=A

v

[

[A13)

(J’LN”LJ

=

where

+ W~#~&X.

(A14)

)

(A4), (AS), and (A14) result in

(A2)

is a constant

for a given technology.

6%1

Thus,

= + “(l+

b)”cox”

Lw”:”fl;

‘N

“ ( LnN - AL~N +3a2. LnN –3a.ALPN).

(A3)

&=~.A

Finally,

and for the (N – l)th

bN-I

(A4)

BN-1=~.A.

assuming

the inverter

pn=pp=p;

and,

from

(A.15)

(18) and (25) we derive

inverter:

c~-~

Again,

‘N

and

because of the difference

~r=~f=T

in mobility

(A5)

of holes and

electrons:

WP– AWP

Wn– Awn

Lp – ALP ‘3*

Ln– ALn”

Wn

=3*

Ln – AL.

r“~no * ‘1 + b)”cOx”L”N

With equations (Al)

pletely determined.

Th~

number

‘N

and (A16)

of inverters

PN

the inverter

(N),

ratio in (26), is now determined

-3a.AL

which

}

“

(A16)

string is com-

depends

on the

by

(A.17)

(A6)

where Co and CN represent the input capacitance and the

output load capacitance of the inverter string, respectively

(Fig. 8).

As Wn >> AWn and WP>> A WP, (A6) reduces to

Wp

A

. (LnN(I+3a2)-AL

to be symmetrical:

V,n=-v=,

LP – ALP

~N

=

(A7)

“

ACKNOWLEDGMENT

With

The

Wn=(Ln–

ALn)~

b.

(A8)

❑

and given a lines

relation

between

LP=a.

Ln and LP

[1]

[2]

we find

a“Ln–

‘P” LP = ‘n ’Ln”3a”

[3]

ALP

Ln – AL.

“

wishes

to acknowledge

the helpful

made by A. T. van Zanten

suggesancl C.

Rf3FERENCES

(A9)

Ln

author

tions and contributions

Hartgring.

(A1O)

M. I. Elmasry, “ Digitaf MOS integrated circuits: A tutoriaf;’ Digital

MOS Integrated Circuils.

New York: IEEE Press pp. 4-27,

A. Kapuma, ” CMOS circuit optimization,” Solid-State Electron., vol.

26, no. 1, pp: 47-58, 1983.

C. Mead and L. Conway, Introduction

to VLSI

Systems.

New

York: pp. 12-15.

Harry J. M. Veendrick was born in Humme”lo en

Keppel, The Netherlands, on March 8, 1950; He

received the Ing. degree from the Zwolle l?olytechnicaf College, Zwolle, The Netherlands, in

of

1971, and graduated from the Department

Electronic

Engineering

at the Eindhoven University of Technology,

Eindhoven, The Netherlands,

in 1977.

.

c

PmN–l

=b” CgN and

CpuN=b. C~.

(A12)

In 1977, he joined Philips Research Laboratories, Eindhoven, The Netherlwds, where he is

working in a digital integrated-circuit

design

group on MOS circuit design.