Chapter 1 topics

advertisement

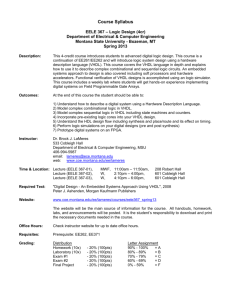

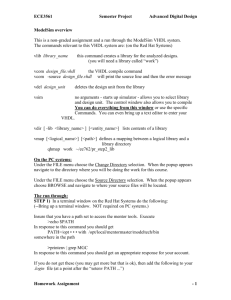

1 Digital Circuits ans Systems (CSD) Chapter 1 topics 1. 2. 3. 4. Use your official UPC e-mail address to communicate with your instructors. Use and manage an e-mail client like Thunderbird or Outlook. Use a SFTP client like WinSCP to remotely access your network disk drive “L”. Explain the five elements to achieve effective cooperative learning: 1) positive interdependence; 2) face-to-face interaction; 3) individual accountability and personal responsibility; 4) use of interpersonal and small-group skills; and 5) group processing or reflection. 5. Explain the concept of a top-down design of a digital circuit and its schematic entry and simulation by a CAD/EDA tool (Computer Aided Design / Electronic Design Automation). 6. Analyse a sPLD/CPLD/FPGA development board and draw a block diagram to include the programmable chip, input switches and pushbuttons, and output LED’s or 7-segment displays. 7. Organise a plan for developing the exercise and being able to work efficiently cooperating in a team of 3 members using the proposed methodology. 8. Analyse your own individual and group study time. 9. Produce a quality written solution; for example, report your work using a predefined word processor template and utilities: spelling and grammar, chapter enumeration, page headers and footers, hyperlinks, cross-references, figure captions, text styles, etc., for a given exercise, control or any other assignment, using the given instructions1. 10. Assess the own or the group learning progression and the quality of the deliverables. 11. Use Google docs to share files with in the cooperative group and Google sites to publish your achievements and results in your ePortfolio ----------------------------- 12. Use and explain the functionality of logic gates AND, NAND, OR, NOR, XOR, NXOR, NOT) 13. Analyze a logic circuit built using logic gates. Analysis concept map. 14. Use the application WolframAlpha to verify logic equations and determine the truth table of a combinational circuit. 15. Use the HADES JAVA-based platform2 to visualise and analyse the operation of digital circuits. 16. Simulate a subcircuit, a digital circuit which is inside a black box or entity, using the virtual laboratory software Proteus-ISIS. Capture a logic schematic in Proteus-ISIS and run its simulation to verify how it is functioning. 17. Install the ispLEVER Classic from Lattice Semiconductor and follow its design flow to implement a schematic/VHDL project into a sPLD chip. 18. Search books and the Internet to find information about the basics of VHDL language. 19. Explain the design flow of a modern digital circuit: from the VHDL description to the PLD programming. 20. Explain the basic technological details of a SPLD like the GAL22V10 and the way it is programmed. 21. Explain the differences between the VHDL design styles: structural and behavioural. ----------------------------- 22. Explain and relate the following concepts for designing a logic circuit: truth table, Boolean algebra and logic functions, minimisation, SoP (sum of products) and PoS (product of sums), canonical algebraic equations, minterms and maxterms. Design concept map. 23. Simplify or minimize logic function using software like Minilog.exe. 24. Find the datasheets of the Small and Medium Scale of Integration (SSI and MSI) integrated circuits. 25. Explain the concepts of flat design and hierarchical design (build using signals and components and their instantiation in VHDL language). 26. Simulate a logic circuit using ModelSim or ActiveHDL ----------------------------1 2 http://digsys.upc.es/ed//CSD/prob/problem_solution-basic_criteria_en.pdf http://tams-www.informatik.uni-hamburg.de/applets/hades/webdemos/docs/tutorial.pdf 2 27. Design and use standard combinational circuit building blocks (at least one of them): multiplexers (or data selectors), demultiplexers (or distributors), binary decoders and encoders, decoders for hexadecimal to seven-segment LED displays, code converters, adders, comparators, etc. 28. Produce a concept map (or a mind map) to explain a topic on the subject, for instance, explain the advantages of using hardware description languages instead of electronic gate-level schematics. 29. Organise a plan for developing the exercise and being able to work efficiently cooperating in a team of 3 members using the proposed methodology. 30. Analyse your own individual and group study time. 31. Produce a quality written solution; for example, document your work using a predefined word processor template and utilities: spelling and grammar, chapter enumeration, page headers and footers, hyperlinks, cross-references, figure captions, text styles, etc., for a given exercise, control or any other assignment, using the given instructions. 32. Assess the own or the group learning progression and the quality of the deliverables. ----------------------------- 33. Read the basics of the “simple machine” already studied in previous subjects on computers. Produce block diagrams for designing the combinational entities in the “simple machine” (ALU and program address generator). 34. Programming subtractions by means of a series of simpler operations (this is a sequential algorithm). 35. Install Altera Quartus II, Lattice Diamond, or Xilinx ISE design tools to implement VHDL-only projects. Run demonstration examples to check the software. Use register transfer level (RTL) and technology views as a help to debug the design through the synthesis process and to clarify the VHDL programming style. 36. Explain by means of a concept map or a power point presentation, the basic technological details of a CPLD or a FPGA and the way they are programmed. ----------------------------- 37. Design a VHDL project for the design of the ALU using elemental blocks as components in a topdown hierarchical and structured design. 38. Install (if not yet for EX1B) the ModelSim or ActiveHDL simulators to verify the VHDL project. Run a demonstration example to check the software. Verify the ALU and the other combinational designs performing functional simulations. ----------------------------- 39. Run the design flow, which essentially consist of: (1) VHDL source files; (2) functional simulation; (3) pin assignment; (4) synthesis; (4) gate-level simulation; (5) device programming; and (6) prototype verification. Implement and check the final design into a CPLD/FPGA training board. ----------------------------- 40. Write and share through the Internet (your Google Sites ePortfolio) a written solution to the problem which has to follow this template (as in EX1). The quality criteria from this document have to be also considered when designing the project. Complement also the planning schedule, your self-assessment mark and your reflections, and remember to sum up your study time using the spreadsheet which can be viewed at your ePortfolio. ----------------------------- Chapter 2 topics 41. Explain the FSM architecture consisting of: (1) the state register, (2) the next state logic and (3) the output logic. 42. Explain the use of the state diagram and the timing diagram to specify sequential systems and to speed to writing of TCL macros. 43. Specify FSM coding styles “sequencial”, “gray”, onehot”, etc in VHDL using ATTRIBUTE statements. 3 44. Explain the use of the special signals CLK and CD. 45. Identify the all the blocks, which are written as processes, in the VHDL file to describe FSM for the basic BCD counter. 46. Use the Quartus II tool: state machine netlist to produce automatically a state diagram from the VHDL listing. 47. Do gate-level simulations in ModelSim using VHO and DSO files. A view on the structural flattened circuit generated by the synthesiser (technology map viewer). 48. Installation and use of the Active-HDL Lattice Edition or the ModelSim Altera Edition simulators. ----------------------------- 49. Design a structured synchronous crystal oscillator frequency divider using expandable counters and other basic components. 50. Design a toggle flip-flop (T-FF) to square pulsed signals or to divide by two the input frequencies. 51. Generate a real-time square waveform of 1Hz from a high frequency crystal oscillator. 52. Use the oscilloscope and other laboratory instruments to measure digital signals’ parameters like frequency, period, propagation delay, power dissipation, etc. ----------------------------- 53. Design basic sequential blocks like a parallel data register, a Johnson counter, a one-hot counter, a shift register, etc. ----------------------------- 54. Explain how a matrix keypad encoder works and design one of them for a 16 keys keypad. 55. Other simple FSM-based applications: a push-button debouncing filter 56. A LED sequencer. Chapter 3 topics 57. Explain the concept of a datapath consisting of an ALU, or other elements which generate or process information and data, and registers or memory for the operands and results. 58. Explain the concept of “flags” or operation indicators and list the most common flags. 59. Explain the concept of control unit based in the application of a FSM, the processor’s brain, the block that will generate control signals for the datapath block in order to execute an algorithm or a sequence of operations. 60. Analyse the complexity and feasible implementation of every project specification. 61. Develop a complex project following the strategy of starting a simple machine and complicating it step by step until all the project specifications are met. 62. Design digital programmable timers 63. Plan auxiliary analogue circuits for the project, for example, the proximity sensors (metal detectors) ----------------------------- 64. Use a VHDL test bench entity to automate the simulation process. 65. Automate a test bench simulation process by means of the ASSERT and REPORT statements. ----------------------------- 66. Do an oral presentation consisting of a few slides to explain the project conception, development, implementation and results. Chapter 4 topics 67. Identify and list commercial microcontrollers and their manufacturers. 68. Search books and the Internet to analyse information about microcontroller chips and their applications (web portals or electronic magazines on the subject of microcontrollers). 69. Explain the basics of a microcontroller-based embedded system. 70. Draw the typical design flow for a microcontroller-based application: concept, hardware, program flow diagrams, coding in assembler or C, Proteus VSM simulation, prototype using evaluation board, verification, in-circuit debugging or microcontroller emulation, PCB design and production. 4 71. Analyse the architecture of an 8-bit microcontroller like the PIC16F877A and describe their main blocks and peripherals. 72. Explain why a microprocessor (CPU) can be considered a programmable dedicated processor from Chapter III. Explain the roles of the EEPROM program memory and the RAM memory. 73. Explain the way to program I/O ports. 74. Explain the way to program the Timer0. 75. Analyse simple applications in assembler or C and deduce the program flowchart from the written code. ----------------------------- 76. Analyse the Heads or Tails game, an example on programming in FSM style: a. b. c. d. e. f. Plan a microcontroller application as if it were a simple FSM or a dedicated processor from Chapters II and III respectively. This is: i. General schematic or top block diagram. ii. Internal architecture using components and signals (and control unit + datapath if it is the case) iii. State diagram for the FSM Explain the role of Timer0 as the FSM clock generator. Draw a program flowchart for every function (interrupt service routine, output logic, future state logic) Convert the program flowchart in C (or in assembler, if it were the case) Run the application using the virtual PICDEM 2 plus board. Download the configuration code to the training board, using for example the In Circuit Debugger/programmer ICD2, and measure and characterise the project using laboratory instrumentation. ----------------------------- 77. Plan and develop through the design flow an example application such as a one minute digital timer using C, the PIC16F877A, and the PICDEM 2 plus board. Use in this project other peripherals like the LCD display and the Timer 1. 78. Do a 10 minutes Power Point oral presentation of the application project consisting of a set of 12 slides maximum. 79. Assess the oral presentation of the other cooperative groups in class considering all the assessment criteria written in the rubric.