DOCX

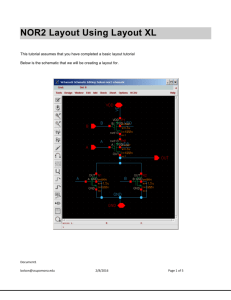

Lab 1: Schematic and Layout of a NAND gate

This document contains instructions on how to:

Make a layout for your NAND gate.

Run a DRC and LVS

Extract your circuit with capacitive parasitics.

How to simulate using your extracted NAND gate.

Note : Go through the whole document before you start. You will save time in the long run

Part B: Procedure

Create layout view.

1.

Make sure that Lab1 and the NAND cell view are highlighted in the “Library

Manager” and from the “File” drop down menu select “New -> Cell View”

2.

In the “Create New File” window that pops up, make sure that: a.

“Library Name” is Lab1 b.

“Cell Name” is NAND

3.

Select “Virtuoso” from the “Tool” drop down menu (it’s the last item on the list) and make sure that the view name is “layout”

4.

Click “OK”

5.

Close the “About what’s New Window”.

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

1

Virtuoso Layout Editor

Virtuoso Layout Editor is the layout editor of the Cadence design tools. Commonly used functions can be accessed through a button bar on the left side of the editor.

Browse through the various menus to familiarize yourself with menus, items, and shortcuts. In preparation for drawing our design in the 0.18 μm process, the grid of

Virtuoso needs to be set to match the spacing required for the target technology. Execute the following commands to set the grid appropriately: a.

Select Options -> Display in the Virtuoso window. The Display Options window appears. b.

Set the following fields in the Display Options window: i.

Minor Spacing: 0.01, ii.

Major Spacing: 0.1, iii.

X Snap Spacing: 0.01, iv.

Y Snap Spacing: 0.01, v.

Display Levels:

1. Start: 0, and

2. Stop: 20, and vi.

Pin Names: On, and vii.

Click Save To in the Display Options window. c.

Click OK in the Display Options window to close it; d.

Select Options -> Layout Editor in the Virtuoso window. The Layout Editor

Options window is displayed; e.

Set the following fields in the Layout Editor Options window:

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

2

i.

Aperture: 0.01, and ii.

Click Save To in the Layout Editor Options window. The aperture setting controls how close you have to be to snap to an object. f.

Click OK in the Layout Editor Options window to close it.

There are a few commands that will be useful to you while you are drawing the design: zoom, ruler and clear rulers. Listed below are the commands to execute them: a.

Zoom: select Window -> Zoom -> To Grid to get closer to the working dimensions; b.

Ruler: Click the ruler icon. Click and drag the mouse across the drawing area of the Virtuoso window. It displays a ruler. To finish the ruler, you need to click the end point as well. Note that rulers are created only horizontal or vertical; and c.

Remove Rulers: To remove the rulers, select Window -> Clear All Rulers from the Virtuoso window. Unfortunately, you have to remove all rulers at once. They can not be removed one at a time.

Now you are ready to create your layout.

Adding components to the layout

Technology kits often provide pre-made scalable components (usually called pCells) to match your design requirements (i.e. to match your schematic).

6.

On the left side of the layout editor there are some buttons. Click on the

“Instance” button

7.

Select “Browse” in the “Create Instance” window.

8.

Select the “CMCpcells” library

9.

Select the “spcnmos” cell (it’s an nMOS transistor) and make sure that “layout” is highlighted. Click Close in the Browser window.

10.

Place the nMOS transistor anywhere and then hit Esc to stop placing instances. a.

Note : The transistor pCell is incomplete. A substrate contact must be placed near the transistor.

11.

Click on the transistor

12.

Select “Properties” from the “Edit” pull down menu (short cut is q)

13.

In the “Edit Instance Properties” window select the “Parameter” button. a.

From here you can modify the length and width of the transistor, change the number of fingers, or add a substrate contact (see figures below).

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

3

NMOS

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

PMOS

4

14.

Repeat the steps above to place nMOS and pMOS transistors as shown below.

Ensure that the transistors have the appropriate properties as shown in the previous figures (widths and lengths should match your design).

Draw VDD/GND contacts a.

Highlight “Metal1 | drw” in the “LSW” window b.

In the “Layout Editor” window select “rectangle” from the “Create” pull down menu (short cut is r). c.

Click “Hide” on the “Create Rectangle” pop up window d.

Use the mouse to select a start and end point for the rectangle, make sure you cover the substrate area of pmos/nmos. e.

Choose Create->Pin... from the Virtuoso window . The Create Symbolic

Pin window is displayed; f.

In the Create Symbolic Pin window , set the following fields: i.

Type VDD in the Terminal Names field. Note that this field is case sensitive ii.

In the Mode area, ensure that the radial button sym pin is selected

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

5

iii.

Just below the Mode area, ensure that the radial button Display Pin

Name is selected, iv.

Next to the radial button Display Pin Name , click Display Pin

Name Option, v.

In the Height field of the Pin Name Display window, enter 0.5 and click OK vi.

In the I/O Type area, ensure that the radial button inputoutput is selected, vii.

In the Pin Type area, select metal1_T from the pull down menu, viii.

Click Hide in the Create Symbolic Pin window; g.

Move the mouse over the Virtuoso window and click anywhere on the metal1 rectangle you created to specify where the pin should be placed.

The pin name VDD is displayed; h.

Move the mouse and you see that the name is attached to the square (pin) that you just located. Arbitrarily select a location for the pin name to be displayed and click once; and i.

Type ESC in the Virtuoso window to terminate Create => Pin mode. j.

Repeat the same steps for GND

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

6

Draw input contacts

Refer to the following figure when performing these steps. a.

Highlight “poly1 | drw” in the “LSW” window b.

In the “Layout Editor” window select “rectangle” from the “Create” pull down menu (short cut is r). c.

Click “Hide” on the “Create Rectangle” pop up window d.

Use the mouse to connect poly from pmos1 to nmos1. Repeat same thing for pmos2/nmos2. e.

Choose Create->contact... from the Virtuoso window . The Create

Contact is displayed; f.

In the Create Contact window , set the following fields: i.

In the Contact Type , make sure the M1-POLY1 is selected. ii.

Click Hide in the Create Contact window (if it appears); g.

Move the mouse over the Virtuoso window and click on the poly to place two contacts. h.

Type ESC in the Virtuoso window to terminate Create => Contact mode. i.

Highlight “Metal1” in the “LSW” window j.

In the “Layout Editor” window select “Path” from the “Create” pull down menu (short cut is p). k.

Click “Hide” on the “Create Path” pop up window (if it appears) l.

Use the mouse to select a start point for the path (by single-clicking) and end point (by double-clicking). You can add more points along the path by single-clicking along the way. m.

Add input pins A and B.

Draw output contact

Once again, refer to the following figure for these steps. a.

Draw a path to connect Source/Drain of pmos/nmos to output C. b.

Add output pin as before.

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

7

Important Hints, Tips and Rules

It’s usually a good idea to make standard cell layouts so you can easily connect different layouts together to build circuits (use the picture on the next page as an example). Cells are normally connected side by side (not top to bottom). o The cells should be exactly 12.37 microns in height, the width can vary

(you can use the ruler to measure the dimensions of objects or map out an area to put an object down. The short cut is r in the Layout editor window) o The positive rail is on top (left to right), negative rail (or ground is on the bottom) and they should each be a minimum of 0.78 microns in height. o Make sure the rails stick out on either side so you don’t violate any design rules when you connect cells together o Use the top metal layer for the power rails (metal 6 and/or metal 5) o Input pins are on the left and output pins on the right. Use metal 4 on the pins so you can connect from cell to cell in metal 4. o Don’t place the I/O pins at the edge of your cell. You want them to be a little recessed so that they don’t interfere with any other cells

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

8

o Also, make your power rails extend a bit past the edge of your circuit

(horizontally) so that your cells don’t over lap. o Do all interconnect (internal cell connections) in metal 1, and if you need to crossover or are too close to a metal trace you can switch to metal 2 or metal 3. o Put all PMOS transistors on top and NMOS on the bottom o Make the pmos nwell as wide as the power rail so that you have one large nwell when you connect multiple cells together.

Try not to run metal lines that are close together in parallel, you get lots of crosstalk if you do.

To connect to the poly (gate of a transistor) you need a metal 1 to poly contact

(look in the create pull down menu). o Any long traces should be done in metal 1 if you can (the poly is highly resistive).

You need to use vias to connect metal lines that are on different layers (I.e. Metal

1 to Metal 2). o The vias are in the create pull down menu under contacts.

Vias and contacts are highly resistive. You can’t usually go wrong with putting down as many as you can. o Remember, size is important. Too big or too small is bad.

Don’t forget to ground all your substrate contacts for NMOS transistors and use the rail if the transistor is a PMOS.

Some info on traces: o Wide metal lines have less resistance but more capacitance o Thin metal lines have lots of inductance and may not be able to handle the necessary current. o The design rules will have information that will help you choose the metal widths (they are in the following directory: /CMC/kits/cmosp18/doc/). o As a general rule:

Power and ground lines can be thick, metal interconnect is generally thin o Don’t make 90-degree turns, use 45 degrees. A 90-degree turn puts a lot of electrical stress on the corner (not as important at slow speeds but can be very important in the GHz range).

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

9

There are a lot of design rules about spacing between various layers, as well as sizes of things like contacts and how wide a metal line can be (without slotting), so run DRC often (see the next section).

At this point you should have all the tools necessary to create the NAND layout. The next step is to run a DRC.

DRC

A design rule check (DRC) makes sure that your design complies with the fabrication guidelines (spacing, sizing, required layers, etc). In other words it makes sure that the fabrication facility can build what you have designed. It also does some simple checks to insure you haven’t made any basic errors. a.

Note

: passing the DRC doesn’t mean your design works.

15.

Using a “Terminal” window make a DRC sub directory under your project directory (use mkdir).

16.

In the “Layout Editor” select the “Verify -> DRC” menu option

17.

Make sure in the Switch Names you select “ no_antenna_check

”.

18.

Make sure that the DRC rules file is “divaDRC.rul”

19.

Click OK

20.

The DRC “Summary of rule violations” appears in the “icfb” window. If you have

0 rule violations then all is good, otherwise you will be required to hunt down the errors and try and correct them. a.

You can use the “Markers “ sub menu under the “verify” pull down menu to “Find” errors in your layout or “Explain” the errors in more detail b.

Note : The error messages can be confusing sometimes, but usually with a little thought you can narrow down the problem

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

10

Common DRC error hints and tips

21.

Minimum metal sizes for metals 1 through 5 are 0.45 microns x 0.45 microns

22.

Minimum metal size for metal 6 is 0.66 microns x 0.66 microns

23.

Minimum widths for metal 1 through metal 5 is 0.28 microns

24.

Minimum width for metal 6 is 0.57 microns

25.

When placing vias and contacts be sure to have one of each type to avoid a size error (I.e. Two of the same vias placed on top of each other but with an offset looks like a larger via ) a.

Note: the metal size for vias is usually too small (see above for minimum metal sizes)

LVS

You can now LVS your circuit. The LVS compares you schematic to your layout (using the extracted view) and makes sure that you haven’t made any inadvertent changes/errors.

26.

Using a terminal window make an LVS sub directory under your project directory

(use mkdir).

27.

In the Layout Editor select the “Verify -> Extract” menu option

28.

In the “Extractor” window click OK

29.

Make sure there are no errors in the “icfb” window

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

11

30.

In the “Layout Editor” select the “Verify -> LVS” pull down menu

31.

Use the “Browse” buttons to select your run directory (the one you made in step

26), the NAND Schematic, and Extracted views.

32.

Make sure that the rules file is “divaLVS.rul” and the Rules Library is cmosp18

33.

Click the “Run” button (this may take some time to run).

34.

Click “OK” in the pop up window. The window will tell you if the LVS ran successfully or not

35.

Click the “Output” button in the “LVS” window

36.

The “LVS Output” file will tell you if the layout and schematic match. If all is good you can proceed to the extraction with parasitics section. Otherwise you will be required to hunt down the errors and try and correct them. a.

The output file usually gives enough information to correct the error (i.e. it tells you what’s wrong and why).

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

12

Hints for Common LVS problems

37.

Watch out for pin types and labels. b.

Make sure that the layout pin types match your schematic pin types c.

The LVS tool is case sensitive. Pin “a” is not the same as pin “A”

38.

The transistors in the layout and schematic must have the same number of fingers.

In your schematic you may have to use multiple transistors in parallel (the pcells in the layout allow you to specify the number of fingers but the transistors in the schematic might not).

39.

Make sure that pin placement in layout matches the pin placement in schematic.

Extracted view with parasitics

The extracted view is a version of your layout that can be used in simulation, probed for connectivity and compared to your schematic using an LVS tool. You can also add parasitic capacitance and resistance to the extracted view. Parasitics are the undesired

(can often be used as part of the design) resistance, capacitance and inductance of your circuit. A good designer takes the parasitics into account when designing the circuit.

40.

In the “Layout Editor” select the “Verify -> Extract” pull down menu

41.

Click on the “Set Switches” button to select the capacitive parasitics to include in your extracted view.

42.

Click OK in the Extractor window.

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

13

The extracted view should appear in the Library Manager as part of your NAND cell

Simulation

43.

Open your testNAND Schematic and select the “Tools -> Analog Environment” pull down menu

44.

In the “Analog design Environment” window select “Setup -> Environment…”

45.

Add “extracted” to the “Switch View” list (make sure it’s the first item on the list)

46.

Run simulations as before in Part A.

Hints

Save your work often, the software that connects you with the UNIX stations has been known to crash.

Run DRC often. The more things you have the more errors your going to get. It’s easier to deal with the errors as they come and not in a bunch at the end.

Most things in the layout editor have a short cut key. The short cut really speeds things up. The same goes with the schematic editor

Don’t forget to use pins in your layout. The LVS will look for them to compare with your schematic (make sure that the schematic and the layout have the same type of pin). The pins are in the create pull down menu.

Your layout does not have to look like your schematic. It just has to match electrically. So placement of components can change to help reduce size.

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

14

Symmetry can be important (more so at high frequency). Try to make your designs symmetrical (i.e. differential lines should be the same length and have the same number of turns).

Every time you use a tool you get a pop up window with the tools features. This can be annoying if all you want to do is draw a trace or place a component. You can stop the pop up window by: o In the “icfb” window select the “User Preferences” from the “Options” pull down. o De-select “Options display when commands start”. o Click Ok o If you want the option pop up window hit F3

ELEC 4708: Lab 1 Part B procedure

Version/Date: 2013-01-17

15