Lab 13

advertisement

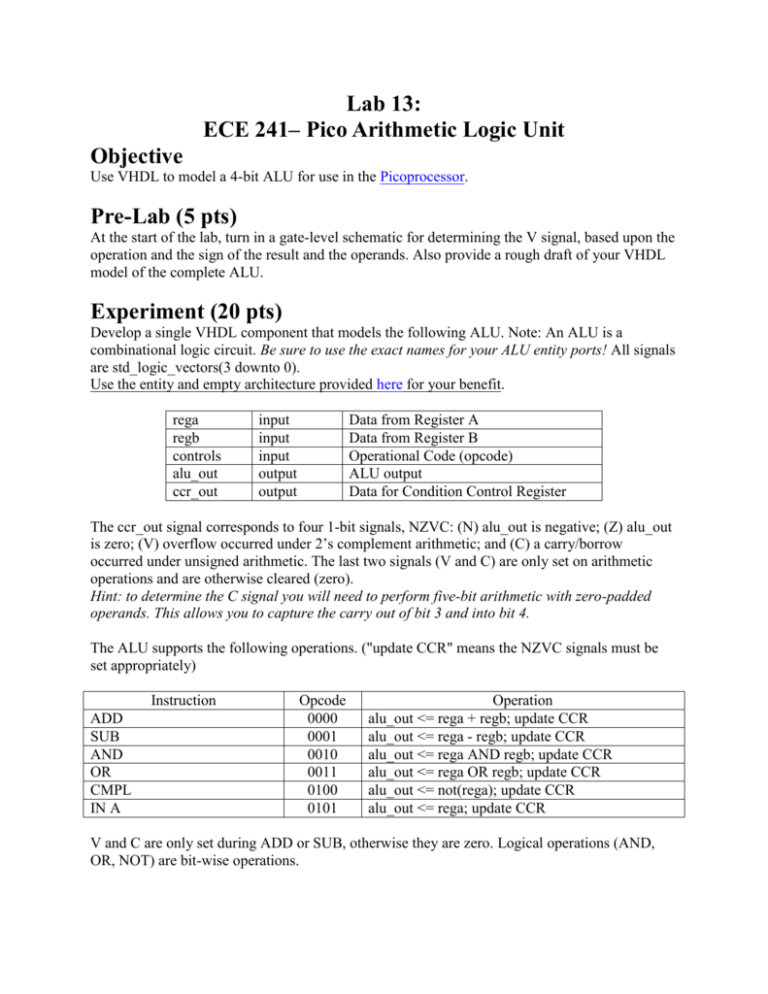

Lab 13: ECE 241– Pico Arithmetic Logic Unit Objective Use VHDL to model a 4-bit ALU for use in the Picoprocessor. Pre-Lab (5 pts) At the start of the lab, turn in a gate-level schematic for determining the V signal, based upon the operation and the sign of the result and the operands. Also provide a rough draft of your VHDL model of the complete ALU. Experiment (20 pts) Develop a single VHDL component that models the following ALU. Note: An ALU is a combinational logic circuit. Be sure to use the exact names for your ALU entity ports! All signals are std_logic_vectors(3 downto 0). Use the entity and empty architecture provided here for your benefit. rega regb controls alu_out ccr_out input input input output output Data from Register A Data from Register B Operational Code (opcode) ALU output Data for Condition Control Register The ccr_out signal corresponds to four 1-bit signals, NZVC: (N) alu_out is negative; (Z) alu_out is zero; (V) overflow occurred under 2’s complement arithmetic; and (C) a carry/borrow occurred under unsigned arithmetic. The last two signals (V and C) are only set on arithmetic operations and are otherwise cleared (zero). Hint: to determine the C signal you will need to perform five-bit arithmetic with zero-padded operands. This allows you to capture the carry out of bit 3 and into bit 4. The ALU supports the following operations. ("update CCR" means the NZVC signals must be set appropriately) Instruction ADD SUB AND OR CMPL IN A Opcode 0000 0001 0010 0011 0100 0101 Operation alu_out <= rega + regb; update CCR alu_out <= rega - regb; update CCR alu_out <= rega AND regb; update CCR alu_out <= rega OR regb; update CCR alu_out <= not(rega); update CCR alu_out <= rega; update CCR V and C are only set during ADD or SUB, otherwise they are zero. Logical operations (AND, OR, NOT) are bit-wise operations. Verify your design, post-route, through simulation and demonstrate the simulation to the instructors. Your simulation must verify each instruction, including test patterns which exercise each of the four conditions for both ADD and SUB: V=C=0; V=1, C=0; V=0, C=1; and C=V=1. Label all simulations neatly. No need to demonstrate on the board. Report (5 pts) Turn in a brief, professional report that describes your design process and results. Comment on any observations during simulation. Elaborate on any problems you encountered. Finally, attach to your report hardcopies of your VHDL, post-route simulations, and the signed design summary.