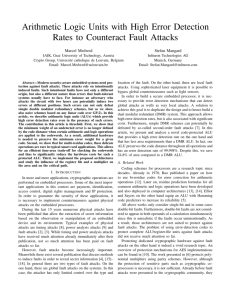

doc

advertisement

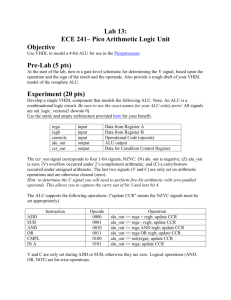

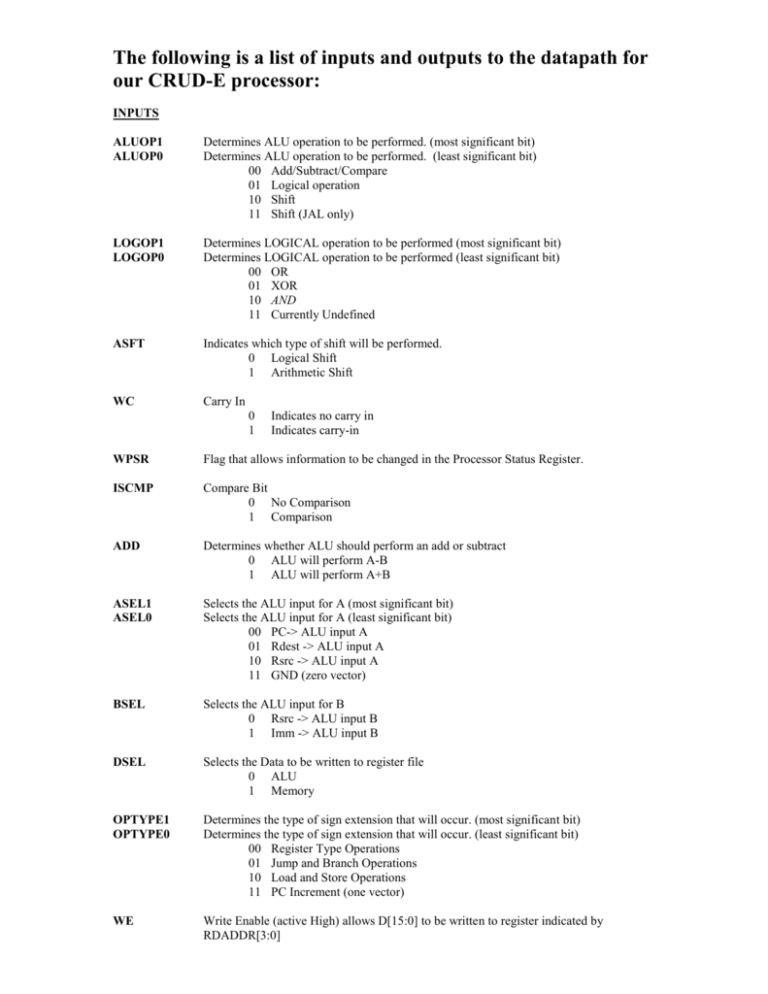

The following is a list of inputs and outputs to the datapath for our CRUD-E processor: INPUTS ALUOP1 ALUOP0 Determines ALU operation to be performed. (most significant bit) Determines ALU operation to be performed. (least significant bit) 00 Add/Subtract/Compare 01 Logical operation 10 Shift 11 Shift (JAL only) LOGOP1 LOGOP0 Determines LOGICAL operation to be performed (most significant bit) Determines LOGICAL operation to be performed (least significant bit) 00 OR 01 XOR 10 AND 11 Currently Undefined ASFT Indicates which type of shift will be performed. 0 Logical Shift 1 Arithmetic Shift WC Carry In 0 1 Indicates no carry in Indicates carry-in WPSR Flag that allows information to be changed in the Processor Status Register. ISCMP Compare Bit 0 No Comparison 1 Comparison ADD Determines whether ALU should perform an add or subtract 0 ALU will perform A-B 1 ALU will perform A+B ASEL1 ASEL0 Selects the ALU input for A (most significant bit) Selects the ALU input for A (least significant bit) 00 PC-> ALU input A 01 Rdest -> ALU input A 10 Rsrc -> ALU input A 11 GND (zero vector) BSEL Selects the ALU input for B 0 Rsrc -> ALU input B 1 Imm -> ALU input B DSEL Selects the Data to be written to register file 0 ALU 1 Memory OPTYPE1 OPTYPE0 Determines the type of sign extension that will occur. (most significant bit) Determines the type of sign extension that will occur. (least significant bit) 00 Register Type Operations 01 Jump and Branch Operations 10 Load and Store Operations 11 PC Increment (one vector) WE Write Enable (active High) allows D[15:0] to be written to register indicated by RDADDR[3:0] LOADPC PC write enable LOADMAR Memory Address Register write enable LOADMDR Memory Data Register write enable LOADIR Instruction Register write enable ISFETCH Asserted if fetching address of instruction for PC. ISMEDIUM Asserted if instruction being executed is a medium immediate type. READ Read Bit 0 1 WRITE Write Bit 0 1 Don’t Read From Memory Read From Memory Don’t Write To Memory Write To Memory ALULOAD ALU Register write enable IMMSHIFT Selects between register or immediate type shift 0 Direction of shift controlled by value in register 1 Direction of shift controlled by value in immediate field LOADIMM Immediate Register write enable CLEAR If asserted then all information is cleared from the data path. CLK Clock of the entire circuit. OUTPUTS IROUT[15:0] 16 bit instruction from the Instruction Register. Z Set if A == B reset otherwise. L Set if A < B (Unsigned) reset otherwise. N Set if A < B (Signed) reset otherwise. F Set if ALU Add/Sub creates an overflow, or other errors C Set if ALU Add/Sub results in a carry DONE Set if all operations (read/writes) to/from memory are complete. BRANCH Asserted if specified condition is true.