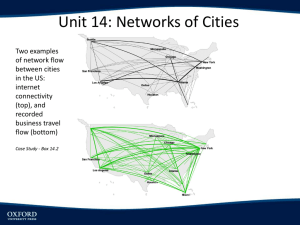

Annex 1 file - digsys.upc.edu

advertisement

EX2: Designing sequential systems using FSM 1.1 1 Annex 1 Here, at this level of knowledge, you can design many more sequential blocks, thus, if it is of your interest, here you are a list of other similar applications which may be found in previous or future courses. 1.1 Annex 1 ................................................................................................................................................... 1 1.1.1 Designing the 16-key keypad scanning decoder for the Altera UP2 ............................................... 1 1.1.2 Debouncing keys .............................................................................. Error! Bookmark not defined. 1.1.3 A simple LED sequencer ................................................................................................................. 3 1.1.1 Designing the 16-key keypad scanning decoder for the Altera UP2 Keypad characteristics and wiring Find the characteristics of a commercial 16-key keypad like the one represented in Fig. 1. You may run the project downloading the Proteus design from the web page. 9 TS B 4 5 6 HS C 1 2 3 MS 24H/ AM-PM 1 D 0 ENTER SS 4 8 3 7 2 A Fig. 1 Example of a commercial matrix keypad and the value obtained when pressing key “E” while scanning (setting a “0”) at RowD. Indeed, the DEC2:4 will be an integrated part of the scanning chip, and so, only the 4 pull-up resistors are the necessary hardware for the interface. An adapted keyboard can be easily obtained sticking new plastic labels on the keys (in Proteus-VSM, you can decompose a component, make the required modifications and adding the new component to the library) The keyboard will be available in the laboratory and ready to be connected to the FLEX_EXPAN_A connector of the UP2 board. The pin assignment is as follows: Row : Column : OUT std_logic_vector(3 downto 0); IN std_logic_vector(3 downto 0); -- Flex_EXPAN (41, 43, 45, 47) == pins (79, 81, 83, 86) -- Flex_EXPAN (49, 51, 53, 55) == pins (88, 95, 98, 100) -- Flex_EXPAN (57, 59) == VCC Plan and code in VHDL the state diagram for the component Invent what is usually called intellectual property (IP): a scanning chip for the 16-key keypad, which in some way has to be similar the commercial chip MM74C922. The chip has to be based essentially in a VHDL-written FSM running a state diagram for scanning rows and decoding the key pressed. Fig. 2 shows an approximate block for the entity suggesting the number of inputs and outputs needed. Fig. 2 RTL netlist view for the keyboard decoder identified as a component Write the VHDL code for the chip’s state diagram and verify by a functional simulation. Compile the project and use the Quartus II tool: State diagram netlist to verify if the state diagram that implements the FSM coincides with the one specified. EETAC: Digital Circuits and Systems 2 In case of having used any of the projects in Unit 2.8, which really represents a complete solution of the previous section 0, fix the problem that appears when clicking simultaneously 2 keys of the same column. For example, the solution can be to introduce a final tri-state buffer to deactivate/disconnect all the rows which are not driven at logic low. See Fig. 3. Fig. 3 A short-circuit is produced when clicking several keys in the same column. Driving the row through tri-state buffers can be a possible solution to this problem Complete the project adding clock and display modules Complete the project adding: (1) a hex-7segment decoder so that the hexadecimal code captured when pressing key will be displayed into the 7 segment display of the UP2 board; (b) the frequency divider from Section Error! Reference source not found., thus the keyboard scanner entity will be driven by the 200 Hz pulse aveform. Synthesise the matrix keyboard application into a CPLD or a FPGA chip Synthesise the module into the CPLD 7128S of the UP2 board and test it. (1) (2) (3) VHDL source files Functional simulation (*.vhd) RTL view (4) Device selection, pin assignment (constraints) and project synthesis (8) (7) (6) (5) Verification using a prototype board Device programming Gate-level simulation (*.vho /*sdf) Technology map viewer Fig. 4 Main steps in the programmable chip design flow EX2: Designing sequential systems using FSM 1.1.2 3 A simple LED sequencer We want to design a simple driver to shown a sequence of movement, clockwise and counter-clockwise, in a single 7-segment display. In Fig. 5 the main diagram for this application is shown. The circuit components are basically: (1) a clock to produce a rectangular wave with a given frequency, let’s take 5 Hz; (2) the digital system; and (3) the 7-segment display (common cathode) with its current-limiting resistors. Fig. 5 Block diagram for the indicator of sequence of movement The system has to work as specified in Fig. 6, depending on the logic levels of the synchronous input signals: UD_L (Up (active high) /Down (active-low) and ST (stop). ST signal has precedence over UD_L. Design the circuit based on the standard FSM style, and implement a prototype for the CPLD or FPGA chip at the development UP2 Altera board, or for the LC4128V Lattice chip at die Experimentierplatine für die Digitaltechnik. t a) b) Fig. 6 a) Sequence of switching LED segments for UD_L = ‘1’ (up) and ST = ‘0’; b) Indication for ST = ‘1’