VHDL Dice Game (Craps) Lab for FPGA

advertisement

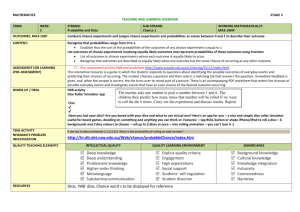

CEC 222 Digital Electronics Lab Spring 2015 Lab 11: A Dice Game (Craps) Lab Overview: In this lab, you will developing VHDL code and implementing it on your FPGA to replicate the dice game loosely referred to as “craps.” After successfully completing this two week duration lab a career at the craps tables in Las Vegas awaits!! The game is played as follows: 1. First Roll: Two die are thrown The player wins if the sum is 7 or 11, The player loses if the sum is 2, 3, or 12, otherwise The initial sum is stored and referred to as the “point” and he/she must throw again. 2. Second or Subsequent Roll: Two die are thrown The player wins if the sum is equal to his/her point, The player loses if the sum is equal to 7, otherwise He/she must roll again until a win or loss. A potential top-level architectural diagram of the overall solution might be given as shown in Figure 1. Figure 1 A top-level architectural diagram of a potential solution Lab 11: A Dice Game (Craps) Page 1 of 5 CEC 222 Digital Electronics Lab Spring 2015 PRELAB Develop the VHDL code to produce the two dice values. Your two inputs will be the 50 MHz clock and the debounced Roll signal and your two outputs, the dice values, roll_1 and roll_2. HINT: Look at the VHDL code from Mon, March 30 (Method2_Moore.vhd). Main Experiment (100%) The game begins with the player depressing the roll button (“Rb”). We can use any one of the four momentary pushbuttons on our FPGA board for this purpose (e.g., BTN3). Upon release of the roll button the two rightmost 7-segment displays should display our dice values (i.e., each a number from 1 to 6). Step 1.a: Build a Counter/Counters to synthesize the rolling of two dice To generate the outcome of rolling two dice you must preserve the randomness of the process. One way of doing this is to drive a counter(s) with the 50 MHz clock and use the duration of the roll button being depressed as a random interval. Vcc A normally-open SPST momentary switch Roll = BTN3 The “Roll” signal is intended to be a “debounced” version of the “Rb” signal, however, if you are using the Digilent BASYS 2 FPGA board the pushbutton switches (BTN3 to BTN0) seem to be “debounced” (likely analog circuitry), hence, the two signals can be one and the same (i.e., Roll = Rb). Task 1. Use the oscilloscope of your Analog Discovery to capture a rapid press and release of BTN3. One way of doing this is to create a simple schematic with only a buffer connecting BTN3 to one of the output pins (e.g., port JA pin 1). Be sure to annotate your screen capture. Use this test to confirm that the signal is actually debounced. How could you “clean-up” this signal? Question 1. What is the shortest duration of a button depression (i.e., how fast can you press and release BTN3) and how many 50 MHz clock cycles does that correspond to? Task 2. Enter your code to synthesize the rolling of two dice (from prelab) and check for errors. Task 3. Simulate your code and then implement your design on the FPGA board. Be sure to display the two dice values on your seven Roll segment display(s). NOTE that VHDL code was provided on the lab webpage to display the dice (disp_dice.vhd). Task 4. Record the outcomes for 20 consecutive rolls. Do the outcomes (i.e., dice values) seem random? Task 5. Include a code block to add the two dice values into the value “Sum” and demonstrate your random dice rolls to the instructor or lab TA. Lab 11: A Dice Game (Craps) Page 2 of 5 CEC 222 Digital Electronics Lab Spring 2015 Step 1.b: Step 2: Remaining I/O and logic for the dice game A top-level interpretation of the input/output structure for the main control block of the dice game can be presented as illustrated in Figure 2. Inputs: o D7 = 1 is sum of dice is 7 o D711 = 1 if sum of dice is 7 or 11 o D2312 = 1 if sum of dice is 2, 3, or 12 o Eq = 1 if sum of dice is equal to the point register (i.e., prior sum = current sum) o Rb = 1 when roll button is pressed (external input BTN3) o Reset = Async reset button (external input BTN0) Outputs: o Roll = 1 is the counter enable (= Rb) o Sp = 1 causes sum to be stored in store point register o Win = 1 denotes a win (external output LED0) o Lose = 1 denotes a loss (external output LED7) Figure 2 The input/output structure for the remainder of the dice game. The overall logic for the dice game can be described via a state graph. A potential Mealy State Machine is given in Figure 3. Lab 11: A Dice Game (Craps) Page 3 of 5 CEC 222 Digital Electronics Lab Clock on Falling Edge of 50 MHz clock Spring 2015 Start A Mealy Machine Rb/0,0 SWin Win SRoll1 SLose Lose Swait Rb/0,0 SRoll2 Outputs: o Roll = 1 enables the counter o Sp RISING edge latches “point” o Win = 1 denotes a win o Lose = 1 denotes a loss Figure 3 A potential Mealy State Machine of the dice game. A potential Moore State Machine is given in Figure 4. A Moore Machine Clock on Falling Edge of delayed Roll signal SRoll1 Sp SWin Win SRoll2 SLose Lose Outputs: o Sp FALLING edge latches “point” o Win = 1 denotes a win o Lose = 1 denotes a loss Figure 4 A potential Moore State Machine of the dice game. Lab 11: A Dice Game (Craps) Page 4 of 5 CEC 222 Digital Electronics Lab Spring 2015 Implement your version of the state graph in VHDL and display Win on LED1 and a LOSS on LED0 (i.e., illuminate LED1 if Win = ‘1’ or illuminate LED0 if Lose = ‘1’. Aspects to consider: How will you implement the point register? How do I break this problem into smaller sub-problems? When is the value of the Sum “stable”? Deliverables 1. Address all of the questions/tasks described in the above (much of this should go into Section 2. Intro and/or Section 3. Theory within your lab report). 2. Formal Lab Report a. Show your commented VHDL code and explain how it works (place code in the Appendix) b. Provide photos of your FPGA board (show 7-segment display and Win/Lose LEDs) corresponding to two consecutive games. Note that a single game may correspond to more than one roll of the dice (provide a photo for each dice roll). 3. Extra-Credit: Display the cumulative number of Wins and Losses on the two remaining 7-segment displays. Lab 11: A Dice Game (Craps) Page 5 of 5