S09_P3_Roa_Fernando

advertisement

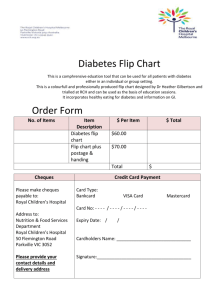

Low Cost Solutions for Cu Pillar Flipchip Packages Fernando Roa Amkor Technology, Inc. 2045 East Innovation Circle Tempe, AZ 85284 Ph: 480 786 7586; Fax: 480 821 1713 Email: Fernando.roa@amkor.com ABSTRACT Flip chip technology has been greatly advanced over recent years with advances in all areas related to this process: better engineering materials for the manufacture of substrates or encapsulants, more controlled processes for pick and place, bonding and reflowing, finer geometries for bonding surfaces, improved finishes, and revolutionary changes such as the recent prevalence of Copper Pillar bumps. Many important applications in the modern world are being enabled with advanced packaging which has extended the typical flip chip packaging solutions to encompass wide ranging solutions for a variety of fields from mobility to automotive and beyond to IOT. As a next evolutionary step in this long range evolution of flip chip, this paper will focus on recent developments that have allowed us to offer lower cost flip chip solutions leveraging our great wealth of technology know how, abundant low cost infrastructure solutions and recent developments in very low cost alternative materials for encapsulation and substrates. In particular, we are looking to demonstrate in this paper that with the right combination of process features, design trade-offs, creative processing combinations, it is possible to leverage flip chip technology, in particular using copper pillars, for low cost packaging solutions in a variety of fields where other incumbent packaging technologies have been predominant. We’ll demonstrate with practical examples form our recent experience, that this alternative flip chip solution will not only respond to the technical requirements of mechanical robustness and long term reliability but also offer an attractive financial alternative to these existing technologies with the added benefit of leveraging learnings and wide understanding of the issues. As a conclusion, we’ll show evidence that there is evidence of a major gap in cost competitive coverage in packaging roadmaps where current prospective solutions are either trapped in IP restrictions, are too costly, or have issues in regards to either yield or long term reliability. Low cost flip chip using copper pillar is shown to be a viable solution to plug this gap without any of these drawbacks and drawing in the same reliable technology currently supporting advanced products for the mobility and communications segments. I. Background Packaging technology is derived from the need to enable the transistors and circuitry in the silicon device to communicate reliably with the external world, typically through the use of an IO expanding media (leadframe, RDL, substrate, interposer, etc.). Many alternatives exist today for packaging a device, each with its own set of nuances and requirements. While is possible to extend most of these alternatives to compete with the other existing solutions, typically each holds to its own typical market segment(s). Thus, for instance, flip chip technology is mainly associated with high performance applications requiring low impedance and very fine patterned features for signal integrity and processing speed. Wafer level solutions tend to be concentrated around the low IO, small body size applications. The other alternative solutions falling somewhere in between. We aim to show in this paper that this needs not to be so for flip chip. Heating + 1. Die Flip & fluxing 3. Flux Cleaning 2. Chip Attach & Reflow 4. Capillary Underfill Figure 1. Simplified process steps for flip chip packaging Flip chip packaging, or as it was initially know, controlled chip collapse connection (C4) technology, has been around for over 40 years and remains a prevalent assembly technique for chip interconnection. In any flip chip solution with conventional reflow, the interconnection process relies in several key properties of the solder materials: surface tension to self-align the chip to the receiving substrate, their melting points to insure easy processability at convenient conditions and the speed at which they form intermetallic with the base metals used for the bonding pads in the device, in insure long term reliability. Figure 1 shows a simplified flip chip process. In this process, the bumped wafers, diced and thinned to final specs, are mounted into a tool which will pick individual die, ‘flip’ it, dip it in a flux reservoir, and then place it on top of the substrate taking care of aligning the fiducials so that the bumps will land on their corresponding bonding pads. The substrate is then send to an oven were a series of zones create a reflow profile where the temperature is progressively increased, first insuring the flux is activated so metal surfaces are cleaned and then progressing till reaching solder melting point, at which point the solder will melt and wet the substrate pad insuring the formation of a conductive joint. After the part exists the oven, it is subject to a cleaning step to remove the flux material. Finally, a last step is to dispense a liquid epoxy material to fill the gaps between bumps under the chip. This material, once cured, protects the bumps from the strong stresses arising from the two materials joined with very dissimilar mechanical properties. Originally, flip chip packages relied mostly on low melting solders (typically Tin Lead eutectic) which enabled the direct interconnection of the chip to the receiving substrate at relatively low temperatures (193’C is the standard melting temp for eutectic solder). Advantages with this approach are multiple: minimum exposure of sensitive circuitry and materials to high temperatures, simpler reflow ovens, available fluxing technology, with environmental restrictions cropping up from many different sectors, a push to extend the technology to an environmentally responsible solution was initiated early in the past decade with the resulting predominance of Tin Silver and Tin Silver Copper alloys. But development never stops, and so, pushed by more aggressive interconnection demands, in particular for mobility segments keen on seeing devices shrink in size and thickness while offering increased signals counts, next step required a fundamental change in bumping technology to enable a bump which would have a much finer patterning resolution, while still able to solder at relatively low temperatures and hopefully leveraging existing equipment. Extending solder bumps to lower bump pitch flip chip packaging was demonstrated unpractical due the tendency of solder materials to lose shape during reflow events which resulted in gross yield losses due to shorting. Thus, typical solder flip chip applications reach a barrier at around 140um or so. To address these conflicting demands, copper pillar was developed at Amkor. The principle being that the Cu portion would allow the pillar to retain its shape during reflow while also helping the interconnection in many other respects: electrically, Cu is a superior conductor than solder and would result in increased current carrying capacity and improved reliability against electromigration. Also, coupled with simultaneous underfilling setting, Cu pillar is a great solution for ILD stress driven by CTE mismatch between silicon and organic interposers. Many other advantages can be derived from the use of Cu pillars vis a vis solder bumps. Much finer geometries possible, see Fig 2 where Cu pillar is currently used also for TSV interconnection with pitches below 20um. Cu pillars can be designed in any conceivable shape, which allows to optimize the bonding area for optimal reliability and yield during bonding, but also examples are shown from using alternative geometries for a variety of reasons: ovals, squares, rectangular bars, etc. Figure 2. Solder vs Cu pillar bump domains Fig. 3 shows a typical CuP bump. Generically, a copper pillar bump is composed of a rigid, not melting column of Cu, topped with tip or cap of solder material. The Cu column height will dictate the collapsed height of the chip after reflow while the solder in the tip will obviously create the metal connection to the substrate metal pad. Figure 3. Typical Amkor copper pillars. Coupled to the Cu pillar bump solution, a novel low ILDstress inducing bonding process, called thermo-compression bonding (TC) was simultaneously developed to address the increasing gap in CTE behavior between leading edge Si gate nodes and substrates. It was noted that 45nm Si and lower tended to exhibit white bumps or mechanical failures particularly affecting the weakest point in the whole connection link, typically the very brittle materials used as dielectrics in the advanced Si processes. Yet, the industry has advanced to extend the process window for conventional reflow to nodes 28nm and below using small incremental changes to the technology which we’ll address in the next section. II. Enabling a low cost flip chip package A. Application spaces for low cost flip chip packages The first task in extending copper pillar flip chip to low cost packaging solutions is to determine which applications this solution will address. Another task required is to determine the competitive landscape in order to be able to compare this technology with other incumbent packaging solutions. As far as application space is concerned and focusing on the mobile phone segment market assuming it provided a good cross sectional view of the semiconductor market as a whole, copper pillar flip chip addresses some of the most challenging, cost-intensive solutions in this landscape today (see Figure 4). At the top end of the FC application spectrum, devices such as baseband engines and application processors for mobile platforms require fast signal transfer rates, great signal integrity and mechanically robust packages; all these needs are well addressed by flip chip packages. Clearly a premium is expected here due to the advanced design rules, materials and processes employed to enable such packages. Fueling these trends are the need for additional functional integration which is simpler and more cost effective to achieve at the back end that if new systems in a chip are designed. So 2.5 and 3.0 architectures will still drive a lot of innovation in flip chip. Those, however, are not the areas where we believe low cost Cu pillar flip chip packages will serve the best. Figure 4. Schematic mobile teardown with common package. But as Figure 4 also shows, there are many other cellular functions which have traditionally been served by alternative packaging platforms for which we see a convergence of requirements for IO, footprint, robustness and price points that indicates an opportunity for low cost flip chip packaging. Connectivity chips (BT, WiFi, NFC, etc.), power chips (PMIC, PA), audio & codec devices are all part of this envelope of functions and applications for which a novel low cost flip chip packaging solution should be a right fit in terms of technical and commercial requirements. So this is the target space we expect to fill with this low cost flip chip solution. Figure 5 provides a visual map representing the specific areas of dominance for concurrent packaging solutions in the space we have identified as target for our flip chip low cost solution. Here, signal count (y axis) is plotted vs body size (x axis). These two are not fully independent variables as pin pitch will correlate them but they should be roughly proportional to each other. In the low count, small body size space, wafer level packaging (WLP) is the dominant solution while at the other end, regular flip chip packaging should be the obvious packaging solution given the routing flexibility attainable with organic laminates. Figure 5. Low cost flip chip and incumbent alternatives In between these points, many other competitive solutions are available: leadframe solutions like QFN or routable MLF, WLP-based solutions like wafer level fan out (panel) and eWLB; and wirebonding solutions like chip array BGA. This begs the question, how flip chip might stand out as the preferred solution B. What bumping solution to use? One of the first questions one gets from any audience interested in low cost packaging applications is how can flip chip be made cost effective when it demands high cost input attributes like bumping, elaborated assembly processing techniques and highly engineered materials. In this section we’ll address the first element on this equation: bumping. Clearly bumping cost is a key input in a total cost of ownership equation for flip chip packages and as such has to be addressed initially to insure a very competitive solution is derived. First off, there are many options available to put bumps on devices: one can print solder using some type of stencil or screen; one can also grow bumps by deposition through electroplating or even by dropping solder balls directly on the bond pads. And there is the question of what solder metallurgy is more adequate to meet the challenges at hand with this particular low cost landscape. Although it might seem reasonable solution to use solder bumps because several processes are available to manufacture them in high volumes, in our estimation, a much more comprehensive solution to enable a low cost flip chip is to use copper pillar bumping. Several factors were considered in making this selection: According to our most current roadmap in figure 2, CuP bumping can be applied over a wider range of bump pitches; added to this, two manufacturing processes are readily developed for CuP: thermocompression bonding and conventional oven reflow. Moreover, there is a wealth of production experience for both processes, extending bonding down to very fine pitches with high yields which obviously are important consideration for manufacturability. Finally, long term reliability, electro migration, current carrying capacity and other quality measures all point to an enhanced packaging solution when using Cu pillars. Figure 6 shows a schematic process flow for CuP bumping tailored for low cost flip chip market. Among the operations considered not essential for low cost flip chip are organic re-passivation, probing and AOI. The underlying assumption enabling these process simplifications is that the devices exhibit really high yields are using non-low K technologies (i.e., silicon should be from legacy nodes, i.e., 65nm and older). Wafer incoming Table I. Examples of Cu pillar flip chip devices in HVM Device name PKG Size (mm) Ball count Ball pitch (mm) Die size, thick Bump Bump Pitch (um) Bump height (um) Substrate layers Device 1 - SIP Device 2 - MCM fc Device 3 - fcCSP 5.25X5.3mm 36 0.5mm 1.17x1.7 0.85x1.0(2 dice) CuPillar 300um 80um 4L 5.25X5.3mm 36 0.5mm 2.06x0.99 1.9x1.35(2 dice) Cupillar 180um 70um 2L 5X5MM 36 0.4mm 2.13x2.5mm Cupillar 170um 75um 2L Structure Sputter metal seed Template Photo (Coat/Align/PEB/Dev) Cu Plating LF(Eu) Solder plating C. Assembly process solutions The final step in enabling a low cost flip chip package is in selecting an assembly process flow that would reduce or eliminate cost contributors while insuring quality and yield metrics are maintained at the level required by the market and specific application. Figure 7 presents our proposed flow for such a process. Template strip Die Prep (BG, Saw) Etch Flux coat & Reflow Flip Chip attach + reflow & Flux clean Figure 6. Process flows for CuP bumps CuP bumping demand has grown at a very fast rate during recent times; so much so that sufficient scale exists nowadays across the industry which has led to a leveling if not decreasing of bumping cost. The obvious benefits of this situation is that existing plating solutions, equipment sets and production flows can be leveraged without requiring specialized changes to accommodate this novel packaging solution. In closing, we believe Cu pillar bumps to be the ideal interconnection solution for low cost flip chip packaging. To enable the best benefits of this solution, we suggest strong codesign activities during the bump array layout, such that it enables a minimal need for routing; i.e., we decidedly have to stay away from redistribution and re-passivation bumping alternatives to enable the lowest cost solution possible. Using that approach, Amkor has been able to use CuP for several devices spanning from logic to analog to mixed signal, starting from very coarse pitches (>200 µm) all the way down to 100 µm with very minimum changes to the standard process flow used for solder bumps. Table 1 shows some selected examples. Molding and cure Solder ball attach PKG Sawing EOL FVI / FVI QA To Test Figure 6. Process flows for Flip Chip assembly First step in the process is to prepare the wafers for assembly. This includes thinning to target thickness and dicing the wafers into individual dice. Much production experience in this area guarantees a high yielding processes where minimal modification from existing best practices is required. Next, the die will be picked and placed on the substrates and send into an oven to complete the soldering process. This is the process where the copper pillar bumps will form the interconnection with the substrate and therefore is an area where critical items such as how high the bumps need to be, the flux to be used and the specific conditions of the reflow recipe are developed to insure a problem free bonding process and good interconnection yields. Figure 7 shows x-ray images depicting typical CuP joints formed with this process. Figure 7. Typical CuP mass reflow x-section. After completing chip attach, the next challenge is the encapsulation of the packages. Underfill provides protection to the joints against the stress caused by the thermal expansion differences between the different materials used in the package construction. In order for underfill to accomplish this goal, it must be free of voids, cracks or imperfections which could result in stress concentration. And, since we are driving a low cost packaging solution, it is peremptory that the material chosen, along with the process, add as lower a contribution to cost as possible. Thus traditional liquid underfill is not a viable solution due to slow process throughput. Instead molded underfill is proposed, where encapsulation of the chip gap and bumps occurs at the same time and process step that the full molding of the package takes place. Table 2 shows typical properties for selected materials used as encapsulants for low cost flip chip packages. Table II. Low cost molding compounds A B C um 20 20 20 Filler content wt% 87.5 88.5 86 Spiral Flow (mold typeA) in/cm 200 190 150 sec 60 63 82 CTE-1 ppm/C 9 10.0 11 CTE-2 ppm/C 36 37.0 42 Gel Time (175C) Tg C 160 143 159.0 Flex. Strength(@25C) N/mm2 170 200 Flex. Strength(@240C) N/mm2 22 23 Flex. Modulus(@25C) Dielectric Constant(@1MHz) Mold shrinkage x102N/mm2 250 270 136 8 210.0 - 3.950 0.17 III. CONCLUSION In this paper we discussed the relevance, application and market dynamics associated with enabling a low cost copper pillar flip chip packages. It was shown that a market gap is appearing for intermediate pin count packages which is currently is not been fully or optimally covered by existing package platforms. In response to this challenge, Amkor has proposed an alternative flip chip package solution leveraging low cost copper pillar bumping, low cost substrates and mature assembly processes which enables said devices to enjoy the mechanical and fan-out robustness of organic laminated flip chip packaging while taking advantage of the benefits provided by a Copper interconnection in terms of current carrying capacity and extended field life. In particular, process flows highlighting the differences between standard operation flows to those proposed for low cost packaging alternatives were proposed. Examples of packages built using optimized copper pillar bumping methodologies and low cost assembly solutions were presented and key differences with standard packaging flows and materials discussed. ACKNOWLEDGMENT The author wishes to acknowledge the factory and research teams in the global Amkor network for their support with data collection, invaluable discussions and financial support for this investigation. REFERENCES Unit Filler size (cut size) low thermal expansion. Each application is different and careful consideration to application specs is required in selection the most appropriate material. Other process in flow process are common with existing packages flows so no special considerations are required in handling these steps. 4 0.21 3.964 0.3 Molding compound formulations are constantly being upgraded and refined to address specific requirements as for example high moisture resistance, low dielectric constant or [1] YANGGYOO JUNG ; MINJAE LEE ; SUNWOO PARK ; DONGSU RYU “DEVELOPMENT OF LARGE DIE FINE PITCH FLIP CHIP BGA USING TCNCP TECHNOLOGY,” ELECTRONIC COMPONENTS AND TECHNOLOGY CONFERENCE (ECTC), 2012 IEEE 62ND, MAY 29, 2012, PP. 439 - 443. [2] Myung_June Lee, Copper Pillar Packaging Development, IPC APEX EXPO, Mar 23-27, 2014, Las Vegas Gerber, M. ; Beddingfield, C. ; O'Connor, S. ; Min Yoo ; MinJae Lee; DaeByoung Kang ; SungSu Park ; Zwenger, C. ; Darveaux, R. ; Lanzone, R.; “Next generation fine pitch Cu Pillar technology Enabling next generation silicon nodes”, Electronic Components and Technology Conference (ECTC), 2011 IEEE 61st , 612-618 [3]