Design of Efficient Binary Comparators in Quantum

advertisement

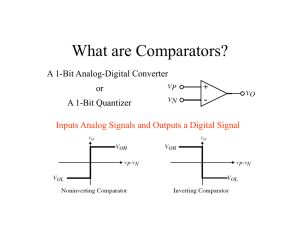

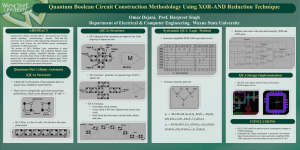

Design of Efficient Binary Comparators in QuantumDot Cellular Automata Abstract: Quantum-dot cellular automata (QCA) are an attractive emerging technology suitable for the development of ultra dense low-power high-performance digital circuits. Efficient solutions have recently been proposed for several arithmetic circuits, such as adders, multipliers, and comparators. Nevertheless, since the design of digital circuits in QCA still poses several challenges, novel implementation strategies and methodologies are highly desirable. This paper proposes a new design approach oriented to the implementation of binary comparators in QCA. New formulations of basic logic equations required to perform the comparison function are proposed. The new strategy has been exploited in the design of two different comparator architectures and for several operands word lengths. With respect to existing counterparts, the comparators proposed here exhibit significantly higher speed and reduced overall area. Existing Method: Binary comparator circuits are building blocks of many digital circuits. This Circuit includes designing of a comparison algorithm for binary numbers which is implemented by normal Logic gates which will consume more amount of area with respect to it’s size. One bit comparison of binary algorithm gives tremendous change in it’s area results To overcome, this results a new architecture which is basic of Nano technology structure is designed in the proposed method. Further Details Contact: A Vinay 9030333433, 08772261612 Email: takeoffstudentprojects@gmail.com | www.takeoffprojects.com Proposed Method: This paper focuses on the design of efficient parallel QCA based n-bit full comparators. The main contribution of this paper is the introduction of a novel design methodology that allows low computational time and very compact layouts to be achieved. In particular, original theorems and corollaries are stated and demonstrated that directly impact on the QCA realizations of some basic Boolean functions used within the comparator architectures. The novel theorems were applied to achieve innovative QCA based structures of n-bit full comparators that were laid out and simulated. Applications: 1) Digital arithmetic applications like in the designing of adders, other logical circuits. Advantages: Simple fixed design architectures and having less area complexities easy flow of Process from input to the output circuit. System Configuration:In the hardware part a normal computer where Xilinx ISE 14.3 software can be easily operated is required, i.e., with a minimum system configuration HARDWARE REQUIREMENT Further Details Contact: A Vinay 9030333433, 08772261612 Email: takeoffstudentprojects@gmail.com | www.takeoffprojects.com Processor Pentium –III - Speed - 1.1 GHz RAM - 1 GB (min) Hard Disk - 40 GB Floppy Drive - 1.44 MB Key Board - Standard Windows Keyboard Mouse - Two or Three Button Mouse Monitor - SVGA SOFTWARE REQUIREMENTS Operating System :Windows95/98/2000/XP/Windows7 Front End : Modelsim 6.3 for Debugging and Xilinx 14.3 for Synthesis and Hard Ware Implementation This software’s where Verilog source code can be used for design implementation. Further Details Contact: A Vinay 9030333433, 08772261612 Email: takeoffstudentprojects@gmail.com | www.takeoffprojects.com