PSoC Square Wave Generator Lab - ECE 381

advertisement

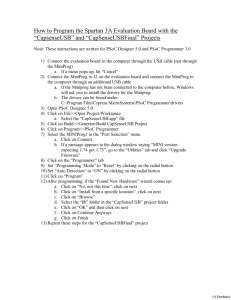

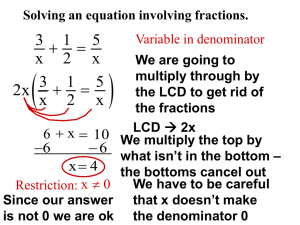

ECE 381 Lab 4 – Square Wave Generator Square Wave Generator Objective Learn about PSoC User Modules, clock sources, and system configuration registers. Description Configure the PSoC to produce a square wave whose frequency is adjusted using an optical encoder. Two momentary push-button switches are used. One, when pressed, halts the output of the square wave by disabling the counter module that produces the output. The other, when pressed, toggles between two frequency ranges. Configuration Use the same optical encoder configuration as in the previous lab. An easy way to do this is to create a new PSoC project and use Clone Project at the top of the Select Project Type –Chip level window. Place the LCD module, which will be used to display information to the user. Connect momentary pushbutton switches to Port1[4] and Port1[5] as shown in the figure at the right. In the Global Resources window, set VC3 Source to SysClk/1 and VC3 Divider to 4. Place a 16-bit Counter module and configure the following Parameters o Name: Counter16 o Clock: VC3 o Enable: Route to Port1[5] o CompareOut: Route to Port1[0]. o TerminalCountOut: None o Period: To be determined by you o CompareValue: To be determined by you o CompareType: Less Than o InterruptType: Terminal Count (Note: Parameters must not be left blank, even if unused) o ClockSync: Sync to SysClock o InvertEnable: Invert Calculate and initialize the Period and CompareValue Parameters of the Counter16 so that it produces an output of 1kHz square wave at 50% duty cycle on startup or after reset. Part I Software SW2 is not used in the part. SW1 controls the Enable input of the Counter16 User Module. When the switch is pressed, the user module halts operation directly in hardware and requires no software intervention. ECE 381 Lab 4 – Square Wave Generator The optical encoder ISR should adjust both the Period and CompareValue of Counter16 so that the output frequency ranges from 100Hz to 10kHz, always with a 50% duty cycle. For this application to be practical, one “tick” of the optical encoder should change the Period and CompareValue by more than 1 integer value. Consider a logarithmic scale. You do not need to hit every frequency in the range and the range should be reachable in a reasonable number of turns. Reasonable will be determined by the professor and/or the lab TA. The LCD should display the frequency of the signal sent to Port1[0] in units of Hz. You will need to do floating point calculations for this to work. Be sure to ask the instructor about string manipulation in class. Floating point math routines are available. See the C Language Compiler User Guide Remember: Do not update the LCD inside of an interrupt service routine! Keep the optical encoder ISR small. It is bad programming practice for an ISR to do more than is necessary to service the interrupt (e.g. updating the value on the LCD). Instead consider using a variable that will let the main loop know that something has changed. For instance, if the main loop sees that the Period value has changed, it can update the information on the LCD, however, it should not update the LCD unless it has actually changed. Test your design to make sure it meets all of the above requirements. Part II In this part, SW2 will be used to toggle the output between two different ranges: 100Hz to 10kHz and 10Hz to 1kHz. Since there is only one GPIO interrupt that is shared by all of the GPIO pins, we will use a DigBuf User Module to provide a unique interrupt for SW2. Place a DigBuf User Module and configure it with the following Parameters: o Name: SW2Buf o Default Load Status: Enable o Input1: Route SW2 (Port1[5]) to this input o Input2: Disable o Input2 ClockSync: Sync to SysClock o Output1: Disable o Output2: Disable o InvertInput1: Normal Implement an ISR for the DigBuf User Module that, when called, toggles the VC3 Divider between two different Divider values so that the output frequency ranges from either 10Hz to 1kHz or 100Hz to 10kHz. To do this, you will need to modify the register named OSC_CR3 which is described in the Technical Reference Manual on page 287. You will also need to modify the LCD display routine to reflect the frequency change and the current mode of operation. Test your design to make sure it meets all of these additional requirements. ECE 381 Lab 4 – Square Wave Generator Part III The system clock (SySClk) is generated internally by the PSoC. It is not a precise oscillator and has a tolerance around its nominal frequency of 24MHz. This means that the actual output frequency of your square wave also shares this tolerance. You will measure the actual frequency of your specific PSoC’s system clock. To do this, you can use register OSC_GO_EN which is described in the Technical Reference Manual on page 285. Modifying this register will allow you to place the SysClk signal on GOE[2]. From there you can connect either Port0[2] or Port2[2]. However, since the LCD is connected to Port2[2] on the evaluation board, it is unavailable for this purpose. Measure your PSoC’s actual SysClk frequency as accurately as you can and calculate the percentage it deviates from the 24MHz nominal frequency. Look in the datasheet for your PSoC part number: DataSheet_CY8C29x66_I.pdf and find the minimum and maximum values of the System Clock; it is listed as Internal main oscillator (IMO). Compare your measured frequency with this range. This model of PSoC is capable of operating at voltages from 3.00V to 5.25V. Suppose you had a design that required the PSoC to operate at 3.3V. Look at the datasheet and determine the maximum CPU Frequency (CPU_Clock) that can be used at this voltage.