Interfaces of 80386DX - Michael J. Geiger, Ph.D.

advertisement

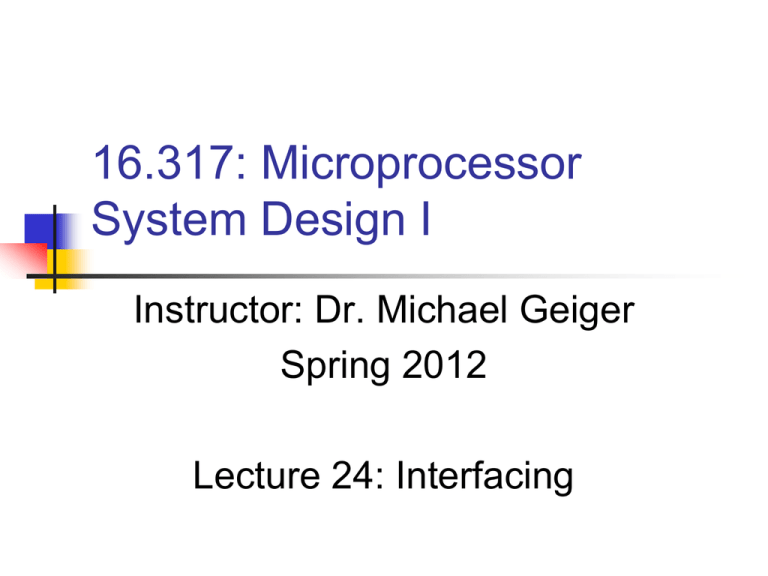

16.317: Microprocessor System Design I Instructor: Dr. Michael Geiger Spring 2012 Lecture 24: Interfacing Lecture outline Announcements/reminders Lab 2 due today Exam 2: 1 week from today Lecture outline 4/13/2015 Once again, allowed 1 8.5” x 11” sheet of notes I’ll provide you with a list of instructions—will post to the web page shortly Review: virtual memory Microprocessor interfaces 80386 interfaces Microprocessors I: Lecture 24 2 Microprocessor interfacing How do microprocessors communicate with the outside world? In other words: What information/signals should a processor take as input? What information/signals should a processor send as output? 4/13/2015 Power/ground Clock Data Interrupt lines Handshaking inputs (i.e., peripheral done with transaction) Bus control inputs Data Address Handshaking outputs (i.e., address valid—proceed with transaction) Read/write control Bus control outputs Microprocessors I: Lecture 24 3 80386 Interfaces (Fig 9.3, p. 376) A2-A31 DMA interface HOLD HLDA BE0-BE3 D0-D31 INTR Interrupt interface NMI W/R RESET D/C M/IO ADS PEREQ Coprocessor interface Memory/ IO interface READY BUSY NA ERROR LOCK BS16 4/13/2015 Microprocessors I: Lecture 24 4 Memory/IO interface 80386 DX has separate address and data buses Difference between real-mode and protected mode - size of address bus Real-mode: 18 address lines (A2-A19) Protected-mode : 30 address lines (A2-A31) What’s “missing”? A0 and A1 are decoded inside 80386DX with information of data transfer size, to produce byteenable outputs (BE0- BE3) BE outputs enable byte, word, double word xfer 4/13/2015 Older processors have multiplexed bus (shared) BE0 lowest byte (D0-D7), BE3 D24-D31 Microprocessors I: Lecture 24 5 Example Show the byte enable line values if 4/13/2015 Accessing a single byte at address 00000H Accessing a single byte at address 17803H Accessing a word starting at 10002H Accessing a word starting at 21029H Accessing a double-word starting at 16314H Microprocessors I: Lecture 24 6 Example solution Show the byte enable line values if Accessing a single byte at address 00000H Accessing a single byte at address 17803H Lowest 2 address bits = 11 start with byte 3 BE3 = 0, all others = 1 Accessing a word starting at 10002H 4/13/2015 Lowest 2 address bits = 00 start with byte 0 BE0 = 0, all others = 1 Lowest 2 address bits = 10 start with byte 2 BE2 = BE3 = 0, others = 1 Microprocessors I: Lecture 24 7 Example solution (cont.) Show the byte enable line values if Accessing a word starting at 21029H Accessing a double-word starting at 16314H 4/13/2015 Lowest 2 address bits = 01 start with byte 1 BE1 = BE2 = 0, others = 1 Lowest 4 address bits = 00 start with byte 0 All BE signals = 0 Microprocessors I: Lecture 24 8 Memory/IO cycle definition and control signals Used to signal: Cycle definition signals: (Figure 9.7) W/R: write/read indication D/C: data/control indication M/IO: memory/input-output indication Cycle control signals 4/13/2015 When a valid address is on the address bus Direction of data transfer When valid write data are on data bus When an external device can put read data on data bus ADS: signals are stable READY: insert wait states NA: next address request Microprocessors I: Lecture 24 9 Bus cycle definitions M/IO D/C W/R Cycle type 0 0 0 Interrupt acknowledge 0 0 1 Idle 0 1 0 I/O data read 0 1 1 I/O data write 1 0 0 Memory code read 1 0 1 Halt/shutdown 1 1 0 Memory data read 1 1 1 Memory data write 4/13/2015 Microprocessors I: Lecture 24 10 Next time 4/13/2015 Finish interfaces 80386 system clock Bus cycles Memory organization Microprocessors I: Lecture 24 11