L1.1_Slides - Concordia University

advertisement

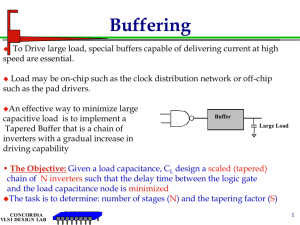

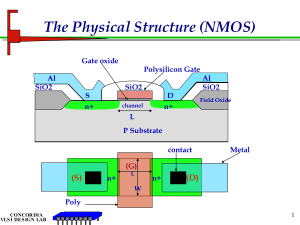

ASIC DESIGN Asim J. Al-Khalili---Concordia University CONCORDIA VLSI DESIGN LAB 1 Objectives •What technologies are there? •Why CMOS? •Where are we? •How far we can go •What is the worldwide view of microelectronics ? •What are the different implementation methods? CONCORDIA VLSI DESIGN LAB 2 The First Transistor CONCORDIA VLSI DESIGN LAB 1948 3 Milestones of IC Development Beginning of Semiconductor Evolution 1948 Passive and Active Components from Semiconductor Materials 1958 Planar Transistors 1959 Planar Passive and Active Devices 1961 Small Scale Integration (SSI)1964 Medium Scale Integration (MSI) 1968 Large Scale Integration(LSI) 1971 Very Large Scale Integration (VLSI) / Ultra Large Scale Integration (ULSI) 1980s System On Chip (SoC) 2000s and is continuing to get larger and larger CONCORDIA VLSI DESIGN LAB 4 WORLD OF SILICON DOGS EAT DOGS IC applications are in every aspects of our lives: Computers Toys Consumer electronics Household items Automotive Industrial equipments Military Communications Advertising and Displays Space and Exploration Etc. CONCORDIA VLSI DESIGN LAB 5 Electronic Circuit Explosion IC Technology Advances MORE CIRCIUTS ON CHIP LOW MANUFACTURING COSTS MORE COMPLEX MANY NEW PRODUCTS ELECRONIC PRODUCTS NEVER BEFORE POSSIBLE NUMBER OF CIRCUITS TO BE DESIGNED CONCORDIA VLSI DESIGN LAB SKY ROCKETED 6 Emerging-in-car systems CONCORDIA VLSI DESIGN LAB 7 The Internet Big Bang CONCORDIA VLSI DESIGN LAB 8 EVEN ATMs CONCORDIA VLSI DESIGN LAB 9 The Incredible Shrinking Transistor 1970’s CONCORDIA VLSI DESIGN LAB 1980’s 2000 2014 10 Reduction in Feature Size Reduce transistor and wiring by Generalized Physical parameter ConstantElectric Field Scaling Factor Generalized Scaling Factor Channel length, Insulator thickness 1/ 1/ 1/d 1/ 1/ 1/w 1 1/ / /d 1/ / /w d Area 1/2 1/2 1/w2 Capacitance 1/ 1/ 1/w Gate delay 1/ 1/ 1/d Power dissipation 1/2 2/2 2/wd Power density 1 2 2w/d Wiring width, channel width Electric field in device Voltage On-current per device Doping CONCORDIA VLSI DESIGN LAB Selective Scaling Factor 11 The First Computer The Babbage Difference Engine (1832) 25,000 parts cost: £17,470 Using finite difference it is possible to replace multiplication, division and subtraction by addition, So in calculating the value of a polynomial we may use addition only . Adding two numbers using gearwheels is easier to implement than doing it by multiplication or division. CONCORDIA VLSI DESIGN LAB 12 Prentice Hall/Rabaey ENIAC - The first electronic computer (1946) 20,000 Vacuum Tubes, it cost $500,000 It could Add, Subtract and store 10-digit decimal numbers in memory It weighted 27 tons, had a size of 80 ft* 8.5 ft* 3 ft, and it required a room of 680 ft2 Consumed 150KW CONCORDIA VLSI DESIGN LAB 13 Prentice Hall/Rabaey BUT NOW, a small cell phone By the millions, more powerful, more functions, less weight, less power consumption, less heat generation Intel 4004 Micro-Processor 1971 4-bit CPU 2,300 transistors Area of 3 by 4 mm Employed a 10 μm silicon-gate 92,000 instructions/s 740 KHz Clock 16 pin CONCORDIA VLSI DESIGN LAB 15 Prentice Hall/Rabaey Intel Pentium (IV) microprocessor 2002 A 'Northwood' core Pentium 4 processor (P4A) Northwood core at 2.2 GHz 2nd cache 512 KB 55 million transistors, 130 nm Technology CONCORDIA VLSI DESIGN LAB 16 Prentice Hall/Rabaey MOORE’S LAW 100 90 80 70 Double Logic Gates Every Two Years ( Moore’s Law ) Maximum Macrocell Size beyond 2005 ( 10 M gates ) Number of Logic Gates (Moore’s Law) Logic Block Area (Moore’s Law) Number of Logic Gates (Max = 10M) Logic Block Area (MAX = 10M) 1M 0.909 1M 0.909 2M 0.923 2M 0.923 4M 1.0 4M 1.0 8M 1.091 8M 1.091 24M 1.32 10M 0.55 64M 1.42 10M 0.22 192M 1.782 10M 0.09 60 50 40 30 20 10 0 1990 2001 2003 2 CONCORDIA VLSI DESIGN LAB 2005 Year 2008 2014 2011 17 Intel announces 14 new Ivy Bridge Processors May. 31, 2012 (8:31 am) By: Matthew Humphries In: Chips, Chips Picks, Geek Pick, News Intel launched the 22nm Ivy Bridge processors that uses quad-core chips Since then it added another 14 processors to the line-up, only this time the chips are mainly dual-core parts catering to a number of different market segments and platforms. . Of the 14 new processors, 6 are classed as desktop chips with power use (TDP) ranging from 35-77 watts. These consist mainly of new quad-core chips, but one dual-core desktop chip is also listed (i5-3470T). CPU frequency ranges from 2.6GHz to 2.9GHz and maxing out at 3.4GHz using Intel Turbo Boost on the Core i7 chip. . IBM Creates New Memory Technology 100 Times Faster Than Flash by Bryan Vore on July 01, 2011 IBM revealed its new phase-change memory (PCM) tech that could drastically change computing and gaming. IBM says that PCM is able to write and retrieve data 100 times faster than Flash memory. It also lasts much longer, surviving 10 million write cycles compared to the 3,000cycles of Flash that the average consumer can use. IBM claims that PCM will herald a "paradigm shift“ when it hits the market in 2016. . IBM Promises Internet 400 times faster A new technology from IBM promises hyper-fast and energy efficient connections to the Internet,as fast as 400 gigabits per second. Scientists in IBM Switzerland just unveiled a prototype tiny chip for an energy efficient analog-to-digital converter (ADC), that’s 5,000 times faster than the average U.S. connection, or 400 times faster than Google Fiber. This is fast enough to download a 2-hour ultra-high-definition movie (about 160 gigabytes) in seconds! The latest version of the chip, developed by IBM with researchers from Ecole Polytechnique Fédérale de Lausanne in Switzerland, is only a prototype right now and was presented at the International Solid-State Circuits Conference (ISSCC) in San Francisco. Latest New iTwin tech torrent onto our hard drives and memory sticks 2011-12 Latest New iTwin tech torrent onto our hard drives and memory sticks 2011-12 Stuck together, the iTwin twins look like a double-ended USB flash memory stick. However, there’s no real storage available in either. Instead, this natty gadget creates a sort of wormhole through the internet, joining together the two computers that the halves of the iTwin are plugged into TOSHIBA SD Memory SD-GU064G2 SD-GU032G2 SD- GU016G2 Capacity 32GB 64GB 16GB Maximum read speed 95MB/ sec Maximum write speed 60MB/ sec Shipped in April 2014, with prices ranging from $120 to $300. Toshiba develops, manufactures 19nm generation NAND Flash Memory with world's largest density and smallest die size 128 Gb capacity in a 3-bit-per-cell chip on a 170mm2 die 23 Feb, 2012 TOKYO—Toshiba Corporation (TOKYO: 6502) today announced breakthroughs in NAND flash that secure major advances in chip density and performance. In the 19 nanometer (nm) generation, Toshiba has developed a 3-bit-per-cell 128 gigabit (Gb) chip with the world's smallest[1] die size—170mm2—and fastest write speed[2]— 18MB/s of any 3-bit-per-cell device. The chip entered mass production earlier this month . What's the largest memory stick that you can buy? It is 256GB. It is a Memory Stick/Flash Drive/USB/Small Little Finger. It is Very Expensive. 128GB$1,499.99 Item# SDCFXP-128G-A91 SanDisk Extreme® Pro™ CompactFlash® 128GB Card with VPG Jun 19, 2012 SANDISK I . . Kingston 1TB USB3.0 DataTraveler HyperX $899 Valid from Aug 05, 2014 Is 14nm the end of the road for silicon chips? • Atoms are very small, but they still have a finite size. The atoms used in silicon chip fabrication are around 0.2nm. A human hair diameter is around 150 micron. A transistor in a 14 nm is around 80 nm. • A process that Intel use with Ivy Bridge — the high-κ dielectric layer is just 0.5nm thick; just two or three atoms! • NOW no manufacturing technique is so accurate, since a single, outof-place atom can ruin an entire chip, it is going to be extremely difficult to manufacture circuits that are both reliable and cost effective. What is in store for us Chipmakers are working hard to reach the 5nm node, but, the industry has several challenges to overcome. Presently, the leading transistor candidates for 5nm are the usual suspects— III-V finFETs; gate-all-around; and nanowires. But the tunnel field-effect transistor (TFET) is also considered for its low power and low voltage, about 0.5 –volt Putting TFETs and finFETs into production is difficult and may need III--‐V materials, nanowires and other complex technologies. System Design Engineering community, Wed, April 30 2014, What foundary support is needed for any chip maker looking to develop 14/16 nm finFET ? a discussion with Steve Carlson, Director, office of Chief Strategy Officer, Cadence Design. http://chipdesignmag.com/sld/blog/2014/04/30/deeper-dive-wed-april-30-2014/ CHALLENGES MOUNT FOR INTERCONNECT> By Mark LaPedus There are a plethora of chip-manufacturing challenges for the 20nm node and beyond. When asked what are the top challenges facing leading-edge chip makers today, Gary Patton, vice president of the Semiconductor Research and Development Center at IBM, said it boils down to two major hurdles: lithography and the interconnect. ROUTING CONGESTION RETURNS By Ed Sperling Routing congestion has returned with a vengeance to SoC design, feuled by the advent of more third-party IP, more memory, a variety of new features, as well as the inability to scale wires at the same rate as transistors. Example of Industrial foundry GLOBALFOUNDRIES provides advanced semiconductor manufacturing excellence with leading-edge (28nm), mainstream (65nm and 45nm) and mature (0.35um to 0.11um) technology, on both 200mm and 300mm wafers. GLOBALFOUNDRIES has fabrication in Dresden, New York and Singapore, with a network of design and support centers in Silicon Valley, China, Japan, Germany, Singapore, Taiwan and the U.K. WWW.GLOBALFOUNDRIES.COM LEVERAGING THE PAST By Ann Steffora Mutschler “It is easy to forget that not every design today is targeted at 20nm, given the amount of focus put on the bleeding edge of technology. But in fact a large number of designs utilize the stability and reliability of older manufacturing nodes, as well as lower mask costs, by incorporating new design and verification techniques, 3D design 3D design opens up architectural possibilities for engineering teams to realize much better performance and far less power consumption. The greatest power savings in 3D designs are achieved at the architectural level, and that may mean jumping in at the deep end. Hot topic: Thermal integrity's effect on 3D-IC design and analysis. editor@chipdesignmag.com> What Comes After FinFETs? By Mark LaPedus The semiconductor industry is currently making a major transition from conventional planar transistors to finFETs starting at 22nm. The question is what’s next? In the lab, IBM, Intel and others have demonstrated the ability to scale finFETs down to 5nm or so. If or when finFETs runs out of steam, there are no less than 18 different next generation candidates that could one day replace today’s CMOS-based finFET transistors. Mayberry said the eventual winners and losers in the next-generation transistor race will be determined by cost, manufacturability and functionality. “The best device is the one you can manufacture,” he said. In fact, the IC industry is already weeding out the candidates. In 2005, the Semiconductor Research Corp. (SRC), a chip R&D consortium , launched the Nanoelectronics Research Initiative (NRI), a group that is researching futuristic devices capable of replacing the CMOS transistor in the 2020 timeframe. NRI member companies include GlobalFoundries, IBM, Intel, Micron and TI. http://extensionmedia.c.topica.com/maapRorab9Upkcc03nbcaeht4A/ posted on April 28, 2013 byStaff Writer Top FPGA Companies For 2013 http://sourcetech411.com/2013 /04/top-fpga-companies-for2013/fpga_market_262x193/ These two companies comprise approximately 90% market share (Xilinx 47%, Altera 41%) in 2012 with combined revenues in excess of $4.5B and a market cap over $20B. posted on April 28, 2013 byStaff Writer Top FPGA Companies For 2013 http://sourcetech411.com/2013 /04/top-fpga-companies-for2013/fpga_market_262x193/ These two companies comprise approximately 90% market share (Xilinx 47%, Altera 41%) in 2012 with combined revenues in excess of $4.5B and a market cap over $20B. How about interconnect and Memory New materials and processes for advanced interconnects Although on chip interconnects have not been scaling at the same speed as other parts of the chip, new capabilities enabled by graphene and CNTs, among other materials, could soon change that. http://marketing.electroiq.com/ct.html?ufl=b&rtr=on&s=x9w5u6,a0tz,5ke,km42,2w dj,fvk2,ca13 3D memory for future nanoelectronic systems 3D memory will generally cost more than 2D memory, so generally a system must demand high speed or small size to mandate 3D. Communications devices and cloud servers need high speed memory. Mobile and portable personalized health monitors need low power memory. In most cases, the optimum solution does not necessarily need more bits, but perhaps faster bits or more reliable bits. http://marketing.electroiq.com/ct.html?ufl=b&rtr=on&s=x9w5u6,a0tz,5ke,8tkl,1r3y,fvk2,ca13 When it comes to memory manufacturing, consolidation is king. Today only three major DRAM manufacturers remain MICRON, SAMSUNG, and SK HYNIX Spectrum Jan 2014 Compound Semiconductors Join the race to sustain Moore’s Law Engineers at Imec and IBM have independently developed processes for making the next decade’s leading chips. The process involves using wafers and certain exotic materials compound semiconductors with ingredients from columns III and V of the old periodic table . The mixing materials holds the key to maintaining the traditional performance improvements associated with Moore’s Law and the shrinking of Transistors. Spectrum IEEE Jan 2014 All optical transistors “The Max Planck Institute of Quantum Optics has taken a step towards devising the long-awaited optical transistor. The technology could pave the way towards long-haul data transmissions using an all-optical network. Researchers from Max Planck have devised a type of optical transistor using a cloud of ultra-cold rubidium atoms.”. http://semiengineering.com/manufacturing-bits-august-5/ State of Semiconductor Revenue Worldwide Semiconductor Revenue Grew 5 Percent in 2013, According to Final Results by Gartner • Intel Retained the No. 1 Position for the 22nd Year in a Row Total worldwide semiconductor revenue reached $315 billion in 2013, up 5 percent from 2012, according to Gartner, Inc. February Semiconductor Sales Up 11.4 Percent Compared to Last Year. More Than One Fourth of Industry Wafer Capacity Dedicated to <40nm Process Geometries. Semiconductor Market Forecast to Contract by 0.1 Percent in 2012 - First Decline in ThreeYears • Graphene The wonder Material https://www.youtube.com/watch?v=eh3dA8xnZ4Y TED on Little Bits http://www.ted.com/talks/ayah_bdeir_building_blocks_that_blink _beep_and_teach Electronic Building Blocks http://www.ted.com/talks/ayah_bdeir_building_blocks_that_blink _beep_and_teach Personal Chip Implant https://ca.finance.yahoo.com/news/microchips-implanted-healthy-people-sooner152916800.html We have seen nothing YET the best days are still ahead Brain Improvement For millions, the brain has not changed, but how we use it is changed. BUT NOW : • Genetically it is possible to alter the brain to create a super brain . • The future comes with new innovation (brain power) • We can upgrade our brain (With implants) • Increase memory (with implants) • Increase sensors (with implants) • Communication between Brain-Brain directly rather than converting chemical – electrical-sounds-pressure waves-mechanical (mouth)-pressure movements (ear) – electrical- chemical, we should be doing it directly • The most important development in the world has been technology start with steam engine, ie replacing human muscle with machine, which is more powerful… So what happens if we increase our brain power, then what we can do !! https://www.youtube.com/watch?v=Z8HeFNJjuj0 Smarter Devices Digital Technology as it gets smarter is eating up our jobs ( example : copier.. translators, Articles written by machines, driverless cars, trucks.. ) Economies do not run on energy, labor , or capital The future is with innovation AIMs What the customers want: High Quality Low Cost Small Size/Weight What the Employer wants Design the: Best Cheapest In shortest time Follow the Spec or better. What you (chip designer) should do: Design a chip with: High speed Small area Low power Testable and reliable Delivered in a short time CONCORDIA VLSI DESIGN LAB 42 Instructor Name: Asim Al-Khalili Office: EV5.126 Tel: 514 848-2424 ext.3119, FAX 848 2802 Email asim@ece.concordia.ca Web http://www.ece.concordia.ca/~asim Time: Mondays-Wednesdays 16:15-17:30 Class Room: MB- 1-301 Office hours: Wednesdays 2:00- 3:30 Course Outline Reference Materials Assignments Lectures Information Web Information Announcements Tools Project Useful Files Important Dates: Midterm Exam: ,Wednesday 15th Oct,2014 Final Exam: Exam: To be announced Project Delivery: Monday 15th Dec. 2014, at 2:00 pm. To be handed to me in my room or the Secretary at front desk. CONCORDIA VLSI DESIGN LAB 43 The following topics will be covered: Week_1 Introduction to ASIC design and review materials. Week_2 MOS transistor characteristics. Week_3 DC analysis of CMOS logic family. Week_4 RC time models, interconnect models. Week_5 Transient analysis, propagation delay models. Week_6 CMOS gates and Static logic families. Week_7 Memory elements. Clocking strategies. Week_8 CMOS process and layout generation. Week_9 Layout techniques. Week_10 I/O drivers and circuit protection. Week_11 Circuit Optimization and secondary effects. Week_12 Dynamic logic families. Week_13 Design for Testability, Packaging, PLD, Synthesis issues. Laboratory: H915. The lab is conducted as an open concept, with no schedule. Information on lab usage will be provided in class. Grading: 5% Assignment Midterm 15% 20% project, 60% Final Exam Text: “CMOS Digital Integrated Circuits, Analysis and Design” (Recommended ) By Sung-Mo Kang and Yusuf Leblebici,3rd Edition, Published by McGraw-Hill “Principles of CMOS VLSI Design” By N. H. Weste & K. Eshraghian 2nd Edition, Published by Addison Wesley “ Application Specific Integrated Circuits”, By M. J. S. Smith,,Addison44Wesley CONCORDIA VLSI DESIGN LAB Device Physics Device Electronics Transistor Circuits Covered in COEN 451 Combinational and sequential Logic Circuits Regular and irregular Subsystems System related issues including reliability, DFT CONCORDIA VLSI DESIGN LAB 45 Course Project The course requires: •design, Design Verification •Layout, Layout Verification, DRC •Post Layout Simulation, •Characterization •IN/OUT placement An example of students projects follows: CONCORDIA VLSI DESIGN LAB 46 Scientific Process or method: Sir Francis Bacon Formulation of a question: Why the apple falls down and not up? Hypothesis: based on knowledge obtained while formulating the question Prediction: This step involves determining the logical consequences of the hypothesis Testing /experimentation: This is an investigation of whether the real world behaves as predicted by the hypothesis. Analysis: This involves determining what the results of the experiment show and deciding on the next actions to take Theory Learning If you're going to learn anything, you need two kinds of prior knowledge: knowledge about the subject at hand, like math, sciences, or programming knowledge about how learning actually works, ie understanding of the cognitive strategies that allow people to learn well. Suggestions to help you learn: Force yourself to recall. In your mind repeat what you have read and see if you can recall what you have just read. Flashcards are useful in this, since they force you to supply answers. Connect the new thing to the old things in your brain. When you do that you are creating new web-lines, in your web of knowledge(Connections between Neurons) that will stick in your brain. Reflect. At the end of your learning session reflect in your mind what you have learned. Henry Roediger and Mark McDaniel, psychologists at Washington University in St. Louis and coauthors of "Make It Stick: The Science Of Successful Learning” Life • When passing a flower, stop and smell it and look at it and appreciate it. Life moves on, so stop and look at the good things around you. • Be Happy with what you can do and ignore the things that you did not succeed to do. • Have a good social life and surround yourself with people that have the same wave length and hobbies so that you can be yourself amongst them . • Keep your hopes alive and keep moving forward by looking forward to what you want to achieve. Keep doing new things and learn new things. • Enjoy the present, consider every breath is a present Tools Cadence unveiled two new tools. The first is a rapid prototyping platform that the company claims will shorten bring-up time by 70%, with 4X improvements in capacity, with IEEE 1801 support for lowpower verification through its emulation platform. The second is a single and multi-corner custom/analog extraction tool, which it claims will improve performance by 5X. The tool has been certified for TSMC’s finFET process. The Future for Feature Size CONCORDIA VLSI DESIGN LAB 51 The Future of Junction Depth Junction Depth (nm) 60 1999 50 2000 2001 40 2002 2003 30 2005 2004 2008 20 2011 10 2014 0 0 CONCORDIA VLSI DESIGN LAB 100 200 300 400 500 Sheet Resistance (/sq) 600 700 800 52 Power density Evolution Watts/cm2 CONCORDIA VLSI DESIGN LAB Feature size (µm) 53 Power Consumption CONCORDIA VLSI DESIGN LAB 54 The Future for Supply Voltage Volts 5 4 3 Gate Over Drive Supply Voltage 2 1 Vth 0 1980 1985 1990 1995 2000 Year CONCORDIA VLSI DESIGN LAB 2005 2010 2015 55 Optical Communications CONCORDIA VLSI DESIGN LAB 56 A day made of Glass http://www.youtube.com/watch?v=X-GXO_urMow&playnext=1&list=PL00407EB774FA759B&fe A Typical CHIP Bus Control Logic Unit Control Logic Register Clock Generation Logic Unit Memory Bonding pads CONCORDIA VLSI DESIGN LAB 58 Design Abstraction Levels SYSTEM MODULE + GATE CIRCUIT DEVICE G S n+ CONCORDIA VLSI DESIGN LAB D n+ 59 Prentice Hall/Rabaey CMOS System Design Top-down Design: Design starts at System Specification and works its way to bottom, ie. circuit level Bottom-up design: Design starts at the basic circuits and works upwards towards system level structure CONCORDIA VLSI DESIGN LAB 60 THE DESIGN FLOW CREATION Register-level Floorplanning Sequential Synthesis RTL DESCRIPTION RTL SYNTHESIS VERIFICATION Simulation RTL NETLIST Logic Optimization, Technology Mapping, Test Generation LOGIC SYNTHESIS Functional Verification, Timing Verification, Simulation GATE-LEVEL NETLIST Physical Floorplanning Placement Signal Routing, Clock Layout, Power & Ground Routing CONCORDIA VLSI DESIGN LAB PHYSICAL SYNTHESIS MASK-LEVEL LAYOUT Parastic Extraction; Power Integrity, Clock Skew, and Noise Analyses; Peliability Analysis 61 Verify at every step ME MO RY CP U Functional Structural Logic Circuit CONCORDIA VLSI DESIGN LAB Device Layout 62 Design Strategies Hierarchy – A repeated process of dividing large modules into smaller sub-modules until the complexity of sub-modules are at an appropriately comprehensible level of detail. – Parallel hierarchy is implemented in all domains. CONCORDIA VLSI DESIGN LAB A Structured Design ÔRegularity Divide the hierarchy in to similar building blocks whenever possible. Some programmability could be added to achieve regularity. l l ÔModularity l Well defined behavioural, structural and physical interface. l Helps: divide tasks into well defined modules, design integration, aids in team design. CONCORDIA VLSI DESIGN LAB ÔLocality IC Design Methodology Requirement specification – most important function which impacts the ultimate success of an IC relates to how firm and clear the device specifications are. – Device specification may be updated throughout the design cycle. – Main items in the specifications are: functional intent: brief description of the device, the technology and the task it performs. Packaging specification CONCORDIA VLSI DESIGN LAB – device port number – package type, dimension, material Functional Description high-level block diagram: all major blocks including intra block connections and connections to pin-outs indicating direction and signal flow. Intra block signal function: description of how blocks interact with each other supported with timing diagram where necessary. · Internal block description of internal operation of each block. Where necessary, the following to be included: timing diagram, state diagram, truth table. CONCORDIA VLSI DESIGN LAB Specifications l I/O specifications · pin-out diagram · I/O functional description · loading · ESD requirements · latch-up protection l D.C. specifications · absolute maximum ratings for: supply voltage, pin voltages · main parameters: VIL and VIH for each input, VOL and VOH for each output, input loading, output drive, leakage current for tri-state operation, quiescent current, power-down current (if applicable) CONCORDIA VLSI DESIGN LAB Specification, continued l AC specifications · inputs: set-up and hold times, rise and fall times · outputs: propagation delays, rise and fall times, relative timing · critical thinking l Environmental requirements · operating temperature, storage temperature, humidity condition (if applicable) CONCORDIA VLSI DESIGN LAB Device Specification ] Functional intent: briefly describe the device, the technology, and the circuits it will replace as well as the task it will perform. ^ Design concept Î Î pin-out diagram: describe the device using a block diagram of the external view of the chip basically, a box with all the I/O pins labelled and numbered I/O description: use a chart to define the I/O signals shown in the pin-out diagram CONCORDIA VLSI DESIGN LAB Example: Pin # Pin Name I/O Type P1 VDD Power Supply P2 TXCLK Input P3 TXP1 Output CONCORDIA VLSI DESIGN LAB Function Power Supply, +5V dc with respect to VSS Transmit Clock, 5.12 MHz rate Transmit output – channel 1, +ve polarity Functional Specification internal block diagram: draw blocks for major functions, show all connections including: connection to all pin-outs, connections between blocks, and direction of signal flow Inter-block signal function: describe how the blocks interact with each other and support this with timing diagrams where necessary · internal block description: describe the internal operation of each block. When necessary, include: timing diagrams, state diagrams, and truth table CONCORDIA VLSI DESIGN LAB Operating characteristics Absolute maximum stress ratings. Example: Parameter Symbol Min. Max. Storage T Ts -65 +150 O O Unit C Operating T TA -40 +85 Supply V VDD -0.5 7 V Input V VI -0.3 VDD + 3 V Supply I IDD 5 mA CONCORDIA VLSI DESIGN LAB C Requirements l Operating power and environmental requirement: · power supply voltage · operating supply current (specify conditions, e.g., power up, power down, frequency, output conditions) · storage temperature · operating temperature · humidity conditions (if applicable) CONCORDIA VLSI DESIGN LAB Input characteristics. Example chart: (V reference is VSS = 0, temperature range is 0oC to 70oC) Pins Symbol Parameter Min nom Max Units TXDAT2 TXDAT2 VIL TXCK TXFRM VIH Input low V Input high V Input C to VSS -0.3 0.4 2.0 2.4 ENB1 ENB2 ICK LFPM CSBL CI IIL IIH RX1N1 RX1N2 VIP CONCORDIA VLSI DESIGN LAB Input low I Input high I Input peak V 0.8 VCC + 0.3 10 +/- 10 +/- 10 VDD + 0.3 V V pF A A V Comments Imputs protected against static damage Vin = 0V Vin = 5.25V AC coupled input A Structured Design ÔRegularity Divide the hierarchy in to similar building blocks whenever possible. Some programmability could be added to achieve regularity. l l ÔModularity l Well defined behavioural, structural and physical interface. Helps: divide tasks into well defined modules, design integration, aids in team design. ÔLocality Internals of the modules are unimportant to any exterior interface. CONCORDIA l VLSI DESIGN LAB Aim of CMOS system Design High Density Fast Switching Time Low Power Dissipation Testable Design Regular and Modular Design CONCORDIA VLSI DESIGN LAB 76 System Performance This is related to several factors including: Algorithm design Design strategy Circuit implementation Floor plan Interconnect strategy Input/Output drives and coupling Clock distribution Interfacing CONCORDIA VLSI DESIGN LAB 77 Standard Devices General purpose use --not optimized to a specific application * Fixed or programmable * Available in various complexities: SSI, MSI, LSI, VLSI, and ULSI * Function: standard logic, MPU, memories, functions DSP, analog * Available in a variety of packages * Technology: bipolar, nMOS, CMOS, BiCMOS, GaAs * Occupy larger areas and consume more power compared to other types of ICs CONCORDIA VLSI DESIGN LAB 78 Full Custom HAND CRAFTED DESIGNG * STRUCTURED DESIGN HIERARCHIAL: TOP DOWN DESIGN, BOTTM UP DESIGN * EXTENSIVE VERIFICATION * MIXED DIGITAL AND ANALOG * TIME CONSUMING AND EXPENSIVE * REQUIRES EXTENSIVE DESIGN EXPERIENCE * COST EFFECTIVE FOR LARGE PRODUCTION VOLUMES CONCORDIA VLSI DESIGN LAB 79 GATE ARRAY CONSISTS OF TRANSISTOR ARRAYS * CUSTOMER DEFINES INTERCONNECTION BETWEEN TRANSISTORS * VENDOR PROVIDES INTERCONNECTION TOPOLOGIES TO FORM LOGIC FUNCTIONS * 1 TO 6 LEVELS OF METALIZATION * AVAILABLE IN DIFFERENT TECHNOLOGIES * 2000 TO 5,000,000 GATE LOGIC COMLEXITIES. * 2 TO 4 WEEKS DESIGN LEAD TIME CONCORDIA VLSI DESIGN LAB 80 STANDARD CELLS *PREDESIGNED AND PRECHARACTERIZED CELLS * AVAILABLE IN VARIOUS CELL COMPLEXITIES: MACROCELLS --VARIABLE HEIGHTS MICROCELLS--STANDARD HEIGHTS * DESIGN PHILOSOPHY SIMILAR TO OFF THE SHELF COMPONENTS * MORE EFFICIENT SILICON UTILIZTION COMPARED * MEDIUM DESIGN TIME * LOWER COST * COST EFFECTIVE FOR LARGE PRODUCTION VOLUMES* CONCORDIA VLSI DESIGN LAB 81 CELL TOPOLOGY STANDARD CELLS ARE AVAILABLE AS FIXED HEIGHT OR VARIABLE HEIGHT. *FIXED HEIGHT CELLS: --MAJORITY OF CELLS ARE IMPLEMENTED USING -- FIXED HEIGHT, BUT VARIABLE WIDTH LAYOUT -- CELLS ARE STACKED IN ROWS * VARIABLE HEIGHT CELLS : --FOR MORE COMPLEX FUNCTIONS SUCH AS MEMORY, ALU, MICROPROCESSOR * COST EFFECTIVE FOR LARGE PRODUCTION VOLUMES CONCORDIA VLSI DESIGN LAB 82 -- Project of ASIC Design -- Instructor: Dr. A.J.AL-Khalili Submitted by Ji, Haiying Zhang, Haiqing Submitted Date: 29 April, 2002 CONCORDIA VLSI DESIGN LAB 83 Overview Logic Design Specification: exhibiting our logic design of every unit: half adder/subtracter, one-bit counter, 4-bit counter. Logic circuit simulation result is presented. The stage mainly worked on the Synopsys development platform within UNIX. Circuit Design Specification: fully covering the most of our work about every CMOS logic circuit unit: NAND and NOR gates, D flip-flop etc. All parameters of circuits are decided. And there are some the circuit plots and waveforms generated by Cadence development tools that test and verify every part of our CMOS circuit design. Layout and Simulation: With Cadence layout tool, we drew the layouts of all circuit units according to the design parameter from the last design stage. Perform DRC. Extract the design and simulate it again and characterize the two gates. To perform DRC on the final design, extract it and simulate it again to obtain the performance measures. The waveforms related the design are shown and analyzed. Packaging: The procedure to place and rout the complete chip including all I/O drivers and PADs is presented. Analyzing and Summary: The test results were analyzed carefully and helped us got appropriate conclusion. Give a complete specification for the circuit. It is summary of our work. It manifests our great gain of designing and developing work experience and important realization from this course. Appendix: this is needful supplement showing our coding work in logic design stage and perfect layout picture drawn with Cadence layout tools. CONCORDIA VLSI DESIGN LAB 84 Logic Design Port clk CLK CLR input output(3:0) 4 –Bit Up/Down Counter udctrl CONCORDIA VLSI DESIGN LAB brwcry Function DFF Driving Clock, 1-0: input output clr “1” clear all port udctrl 1: up counting 0: down counting input 1 or 0 sout 0000--1111 brwcry Borrow or carry signal; for up linking 85 Up/ Do wn c o n t ro llin g-Half adde r an d s u bt rac t e r de s ign Half-Adder and Half-Substracter function: Sout =A’B+B’A Carry=AB Borrow=BA’ The Up/Down Control signal is added to the unit. It just controls which one should be output either the carry or borrow. Borcar=B(UD’A’+UD*A) (UD: up/down control) When UD=1, output carry, the unit works as a half adder. When UD=0, output borrow, it works as a half substracter. CONCORDIA VLSI DESIGN LAB 86 On e -Bit Up/ Do wn c o n t ro llin g Co un t e r de s ign Combining a One-Bit D Flip-Flop, we implement the One-Bit Up/Down controlling Counter. In1 Control S udcontrol In2 Bor/Car D CLR CLK Q Data i Input Bor/Car The ‘Data i’ is the counter output; bor/car can be the input for next level to form the several bits counter. CONCORDIA VLSI DESIGN LAB 87 4 -Bit Up/ Do wn c o n t ro llin g Co un t e r Lo gic Circ uit Plan an d Sim ulat io n Using four One-Bit Up/Down controlling Counters, we implement the 4-Bit Up/Down controlling Counter unit shown as following figure. CONCORDIA VLSI DESIGN LAB 88 We tested and verified the design within Synopsys simulation platform on the Unix (Sun-Solaris). The waveform is shown as Figure 3-6. Figure 3-6 CONCORDIA VLSI DESIGN LAB 89 Circuit Design D flip-flop circuit design CONCORDIA VLSI DESIGN LAB 90 Parameters for positive-edge-triggered D flip-flop. Parameter minimu m ------ Typical Maximum Unit ------ 1670 MHz tPLH propagation delay time, low-to-high output from clear tPHL propagation delay time, high-to-low output from clear tPLH propagation delay time, low-to-high output from clock tPHL propagation delay time, high-to-low output from clock Width of clock or clear pulse, tw ------ ------ ------ Ns 0.1 0.1 0.1 Ns 0.18 0.2 0.22 Ns 0.17 0.2 0.2 Ns 0.3 0.3 ------ Ns Setup time, tsu 0.1 ------ ------ Ns Data hold time, th 0.08 ------ ------ Ns Supply voltage, VDD ------ 3.3 ------ Volt fMAX maximum clock frequency CONCORDIA VLSI DESIGN LAB 91 Timing waveforms of DFF CONCORDIA VLSI DESIGN LAB 92 Half Adder/Subtracter Circuit CONCORDIA VLSI DESIGN LAB 93 Half Adder/Subtracter Circuit waveforms CONCORDIA VLSI DESIGN LAB 94 Half Adder/Subtracter Timing parameters Parameter Typical Unit tPLH propagation delay time, low-to-high sout from data input 0.34 ns tPHL propagation delay time, high-to-low sout from data input 0.38 ns tPLH propagation delay time, low-to-high sout from udctrl 0.24 ns tPHL propagation delay time, high-to-low sout from udctrl 0.26 ns Sout rise-time, tr 0.1 ns Sout fall-time, tf 0.1 ns Borcar fall-time, tr 0.1 ns Borcar fall-time, tf 0.1 ns Supply voltage, VDD 3.3 Volt CONCORDIA VLSI DESIGN LAB 95 4-bit synchronous up/down counter design 4-bit synchronous up down counter implementation CONCORDIA VLSI DESIGN LAB 96 waves feature for the 4-bit synchronous up down counter CONCORDIA VLSI DESIGN LAB 97 Timing parameters for the 4-bit synchronous up down counter Parameter Typical Unit tPLH propagation delay time, low-to-high sout from clock input 0.34 ns tPHL propagation delay time, high-to-low sout from clock input 0.43 ns tPLH propagation delay time, low-to-high sout from udctrl 0.68 ns tPHL propagation delay time, high-to-low sout from udctrl 0.60 ns Sout rise-time, tr 0.38 ns Sout fall-time, tf 0.36 ns Borcar fall-time, tr 0.1 ns Borcar fall-time, tf 0.1 ns Supply voltage, VDD 3.3 Volt CONCORDIA VLSI DESIGN LAB 98 Layout and Simulation NAND Gate Layout CONCORDIA VLSI DESIGN LAB 99 simulation waveforms of NAND gate CONCORDIA VLSI DESIGN LAB 100 Simulation characteristics of the 2-input NAND gate in complementary CMOS. DC characteristics Active area Total area Static current VOH VOL VIH VIL NML NMH 18.76 um2 132.5 um2 0 3.3 volts 0 volt 1.42 volts 0.87 volts 0.87 volts 1.88 volts AC characteristics tPLH min tPHL min tP min tPLH max tPHL max tP max tr min tf min tr max tf max Average power Peak Power 0.15 ns 0.03 ns 0.09 ns 0.18 ns 0.05 ns 0.115 ns 0.15 ns 0.14 ns 0.176 ns 0.15 ns 0.43 mw 0.5 mw CONCORDIA VLSI DESIGN LAB 101 NOR Gate Layout CONCORDIA VLSI DESIGN LAB 102 Waveform of the 2-input NOR gate in complementary CMOS. CONCORDIA VLSI DESIGN LAB 103 Simulation characteristics of the 2-input NOR gate in complementary CMOS DC characteristics Active area Total area Static current VOH VOL VIH VIL NML NMH 24.87 um2 148.32 um2 0 3.3 volts 0 volts 1.57 volts 0.95 volts 0.95 volts 1.73 volts AC characteristics tPLH min tPHL min tP min tPLH max tPHL max tP max tr min tf min tr max tf max Average power Peak Power 0.18 ns 0.05 ns 0.115 ns 0.2 ns 0.07 ns 0.135 ns 0.2 ns 0.15 ns 0.24 ns 0.16 ns 0.45 mw 0.6 mw CONCORDIA VLSI DESIGN LAB 104 Transmission Gate Layout CONCORDIA VLSI DESIGN LAB 105 Inverter Gate Layout CONCORDIA VLSI DESIGN LAB 106 DFF Layout CONCORDIA VLSI DESIGN LAB 107 Half Adder/Substrater Layout CONCORDIA VLSI DESIGN LAB 108 4-bit synchronous up/down counter layout CONCORDIA VLSI DESIGN LAB 109 Simulation waveforms of 4-bit synchronous up/down counter layout CONCORDIA VLSI DESIGN LAB 110 Simulation characteristics of 4-bit synchronous up/down counter layout DC characteristics Active area Total area Static current VOH VOL VIH VIL NML NMH Input leakage current 2685 um2 16000 um2 0 3.3 volts 0 volt 1.5 volts 0.9 volts 0.9 volts 1.8 volts 2 uA Prerequisite for switching function Maximum frequency fma Minimum CLK width Minimum CLR width Set up time tsu uctrl to CLK Set up time tsu CLR to CLK Hold time th uctrl to CLK Hold time th CLR to CLK 280 MHz 3.5 ns 1.6 ns 0.8 ns 0.3 ns 0 ns 0.15 ns Switching characteristics tPLH tPHL 0.7 ns CONCORDIA VLSI DESIGN LAB 0.7 ns tPudctrl to output 0.7 ns tPLH 0.665ns tPHL tPCLK to output 0.72 ns 0.693 ns tPLH -------- tPHL tP CLR to output 0.8 ns 111 0.8 ns Package I/O structure of the 4-bit synchronous up down counter. Ø Input pads In our chip we have three input pads: CLK, CLR, and udctrl. We use the pads of PADINC in hcells library, then make the connection with the correspondent input in the counter circuit using metal1dg layer. Ø Output pads In our chip we have five output pads: output<0>, output<1>, output<2>, output<3>, and brwcry (borrow carry). The first four outputs are the counting results, and the brwcry output pad provides a function of forming cascaded counter using this counter. Notes: -udctrl-- up/down control signal; CLK-- clock signal; CLR-- clear signal -CLR is a high- active signal, so there is no tPLH from CLR to output. CONCORDIA VLSI DESIGN LAB 112 Pad Layout of the 4-bit synchronous up down counter. CONCORDIA VLSI DESIGN LAB 113 Analyzing & Summary From the three development stages, logic design, circuit design and layout simulation, we are able to acquire the conclusion easily. The logic design simulation is the ideal wave that we want to get. The circuit design simulation verifies our logic design correct and in this stage it also help us decide the appropriate parameters. The layout is based on our circuit design parameter. Its simulation result proves to our design work successful. What should be advanced is the fact that there is some discrepancy between the two results from circuit design simulation and layout simulation. As the shown in the Figure 5-5 and Figure 4-10, all the time performance parameters from layout simulation are higher those from circuit design simulation. Actually it is just right result that we have predicted. The layout is closer to real product. However, the circuit design mainly simulates the ideal model; some effect resulting from whole circuit can not be calculated accurately. In short, our work is proved to be significant. Through the project we have learned more system development knowledge and strengthened the ASIC design skills. The achievement from that also manifests our team is successful and cooperative. In addition, we understand the challenge projects in the future work and how to face and solve them. Again, we express our appreciation for our tutor Dr. A.J.AL-Khalili. CONCORDIA VLSI DESIGN LAB 114 Verify at every step ME MO RY CP U Functional Structural Logic Circuit CONCORDIA VLSI DESIGN LAB Device Layout 115