exp7_lecture_wp

advertisement

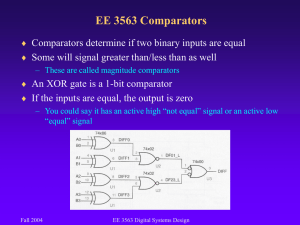

Experiment 7 Design of Binary Arithmetic Circuits Lab Report Comments: Circuit Diagrams: ALWAYS INCLUDE ! – Titled with a descriptive name for the circuit – Brief verbal description of the circuit's function / purpose (what does it do?) – Circuit schematic and/or block diagram • Include all input/output signals – When circuits are implemented in VHDL, signal names on schematics should match signal names used in your VHDL code • • Include all input/output signals sources / destinations on the Development Board (switches, LEDs, etc.) If combining multiple modules, show each module and the interconnections – Not just 1 big “black box” for the whole thing. Modular Design & Design Reuse • Best to “reuse” a previously-designed, tested, verified VHDL module with as little change as possible – …or NONE, if possible! – Changes negate the benefits of having a “proven, working” design • Ex: Rewriting the BCD-7seg in Exp 6 to use only 3-bit inputs (to match Priority Enc output) was not the “best” solution • This week, we will use a more powerful implementation of “Modular Design”…….. VHDL Structural Modeling VHDL Structural Modeling • Reflects modern digital circuit design practice • Supports preferred digital design approach Hierarchical (Top-Down) Design VHDL Structural Modeling Hierarchical (Top-Down) Design Digital Alarm System BCD-7 Seg Decoder 4-bit Digital Comparator Priority Encoder 1-bit Digital Comparator AND_2 (AND gate) Alarm Controller FSM D Flip-Flop NOR_2 (NOR gate) (This is an Example of Multi-level Hierarchical Design. It is NOT necessarily how YOU should complete Exp 9.) VHDL Structural Modeling • Reflects modern digital circuit design practice • Supports preferred digital design approach: Hierarchical (Top-Down) Design • Leverages software design techniques • Supports readability, understandability, and reuse of code • Allows for easy scalability of design • Allows for the use of library-based modules Instructional Objectives: • To use concurrent VHDL statements in the design of arithmetic circuits – Half Adder – Full Adder • Use “Structural Modeling” in VHDL – 4-bit Ripple Carry Adder – Using Half Adder & Full Adder as “Components” – “Top Module” in same “Project” as Half Adder & Full Adder • To design a 4-bit Comparator (need for Alarm System) – Any VHDL Model style (architecture) you like • (Hint: Probably NOT structural!) 1-Bit Binary Addition To Add Two Single-Bit Binary Numbers: A0 A0 B0 Sum S0 Carry COut 0 0 1 1 0 1 0 1 0 1 1 0 0 0 0 1 A0B0 A0B0 B0 1-Bit Binary Adder Half Adder Ai Bi Half Adder COi Si CO0 S0 Multiple-Bit Binary Addition Alternative Approach: Modular Design CO CI3 CI2 CI1 A3 + B3 A2 B2 A1 B1 S3 CO2 S2 CO1 S1 A0 B0 CO0 S0 A3-0 + B3-0 _______________________ CO S3-0 Use same approach as manual computation • Apply the same basic binary addition rules at each bit position • Need to handle “Carry In” for higher bit position additions Modular Approach • Design a 1-bit “Full Adder” for 2 numbers + Carry In • Reuse the design for each upper bit position 1-Bit Binary Full Adder To Add Two 1-Bit Binary Numbers w/Carry In : Input Variables Outputs A B CIn Carry COut Sum 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 ? ? 1 0 1 ? ? 1 1 0 ? ? 1 1 1 ? ? A B CI Ai Bi CIi Full Adder COi Si CO S 4- Bit Ripple-Carry Adder CI3 CI2 A2 B2 A1 B1 A0 B0 S3 CO2S2 CO1 S1 CO0 S0 A3 + B3 A3 B3 A2 CI1 A1 B2 Bi CIi Full Adder COi Si COut Ai Bi CIi COi S3 Ai Si Bi CIi Ai Bi Full Adder Half Adder Si COi Si CO0 S1 S0 COi CO1 S2 B0 CI1 Full Adder CO2 CO3 A0 CI2 CI3 Ai B1 VHDL Structural Modeling Similar to higher level language programming Example circuit Structural VHDL Code A F B A F B A F B 4-Bit Comparator Digital Alarm System 7-Seg Decoder Priority Encoder Connect to ground 4 switches (sensors) I7 I6 I5 I4 I3 I2 I1 I0 B3 B2 B1 B0 Y2 Y1 Y0 AA-AG CATH STROBE Alarm Control Key Comparator Preset Secret Code Code3 Code2 Code1 Code0 Break-in EQ 4 switches (access code) I3 I2 I1 I0 Experiment 7 P3 OFF/ON_L Armed Alarm 4-Bit Comparator Given two 4-bit binary numbers, A and B, determine if they are equal. Multiple solutions: – Subtract B from A and test for zero result – Use VHDL operators • require special libraries – Use XNOR gates to do a bitwise comparison Experiment 7 Overview P1: Design, test, and implement a Half Adder P2: Design, test, and implement a Full Adder P3: Design and implement a 4-bit Ripple Carry Adder Using Structural Modeling - Behavioral Simulation P4: Design and implement a 4-bit Comparator Save for use in Experiment 9 Nexys Development Board Carry out EQUAL A B 4-bit sum Of A+B Design Verification Steps Behavioral Simulation • Is the basic logic correct? Place & Route Post-Route Simulation • Does the design still work with the actual devices used (with prop. delays, etc.)? An important step for “real world” designs!! Testing Strategies We want to create input signal “test vectors” that will: • Verify all important functions of our designs are working properly • Be THOROUGH….. – Cover as many functions / cases as possible • …..AND be EFFICIENT – Use as few test cases (vectors) as possible Testing Strategies Possible Approaches: 1. Test ALL POSSIBLE input combinations (Truth Table) – – Thorough!! Good approach if the number of inputs is small. If not reasonable, then consider: If it ain’t too 2. Targeted Functional Testing bad,…Why not??? – What are the important functions to verify? – What is already proven? (reuse)...what is not? – What could have gone wrong in the design that I should check for? – How can we test each issue as efficiently as possible? Then,… BRAINSTORM Testing the Half & Full Adders A1 A0 B1 B0 CI1 Ai Bi CIi Full Adder COi Ai Bi Half Adder Si COi Si CO0 S1 S0 CO1 How would you suggest testing these two devices? What method / test vectors would you choose? Testing the Ripple-Carry Adder A3 A2 B3 A1 B2 Bi CIi Full Adder COi Si COut Ai Bi CIi COi S3 Ai Si Bi Ai CIi How many input signals? Bi Full Adder Half Adder Si COi Si CO0 COi CO1 S2 B0 CI1 Full Adder CO2 CO3 A0 CI2 CI3 Ai B1 S1 Good Luck!!S0 4 (A) + 4 (B) = 8 How many Test Vectors to test ALL CASES? 28 = 256 Testing the Ripple-Carry Adder A3 A2 B3 A1 B2 Bi CIi Full Adder COi Si COut Ai Bi CIi COi S3 Ai Si Bi CIi Ai Bi Full Adder Half Adder Si COi Si CO0 S1 S0 COi CO1 S2 B0 CI1 Full Adder CO2 CO3 A0 CI2 CI3 Ai B1 If you’ve already proven that the Half Adder & Full Adder designs are OK,… • What other “features” of the RCA do you need to verify? • What “mistakes” could you have made in the structural design that you should check for? Verification Testing of the 4- Bit Comparator A 4 4-bit Digital EQUAL Comparator = 1 : if A = B = 0 : if A \= B B 4 • How might we approach “efficiently” testing this device?