Document

advertisement

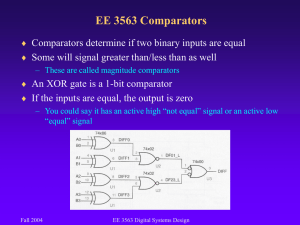

DIGITAL SYSTEMS TCE1111 Design of Arithmetic Circuits – Adders, Subtractors, BCD adders Week 6 and 7 (Lecture 2 of 2) DIGITAL SYSTEMS TCE1111 What we are going to discuss? • Design of Half Adder – Different ways of implementation • Design of Full Adder – using two half adders, using only NAND or using only NOR gates • Design of Half Subtractor • Design of Full Subtractor-using two half subtractors • Construction of 2-bit, 4-bit parallel binary adders, 4-bit parallel binary subtractors, 4 bit parallel binary adder/subtractor circuits • Construction of Carry lookahead adder • BCD addition – Design of 8421 BCD adder circuit 2 DIGITAL SYSTEMS TCE1111 Half-Adder • This circuit needs 2 binary inputs and 2 binary outputs. • The input variables designate the augend and addend bits:the output variables produce the sum and carry. Inputs Carry Sum • X Y C S • 0 0 0 0 • 0 1 0 1 • 1 0 0 1 • 1 1 1 0 3 DIGITAL SYSTEMS TCE1111 TWO DIFFERENT IMPLEMENTATIONS OF HALF ADDER 4 DIGITAL SYSTEMS TCE1111 Implementation of Half Adder using only NAND gates 5 DIGITAL SYSTEMS TCE1111 Implementation of Half Adder using only NOR gates 6 DIGITAL SYSTEMS TCE1111 Full-Adder • • • • Is a combinational circuit that forms the arithmetic sum of 3 bits. Consists of 3 inputs and 2 outputs. When all input bits are 0 , the output is 0. The output S equal to 1 when only one input is equal to 1 or when all 3 inputs are equal to 1. • The C output has a carry of 1 if 2 or 3 inputs are equal to 1. 7 DIGITAL SYSTEMS TCE1111 Full Adder Truth Table x y Z C S 0 0 0 0 0 0 0 1 0 1 X’Y’Z 0 1 0 0 1 X’YZ’ 0 1 1 1 X’YZ 0 1 0 0 0 1 XY’Z’ 1 0 1 1 XY’Z 0 1 1 0 1 XYZ’ 0 1 1 1 1 XYZ 1 XYZ 8 DIGITAL SYSTEMS TCE1111 Simplification of Boolean expressions for Full adder S=XY’Z’ +X’YZ’ + XYZ + X’Y’Z C=XY+XZ+YZ 9 DIGITAL SYSTEMS TCE1111 Implementation of Full Adder using AND-OR Gate Network 10 DIGITAL SYSTEMS TCE1111 Implementation of Full Adder using Two Half Adders (1)… S=XY’Z’ +X’YZ’ + XYZ + X’Y’Z = Z’ (XY’+X’Y) + Z (XY + X’Y’) = Z’ (XY’ + X’Y) + Z (XY’ + X’Y)’ = Z (X Y) C= XY’Z + X’YZ + XYZ’+XYZ = XY’Z + X’YZ + XY(Z’+Z) = XY’Z + X’YZ + XY = Z(XY’ + X’Y) + XY = Z (X Y) + XY 11 DIGITAL SYSTEMS TCE1111 Implementation of Full Adder using Two Half Adders (2) X S Y Z C 12 DIGITAL SYSTEMS TCE1111 Implementation of Full Adder using only NAND gates (1)…Boolean expressions in NAND form 13 DIGITAL SYSTEMS TCE1111 Implementation of Full Adder using only NAND gates (2) - Logic Diagram X Y Z S C 14 DIGITAL SYSTEMS TCE1111 Full Adder Truth Table x y Z C S 0 0 0 0 0 0 1 0 (X+Y+Z’) 1 0 1 0 0 (X+Y’+Z) 1 0 1 1 1 0 (X+Y’+Z’) 1 0 0 0 (X’+Y+Z) 1 1 0 1 1 0 (X’+Y+Z’) 1 1 0 1 0 (X’+Y’+Z) 1 1 1 1 1 (X+Y+Z) 0 (X+Y+Z) 15 DIGITAL SYSTEMS TCE1111 Implementation of Full Adder using only NOR gates (1)…Boolean expressions in NOR form 16 DIGITAL SYSTEMS TCE1111 Implementation of Full Adder using only NOR gates (2)-Logic Diagram 17 DIGITAL SYSTEMS TCE1111 HALF SUBTRACTORS Half subtractor accepts two binary digits as input (Minuend and Subtrahend) and produces two outputs, a Difference bit (Di) and Borrow bit (B0). Difference 00 01 10 11 = = = = 0 1 1 0 Borrow 0 1 0 0 18 DIGITAL SYSTEMS TCE1111 The truth table and the logic symbol for half subtractor A’B AB’ A’B 19 DIGITAL SYSTEMS TCE1111 Boolean expressions for half subtractor The difference (Di) output column of the truth table is an XOR operation. Di = A B The Boolean expression for the borrow (B0) output is 20 DIGITAL SYSTEMS TCE1111 LOGIC DIAGRAM OF HALF SUBTRACTOR 21 DIGITAL SYSTEMS TCE1111 FULL SUBTRACTOR-Truth Table and Logic Symbol The FS accepts three inputs including a borrow input (Bin) and produces a difference output (Di) and a borrow output (B0). 22 DIGITAL SYSTEMS TCE1111 Boolean Expressions for Full Subtractor A’B’Bin A’B’Bin A’BBin’ A’BBin’ A’BBin AB’Bin’ ABBin ABBin 23 DIGITAL SYSTEMS TCE1111 Boolean Expressions for Full Subtractor Di A’B’Bin + A’BBin’ + AB’Bin’ + ABBin = A’(B’Bin + BBin’) + A(B’ Bin’ + BBin) = A’(B Bin) + A(B Bin)’ = A B Bin B0 A’B’Bin + A’BBin’ + A’BBin + ABBin = A’B’Bin + ABBin + A’B(Bin + Bin’) = Bin( A B)’ + A’B 24 DIGITAL SYSTEMS TCE1111 Boolean Expressions for Full Subtractor Difference output of the FS can be given by Di = A B Bin The borrow output of the FS can be derived by the truth table as follows. 25 DIGITAL SYSTEMS TCE1111 LOGIC DIAGRAM FOR FULL SUBTRACTOR Di = A B Bin 26 DIGITAL SYSTEMS TCE1111 FULL SUBTRACTOR USING TWO HALFSUBTRACTORS AB Di = A B Bin 27 DIGITAL SYSTEMS TCE1111 PARALLEL ADDER • Parallel Adder is a digital circuit that produces the arithmetic sum of 2 binary numbers. • Constructed with full adders connected in cascade, with output carry from each full adder connected to the input carry of next full adder in the chain. • The augend bits of A and the addend bits of B are designated by subscript numbers from right to left, with subscript 1 denoting the least significant bit. • The carries are connected in a chain through the full adders. 28 DIGITAL SYSTEMS TCE1111 2- Bit Parallel Adder (1)… • LSB of two binary numbers are represented by A1 and B1. • The next higher bit are A2 and B2. The resulting three sum bits are 1, 2 and CO, in which the CO becomes MSB. • The carry output CO of each adder is connected as the carry input of the next higher order. A2A1 + B2B1 C0 2 1 29 DIGITAL SYSTEMS TCE1111 2-BIT PARALLEL ADDER USING A HALF ADDER AND A FULL ADDER (2)… A2A1 + B2B1 C0 2 1 30 DIGITAL SYSTEMS TCE1111 2-BIT PARALLEL ADDER USING TWO FULL ADDERS (3) A2A1 + B2B1 C0 2 1 31 DIGITAL SYSTEMS TCE1111 Four Bit Parallel Adders (1)… • An n-bit adder requires n full adders with each output connected to the input carry of the next higher-order full adder. • A four bit parallel adder using 3 FA and 1 HA is shown. • Halfadder adds the 1s column A1 and B1. The 2s, 4s and 8s columns being added by three FA. • The carry output of each adder is connected to the carry input of next adder called as internal carries. 32 DIGITAL SYSTEMS TCE1111 Four Bit Parallel Adders (2)An example… Subscript I: 4 3 2 1 Input carry 0 1 1 0 Cin Augend 1 0 1 1 Ai Addend 0 0 1 1 Bi Sum 1 1 1 0 ∑i Output carry 0 0 1 1 C0 Where Ai = 10112 Bi = 00112 33 DIGITAL SYSTEMS TCE1111 Four Bit Parallel Adder (3)… 34 DIGITAL SYSTEMS TCE1111 Logic Symbol Of Four Bit Parallel Adder (4)… The 4 bit parallel adders can be used to form 8 bit, 12 bit, 16 bit and 32 bit parallel adders. 35 DIGITAL SYSTEMS TCE1111 Logic symbol of 8 bit parallel adder (5) 36 DIGITAL SYSTEMS TCE1111 2-BIT PARALLEL SUBTRACTOR Here the least significant bit (LSB) of the two numbers are represented by A1 and B1 and the next higher bit are A2 and B2. The BO of 1s HS is connected to Bin 2s FS. The subtractor produces two difference bits D1 and D2. 37 DIGITAL SYSTEMS TCE1111 Four Bit Parallel Subtractor using Half and Full Subtractors 38 DIGITAL SYSTEMS TCE1111 Four Bit Parallel Subtractor using Full Adders (1)… • Parallel adders can be used to perform binary subtraction because the subtraction is addition in the 2’s complement form of binary number. • The four bit subtractor using four Full Adder is shown. 39 DIGITAL SYSTEMS TCE1111 Four Bit Parallel Subtractor using Full Adders (2)… 40 DIGITAL SYSTEMS TCE1111 Four Bit Parallel Subtractor using Full Adders (3) • The four inverters change the binary subtrahend to its 1’ complement form i.e 1 to 0 and 0 to 1. • The high input at Cin, LSB makes the binary subtrahend to 2s complement form. • Then minuend and 2’s complement form of subtrahend are added. The output line C0 of fourth Full adder is the overflow output which is discarded. 41 DIGITAL SYSTEMS TCE1111 4 bit Parallel Adder / Subtractor Circuit (1)… 42 DIGITAL SYSTEMS TCE1111 4 bit Parallel Adder / Subtractor Circuit (2) • • • • • 4 bit parallel adder / subtractor Circuit can be constructed using Full Adders and XOR gates as shown. The logic circuit has an additional input called the control input, which determines the addition or subtraction. If this control input is logic 0, the all four XOR gates have no effect on the data on the input line B. IF Cin of the first Full Adder is held low, it works as a four bit parallel adder When the control input is at logic 1 the XOR gates work as a inverter and the circuit performs as four bit parallel subtractor 43 DIGITAL SYSTEMS TCE1111 Carry Propagation (1)… • The addition of 2 binary numbers in parallel implies that all the bits of the augend and addend are available for computation at the same. • The signal must propagate through the gates before the correct output sum is available in the output terminals. • The total propagation time is equal to the propagation delay of a typical gates times the number of gate levels in the circuit. 44 DIGITAL SYSTEMS TCE1111 Carry Propagation (2) • The number of gate levels for the carry propagation can be found from the circuit of the full adder. • In the figure for full adder, the input and output variables use the subscript i to denote a typical stage in the adder. • The signals at Pi and Gi settle to their steady state value after they propagate through their respective gates. • These 2 signals are common to all full adders and depend only on the input augend and addend bits. 45 DIGITAL SYSTEMS TCE1111 Full Adder Circuit with P and G (1)… 46 DIGITAL SYSTEMS TCE1111 Full Adder Circuit with P and G (2) • If we define two new binary variables Pi = Ai Bi Gi = Ai Bi Then output sum and carry can be expressed as Si = Pi Ci Ci+1 = Gi +PiCi • Gi is called a carry generate and it produces a carry of 1 when both Ai and Bi are 1, regardless of the input carry Ci • Pi is called a carry propagate because it is the term associated with the propagation of the carry from ci to ci+1. 47 DIGITAL SYSTEMS TCE1111 Carry Lookahead Generator (1)…Boolean Expressions C0= input carry C1=G0+P0C0 C2=G1 +P1C1 = G1+P1(G0+P0C0) = G1+P1G0+P1P0C0 C3=G2+P2C2=G2+P2G1+P2P1G0+P2P1P0C0 C3 does not have to wait for C2 and C1 to propagate , in fact C3 is propagated at the same time as C1 and C2. 48 DIGITAL SYSTEMS TCE1111 Carry Lookahead Generator (2)…-Logic Diagram C3 C2 C1 49 DIGITAL SYSTEMS TCE1111 4 bit adder with carry lookahead (1)… • Each sum output requires 2 exclusive OR gates. • The output of the first exclusive OR gate generate the Pi variable and the AND gate generate the Gi variable. • The carries are propagated through the carry lookahead generator and applied as inputs to the second exclusive OR gate. • All output carries are generated after a delay through two levels of gates. • Thus , output S1 though S3 have equal propagation delay times. 50 DIGITAL SYSTEMS TCE1111 4 bit adder with carry lookahead (2) 51 DIGITAL SYSTEMS TCE1111 BCD ADDITION (1)… • Procedure: – Step 1: Add the two BCD numbers, using the rules for binary addition – Step 2: If a 4-bit sum is equal to or less than 9, it is a valid BCD number. – Step 3: If a 4-bit sum is greater than 9, or if a carry out of the 4-bit group is generated, it is an invalid result. Add 6 (0110) to the 4-bit sum in order to skip the six invalid states and return the code to 8421. If a carry results when 6 is added, simply add the carry to the next 4-bit group. 52 DIGITAL SYSTEMS TCE1111 BCD ADDITION (2)-Example When you add BCD think decimal and answer in Binary 1 1 478 0100 0111 1000 +137 0001 0011 0111 -----------------------------------------------0110 1011 1111 0000 0110 0110 ------------------------------------------------615 0110 0001 0101 53 DIGITAL SYSTEMS TCE1111 Decimal adder for Standard BCD Code (1)… • A decimal adder requires a minimum of nine inputs and five outputs, since four bits are required to code each decimal digit and the circuit must have an input and output carry. • Consider the arithmetic addition of two decimal digits in standard BCD code (8421 code), together with an input carry from a previous stage. 54 DIGITAL SYSTEMS TCE1111 Decimal adder for Standard BCD Code (2)… • Since each input digit does not exceed 9, the output sum cannot be greater than 9+9+1 =19, the 1 in the sum being an input carry. • Apply 2 BCD digits to a 4-bit binary adder. • The adder will form the sum in binary and produce a result that ranges from 0 through 19. • These binary numbers are listed in the table and are labeled by K, Z8,Z4,Z2,Z1 and K is carry. • The columns under the binary sum list the binary value that appears in the outputs of the 4-bit binary adder 55 DIGITAL SYSTEMS TCE1111 Decimal adder for Standard BCD Code (3)…-Truth Table K Z8 Z4 Z2 Z1 C S8 S4 S2 S1 D K Z8 Z4 Z2 Z1 C S8 S4 S2 S1 D 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 0 1 0 0 0 0 10 0 0 0 0 1 0 0 0 0 1 1 0 1 0 1 1 1 0 0 0 1 11 0 0 0 1 0 0 0 0 1 0 2 0 1 1 0 0 1 0 0 1 0 12 0 0 0 1 1 0 0 0 1 1 3 0 1 1 0 1 1 0 0 1 1 13 0 0 1 0 0 0 0 1 0 0 4 0 1 1 1 0 1 0 1 0 0 14 0 0 1 0 1 0 0 1 0 1 5 0 1 1 1 1 1 0 1 0 1 15 0 0 1 1 0 0 0 1 1 0 6 1 0 0 0 0 1 0 1 1 0 16 0 0 1 1 1 0 0 1 1 1 7 1 0 0 0 1 1 0 1 1 1 17 0 1 0 0 0 0 1 0 0 0 8 1 0 0 1 0 1 1 0 0 0 18 0 1 0 0 1 0 1 0 0 1 9 1 0 0 1 1 1 1 0 0 1 19 56 DIGITAL SYSTEMS TCE1111 Decimal adder for Standard BCD Code (4)… -Boolean function for correction • From the table, when the binary sum is equal to or less than 1001, the corresponding BCD number is identical, and therefore no conversion is needed. • When the binary sum is greater than 1001, non valid BCD representation is obtained. • Addition of binary 6 (0110) to the binary sum converts it to the correct BCD representation and also produces an output carry as required 57 DIGITAL SYSTEMS TCE1111 Decimal adder for Standard BCD Code (5)… Boolean function for correction • A correction is needed when the binary sum has an output carry K=1. The other six combinations from 1010 through 1111 that need a correction have a 1 in position Z8. To distinguish them from binary 1000 and 1001, which also have a 1 in position Z8, it can be concluded that Z 4 or Z2 must have a 1. • Therefore, the condition for a correction and an output carry can be expressed by the Boolean function: C=K+Z8 Z 4+Z8 Z2 • When C =1, it is necessary to add 0110 to the binary sum and provide an output carry for the next stage. 58 Decimal adder for Standard BCD Code (6)… Block Diagram of a BCD Adder DIGITAL SYSTEMS TCE1111 59 DIGITAL SYSTEMS TCE1111 Decimal adder for Standard BCD Code (7) • The two decimal digits, together with the input carry, are first added in the top 4-bit adder to produce the binary sum. • When the output carry is equal to zero, nothing is added to the binary sum • When it is equal to 1, binary 0110 is added to the binary sum through the bottom 4-bit adder. • A decimal parallel adder that adds n decimal digits needs n BCD adder stages. • The output carry from one stage must be connected to the input carry of the next higher-order stage. 60