Address

advertisement

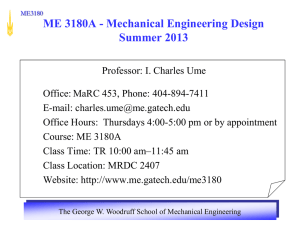

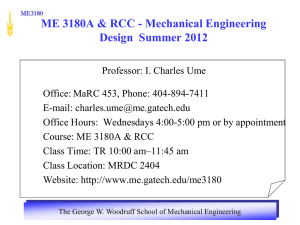

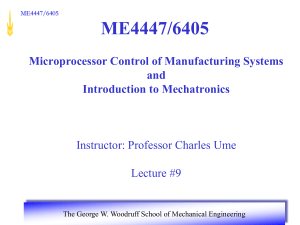

ME4447/6405 ME4447/6405 Microprocessor Control of Manufacturing Systems and Introduction to Mechatronics Instructor: Professor Charles Ume Lecture #9 The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 Reading Assignments Reading assignments for the next 4 weeks: HCS12 Microcontroller: S12CPUV2 Reference Manual CPU12RG/D: Rev. 2, 11/2001 Reference Book: Basic Microprocessors and the 6800, by Ron Bishop . Chapter 5 Chapter 6 Chapter 7 Chapter 8 Microcomputers-What Are They? Programming Concepts Addressing Modes M6800 Software There will be questions and answers the rest of this week and next week based on your reading assignment. The George W. Woodruff School of Mechanical Engineering ME4447/6405 Why use Assembly Language? HCS12 CPU can only understand instructions written in binary called Machine Language. Writing programs in Machine Language is extremely difficult Mnemonics are simple codes, usually alphabetic, that are representatives of instructions they represent (example: LDAA [LoaD Accumulator A]) A program written using Mnemonic Instructions is called Assembly Language program An Assembler can be used to translate Assembly Language program to Machine Language Program, and put it in S-Record Format. The George W. Woodruff School of Mechanical Engineering ME4447/6405 Assembly Language Notations Address: Common term for memory location. Always written in hexadecimal. $4000 is the 4000th16 Memory Location (Note: “$” signifies hexadecimal) LDAB $4000 Literal Value: A number used as data in program is indicated by “#”. Can be represented in the following ways: #$FF = hexadecimal number FF #%1011 = binary number 1011 (Note: “%” signifies binary) #123 = decimal number 123 LDAB #$FF; LDAB #$D01A A Literal Value can be stored in an address Example: Store Literal Value #$FF in address $4000 LDAB #$FF STAB $4000 Example 2: Store Literal Value #$FE0A in address $2000 LDD #$FE0A STD $2000 Note: #$FE is stored in address $2000 and #$0A is stored in address $2001 The George W. Woodruff School of Mechanical Engineering ME4447/6405 Assembly Language Directives Directives: Instructions from the programmer to Assembler NOT to microcontroller (Page 134 in Ron Bishop) Example 1: ORG <address> Store translated/assembled machine language instructions in sequence starting at given address for any mnemonic instructions that follow ORG $1000 Example 2: END Stop translating/assembling mnemonics instructions until another ORG is encountered (Note: More will be covered in later lectures) The George W. Woodruff School of Mechanical Engineering ME4447/6405 Left margin of assembly program Assembly Language Format A Tab (8 white spaces) or Label (Note: A Label is another Assembly Directive and will be covered in later lectures) Assembly Directive Or Mnemonic Instruction (Note: Last three options are called Operands) Data that the Assembly Directive uses Or Blank if Mnemonic Instruction does not need Data Or Offset Address used to modify Program Counter by a Mnemonic Instruction Or Data that Mnemonic Instruction uses Or Address where the Data that Mnemonic Instruction will use is stored The George W. Woodruff School of Mechanical Engineering ME4447/6405 Front ORG LDAA DECA BNE LDAB STAB INCX SWI END $0800 #$100A Front $2F,Y $110C - - 86 43 27 3F 100A 0E - The George W. Woodruff School of Mechanical Engineering ME4447/6405 Addressing Modes In the previous slide, there were several options for the operand: • Blank if Mnemonic Instruction does not need Data • Offset Address used to modify Program Counter by a Mnemonic Instruction • Data that Mnemonic instruction uses • Address were Data that Mnemonic instruction uses is stored Which option a programmer uses is defined by the following addressing modes: (See next slide also) •Inherent •Immediate •Extended •Indexed Indirect •Direct •Indexed •Relative (Note: All instructions are not capable of all addressing modes. Example: BLE [Branch if Less than or Equal to Zero] is only capable of Relative addressing mode) The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 Example: Programming Reference Guide Page 6 The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 Blank if Mnemonic Instruction does not need Data If Mnemonic Instruction does not need data then it uses Inherent Addressing Mode Example: Write a program to clear accumulator A. Start programming at address $1000 Solution: ORG $1000 CLRA SWI END CLRA [ CLeaR accumulator A] is an instruction using Inherent Addressing (NOTE: SWI [SoftWare Interrupt] is a mnemonic instruction which tells the 9SC32 to store the content of cpu registers on the stack. Sets the I bit (the interrupt bit) on the CCR. Loads the program counter with the address stored in the SWI interrupt vector, and resumes program execution at this location. If no address is stored in the SWI vector, the main program will stop execution at The George Woodruff School of Mechanical this point. Used in this W. course to return control to Mon12Engineering Program) ME4447/6405 Data that Mnemonic instruction uses The Mnemonic instruction is using Immediate Addressing mode if the operand is Data used by the instruction Example: Write a program to load accumulator A with #$12. Start programming at address $1000 Solution: ORG $1000 LDAA #$12 SWI END LDAA #$5BEE (Explain what happens) LDAA is an instruction using Immediate Addressing mode in this example The George W. Woodruff School of Mechanical Engineering ME4447/6405 Address were Data that Mnemonic instruction uses is stored The following addressing modes apply if the operand is an Address containing Data used by Mnemonic instruction : Direct •Data is contained in Memory locations $00 to $FF •Address is given as a single byte address between $00 to $FF •Instructions using Direct addressing has fastest access to memory Example: LDAA $00 Loads accumulator A with Data value stored at memory location $00 Extended •Data is contained in Memory locations $0100 to $FFFF •Address is given as a two byte address between $0100 to $FFFF Example: LDAA $2000 Loads accumulator A with Data value stored at memory location $2000 The George W. Woodruff School of Mechanical Engineering ME4447/6405 Example Problem 1 Example : Write a program to add the numbers 1010 and 1110. Solution ORG LDAA LDAB ABA STAA SWI END $1000 #$0A #$0B $00 *Puts number $0A in acc. A *Puts number $0B in acc. B *Adds acc. B to acc. A *Stores results in address $00 *Software interrupt LDAB and LDAA use immediate addressing mode STAA uses direct addressing mode The George W. Woodruff School of Mechanical Engineering ME4447/6405 Address were Data that Mnemonic instruction uses is stored (Continued) Indexed: • Data is located within Memory locations $00 to $FFFF Example: Store content of $2003 in Register A LDX #$2000 LDAA $03,X Loads accumulator A with Data value stored at memory location $2003 X + $03 = $2000 + $03 = $2003 (Note: LDX [ LoaD index register X]) The George W. Woodruff School of Mechanical Engineering ME4447/6405 Why is Indexed Addressing Mode needed? Example: Store Data Value #$20 into memory locations $2000 to $3000 Without Indexed Addressing Mode ORG $1000 LDAA #$20 STAA $2000 STAA $2001 . . . STAA $3000 SWI END With Indexed Addressing Mode LOOP ORG $1000 LDAA #$20 LDX #$2000 STAA $00,X INX CPX #$3001 BNE LOOP SWI END Program on the Left is much longer than the program on Right The George W. Woodruff School of Mechanical Engineering ME4447/6405 LOOP Why is Indexed Addressing Mode needed? (Continued) ORG $1000 LDAA #$20 LDX #$2000 STAA $00,X INX CPX #$3001 BNE LOOP SWI END Note: LDAA[LoaD accumulator A] LDX [ LoaD Index Register X] STAA [ STore Accumulator A] INX [ INcrement X] CPX [ ComPare X] BNE [Branch if Not Equal] ( is using relative addressing in conjunction with label “LOOP”) LOOP, BNE LOOP, INX, and CPX #$3001 creates a loop. Loop1: Data in accumulator A (#$20) is stored at $2000 + $00 Data in X is incremented #$2000 + #$0001 = #$2001 Data in X is compared to #$3001 Not equal so do another loop Loop2: Data in Accumulator A (#$20) is stored at $2001 Data in X is incremented #$2001 + #$0001 = #$2002 Data in X is compared to #$3001 Not equal so do another loop The George W. Woodruff School of Mechanical Engineering Etc….. ME4447/6405 Why is Indexed Addressing Mode needed? Example: Store Data Value #$20 into memory locations $2000 to $3000 ORG $1000 LDY #$1001 LDAA #$20 LDX #$2000 LOOP STAA $00,X INX DECY BNE LOOP SWI END The George W. Woodruff School of Mechanical Engineering ME4447/6405 Homework Homework 1 • Write an assembly language program to clear the internal RAM in the MC9S12C32. • Write a program to add even/odd numbers located in addresses $0800 through $0900. Homework 2 • Write a program to find the largest signed number in a list of numbers stored in address $0A00 through $0BFF. Repeat for an unsigned number. The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 Types of Indexed modes of Addressing Auto Pre-/Post-Increment/Decrement: Base index register (X, Y and SP) may be automatically incremented/decremented before or after instruction Program Counter may not be used as base register No offset is available May be incremented/decremented 1 to 8 times Post-Increment (in ranges from 1 through 8): LDX 2,SP+ EE B1 *Index register X is loaded with contents of memory location in stack pointer (same as PULX). Then stack pointer is incremented twice. The George W. Woodruff School of Mechanical Engineering ME4447/6405 Types of Indexed modes of Addressing Pre-Increment (in ranges from 1 through 8): LDX 2,+SP EE A1 *Stack pointer is incremented twice. Then Index register X is loaded with contents of memory location in stack pointer Pre-Decrement (in ranges from -8 through -1): STAA 1,-X 6A 2F *Index register X is decremented. Then content of Accumulator A is stored in memory location in Index Register X The George W. Woodruff School of Mechanical Engineering Types of Indexed modes of Addressing ME4447/6405 Learning Objectives: Learn how to use following in index mode of addressing instructions: 5-bit signed constant offset: -16 to +15 9-bit signed constant offset: -256 to +255 16-bit signed constant offset: -32768 to +32767 Accumulator offset 16-bit constant indirect indexed Learn how to use following base index registers for instructions: X, Y, SP and PC Note that when: Offset is added to base index register to form effective address. Content of base register remains unchanged. The George W. Woodruff School of Mechanical Engineering ME4447/6405 Types of Indexed modes of Addressing 5-Bit Constant Offset Indexed Addressing: -16 to +15 Index mode uses: 5-bit signed constant offset is added to base index register (X, Y, SP or PC) To form effective address of memory location that will be affected by instruction. Offset ranges from -16 through +15. Majority of indexed instructions in real programming use offsets that fit in shortest 5-bit form of indexed addressing. LDAA $00, X A6 00 *load A with (X + $00) The George W. Woodruff School of Mechanical Engineering ME4447/6405 The following three statements are equivalent: STAA -8,X 6A 18 *Offset given in decimal STAA -$08,X 6A 18 *Offset given in hex STAA $FFF8,X 6A 18 *Offset given as 16-bit number Let X contain #$3000. After program executed, content of A will be stored at address (#$3000 - #$08) = $2FF8 $FFF8 = 1111 1111 1111 1000 0000 0000 0000 0111 1 --------------------------------------------- 0000 0000 0000 1000 = - #$0008 The George W. Woodruff School of Mechanical Engineering ME4447/6405 (Page 21) The George W. Woodruff School of Mechanical Engineering Base index register rr X 00 Y 01 SP 10 PC 11 ME4447/6405 5-bit Constant offset : -16 to +15 LDDA -16, X A6 10: -16 = -$10 $10 = 00010000 1’s Comp = 11101111 2’s Comp = 11110000 rr0nnnnn = 00010000 = $10 (this is the postbyte) bits 0-4 of offset LDAA 6, SP A6 86: 6 = $06 = 00000110 rr0nnnnnn = 10000110 = $86 (this is the postbyte) bits 0-4 of offset LDAA –14, SP A6 92 -14 = -$0E 0E = 00001110 1’s Comp = 11110001 2’s Comp = 11110010 rr0nnnnn: 10010010 = $92 (this is the postbyte) bits 0-4 of offset The George W. Woodruff School of Mechanical Engineering ME4447/6405 Types of Indexed modes of Addressing 9-Bit Constant Offset Indexed Addressing: -256 through +255 Uses 9-bit signed constant offset which is added to base index register (X, Y, SP or PC): To form effective address of memory location affected by instruction Offset ranges from -256 through +255. Content of base register is not changed after instruction is executed MSB (sign bit) of offset is included in instruction postbyte Remaining 8 bits are provided as extension byte after instruction postbyte in instruction flow. LDAA $FF, X A6 E0 FF *Assume X contains $1000 prior to instruct is executed LDAB -20, Y E6 E9 EC *Assume Y contains $2000 prior to instruct is executed First instruction will load A with value from ($1000 + $FF) = $10FF Second instruction will load B with value from ($2000 – 20) = $IFEC The George W. Woodruff School of Mechanical Engineering (Page 21) ME4447/6405 Base index register rr X 00 Y 01 SP 10 PC 11 9-bit Constant offset : -256 to +255 Postbyte Code (xb) is = 111rr0zs Z = 0 and s = 1 (when offset is a negative number-MSB of offset) Z = 0 and s = 0 (when offset is a positive number-MSB of offset) The George W. Woodruff School of Mechanical Engineering ME4447/6405 9-bit Constant offset : -256 to +255 LDAA -25, X A6 E1 E7: -25 = -$19 $19 = 00011001 1’s Comp = 11100110 2’s Comp = 11100111 = $E7 (this is the offset) 111rr0zs = 11100001 = E1 (this is the postbyte) LDAA 30, SP A6 F0 1E: 30 = $1E (this is the offset) = 00011110 111rr0zs = 11110000 = F0 (this is the postbyte) The George W. Woodruff School of Mechanical Engineering (Page 21) Types of Indexed modes of Addressing ME4447/6405 16-bit Constant offset : -32768 to +32767 The George W. Woodruff School of Mechanical Engineering Base index register rr X 00 Y 01 SP 10 PC 11 ME4447/6405 16-bit Constant offset : -32768 to +32767 Postbyte Code (xb) is = 111rr0zs Z = 1 and s = 0 : For the case when the offset is positive or negative. S is not = 1 during postbyte calculation when the offset is negative because Bit 15 of the 2’s complement offset is already 1 which Indicates a negative offset number Postbyte for positive offset is same as postbyte for negative offset ie EA The George W. Woodruff School of Mechanical Engineering ME4447/6405 16-bit Constant offset : -32768 to +32767 Postbyte code (xb) is 111rr0zs LDAA 280, y A6 EA 0118 280 = $0118 = 0000000100011000 (this is the offset) 111rr0zs = 11101010 = $EA (this is the postbyte) LDAA -280, Y A6 EA FE E8 -280 = -$0118 $0118 = 0000000100011000 1’s Comp. = 1111111011100111 2’s Comp. = 1111111011101000 = $FEE8 (this is the offset) 111rr0zs = 11101010 = $EA (this is the postbyte) The George W. Woodruff School of Mechanical Engineering ME4447/6405 Types of Indexed modes of Addressing Accumulator Offset Indexed Addressing In this indexed addressing mode: Effective address is sum of values in base index register and unsigned offset in one of accumulators. Value in base index register is not changed. Base indexed register can be X, Y, SP or PC and accumulator can be either 8-bit (A or B) or 16-bit (D) Content of A, B, or D accumulator added to base index register to form address LDAA B, X A6 E5 Instruction adds content of accumulator B to X register to form address from which accumulator A will be loaded. B and X are not changed by this instruction. The George W. Woodruff School of Mechanical Engineering ME4447/6405 (Page 21) Base index register rr X 00 Y 01 SP 10 PC 11 Detailed Explanation: Example: LDAA B, X •This is Indexed Addressing Mode with Accumulator Offset. •Opcode for LDAA is A6 for this mode. Ans: A6 E5 •From the table above, the formula for postbyte of this mode is: 111rr1aa •rr is 00 because Base Index Register is X •aa is 01 because Accumulator used for offset is B •11100101 = E5 in School hex of Mechanical Engineering The George W. Woodruff ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 Indexed Addressing Mode Postbyte Encoding (xb) The George W. Woodruff School of Mechanical Engineering ME4447/6405 Indexed Addressing Mode Postbyte Encoding (xb) - Continued The George W. Woodruff School of Mechanical Engineering ME4447/6405 Why is Pre-/Post-Increment/Decrement Useful? Example: Store Data Value #$20 into memory locations $2000 to $3000 Without Post-Increment LOOP ORG $1000 LDAA #$20 LDX #$2000 STAA $00,X INX CPX #$3001 BNE LOOP SWI END With Post-Increment LOOP ORG $1000 LDAA #$20 LDX #$2000 STAA 1,X+ CPX #$3001 BNE LOOP SWI END Note: “1” refers to the number of post increments, not an offset! Program on the Left requires 1 more byte of program memory and takes 1 more cycle to execute per run through the loop than the program on the right. This may make a large difference when the program is large and complex or when dealing with values larger than 16-bits. The George W. Woodruff School of Mechanical Engineering Types of Indexed modes of Addressing - Continued ME4447/6405 16-Bit constant indirect indexed addressing Indexed addressing mode adds 16-bit instruction-supplied offset to Base indexed register to form address of memory location that contains pointer to memory location affected by instruction. Instruction itself does not point to address of memory location to be acted on. Square brackets distinguished this addressing mode from 16-bit constant offset indexing. The George W. Woodruff School of Mechanical Engineering 16-Bit constant indirect indexed addressing ME4447/6405 LDAA [10, X] or LDAA [$0A, X] Assume: X holds base address of table of pointers X has initial value of $1000 #$2000 is stored at addresses $100A and $100B When instruction is executed: #$0A is added to value in X to form address $100A Address pointer ($2000) is fetched from memory $100A Value stored in $2000 is read and loaded into A accumulator The George W. Woodruff School of Mechanical Engineering ME4447/6405 Types of Indexed modes of Addressing - Continued • 16-Bit Constant Indirect Indexed Addressing ORG $1000 LDAB #$EE STAB $0400 *#$EE stored at $0400 LDD #$0400 STD $5DBC *#$0400 stored at $5DBC & $5DBD LDX #$5D00 *X contains #$5D00 LDAA [$BC, X] *#$BC added to value in X to form …… …… address $5DBC. Address pointer $0400 ...... …… fetched from memory at $5DBC. Value (EE) store in $0400 read & loaded in Acc. A …… …… SWI END The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 As stated before the Assembler translates an assembly language program into a machine language program Format of machine language program Instruction Operand Address where instruction is located Opcode Postbyte Or Blank if instruction does not use Operands (Note: This format is for Lecture and Tests only !! The real format the assembler outputs is “S19” and will be shown to you in Lab) The George W. Woodruff School of Mechanical Engineering ME4447/6405 Postbyte and Opcode Reference All Mnemonics and associated Op-codes can be found in Programming Reference Guide pages 6-19 Example: Programming Reference Guide Page 12 (Note: LDAA outlined in red) The George W. Woodruff School of Mechanical Engineering ME4447/6405 Indexed Addressing Mode Postbyte Encoding (xb) The George W. Woodruff School of Mechanical Engineering ME4447/6405 Indexed Addressing Mode Postbyte Encoding (xb) - Continued The George W. Woodruff School of Mechanical Engineering ME4447/6405 Postbyte Postbyte allows an op-code to be used for more than one instruction. Determined from Tables 1, 3 or 4 in the programming reference guide Instruction Opcode Postbyte LDAA 0,X A6 00 LDAA $02,SP+ A6 B1 LDAA B,Y A6 ED SUBB $1040,X E0 E2 SUBB D,Y E0 EE SUBB -14,X E0 12 Table 1 (Excerpt) The George W. Woodruff School of Mechanical Engineering ME4447/6405 (Programming Guide) Engineering The George W. Woodruff SchoolReference of Mechanical ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 The George W. Woodruff School of Mechanical Engineering ME4447/6405 Hand Assembling Example: Assemble the following Program ORG LDAA LDAB ABA STAA SWI END $1000 #$0A #$0B $00 Address Opcode Postbyte Operand $1000 86 0A $1002 C6 0B $1004 18 06 $1006 5A $1008 3F 00 (Note: $1002 since $86 is now at $1000 and $0A is at $1001) The George W. Woodruff School of Mechanical Engineering ME4447/6405 Example Problem 1 (revisited) ORG LDAB STAB INCB ADDB $1000 #$0A $1100 STAB SWI END $1090 $1100 *Load acc. B with number 0A *Store acc. B in address $1100 *Increment acc. B by 1 *Add memory location $1100 *to acc. B *Store acc. B in address $1090 *Software interrupt The George W. Woodruff School of Mechanical Engineering ME4447/6405 Hand Assemble Example Problem 1 (Revisited) ORG LDAB STAB INCB ADDB STAB SWI END $1000 #$0A $1100 $1100 $1090 Address 1000 1002 1005 1006 1009 100B Opcode Postbyte C6 7B 52 FB 7B 3F The George W. Woodruff School of Mechanical Engineering Operand 0A 1100 1100 1090 ME4447/6405 Example Problem 2 Write a short assembly language program that stores the content of Port T in memory location $3000 after waiting for 0.05 seconds for the input data. Solution Recall: One machine cycle = 0.125 x 10-6 s (8 MHz Bus Clock) We want the HCS12 to wait 0.05 s/0.125 x 10-6 s = 400,000 cycles One good way to make the HCS12 wait is to create a loop. The George W. Woodruff School of Mechanical Engineering ME4447/6405 Wait Loop LDY #$AD9C LDD #$0000 LOOP ABA CPX $2000 DEY BNE LOOP 2 cycles 2 cycles 2 cycles 3 cycles 1 cycle 3 cycles Note: These instructions are included to increase the operation time Assume the number of loops needed to wait is 2 bytes (2 + 3 + 1 + 3)*X + 4 = 400,000 cycles X = 44,44410 = $AD9C The George W. Woodruff School of Mechanical Engineering ME4447/6405 Example 2 Solution Solution *Remember that Port T is input upon reset ORG $1000 LDY #$AD9C *Load Y with 44,44410 LDD #$0000 *Clear Accumulator D LOOP ABA *Add the contents of B to A CPX $2000 *Compare X with the contents of *$2000 DEY *Decrement Y BNE LOOP *Branch to LOOP if Y is not equal *to zero LDAB $0240 *Load acc. B with content of $0240 STAB $3000 *Store content of acc. B in $3000 SWI *Software Interrupt END The George W. Woodruff School of Mechanical Engineering ME4447/6405 Homework Homework 1 • Write an assembly language program to clear the internal RAM in the MC9S12C32. • Write a program to add even/odd numbers located in addresses $0800 through $0900. Homework 2 • Write a program to find the largest signed number in a list of numbers stored in address $0A00 through $0BFF. Repeat for an unsigned number. The George W. Woodruff School of Mechanical Engineering ME4447/6405 QUESTIONS??? The George W. Woodruff School of Mechanical Engineering