GilbertVLSI2013 - Robust Low Power VLSI

advertisement

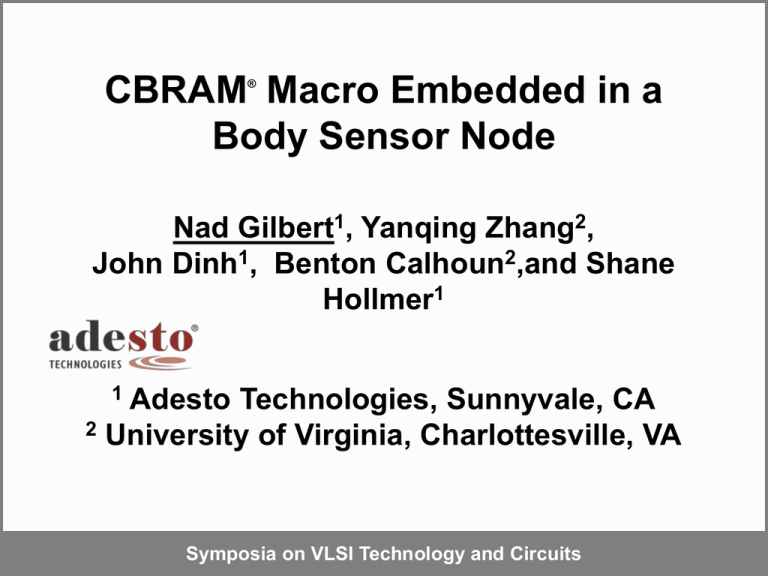

CBRAM Macro Embedded in a Body Sensor Node ® Nad Gilbert1, Yanqing Zhang2, John Dinh1, Benton Calhoun2,and Shane Hollmer1 1 Adesto Technologies, Sunnyvale, CA 2 University of Virginia, Charlottesville, VA Symposia on VLSI Technology and Circuits Outline • • • • • • • • • • Introduction - Ultra Low Power (ULP) CBRAM technology CBRAM Macro Architecture Energy Monitor Sensing Circuit and Energy measurement Results Write Circuit and Energy measurement Results Body Sensor Node (BSN) concept and results Die Photo Comparison of macro to Prior work Conclusion Slide 1 Introduction Typical Low Power Sensor Non-volatile Serial Flash The Missing ULP component Transceiver (Demonstrated in ULP system) Image courtesy of University of Washington TI SoC Microcontroller, 12 bit ADC, temperature sensor (Demonstrated in ULP system), 128KB embedded FLASH (The Missing ULP component) Slide 2 CBRAM Technology – Introduction < 20nm dimensions < 0.6V Operation Multi Level Cell < 1mA Write < 0.6V Write Conductive Bridging RAM (CBRAM) is a subset of Resistive RAM that is highly scalable low power high performance and can be integrated at Back-End-of-Line in a standard CMOS processes. 1Transistor – 1 Resistor Cell (1T1R) DRAM Cost Structure <50ns Write Large Read Signal Verify During Write Slide 3 CBRAM Technology – Cross section Data is stored by modulating the resistance of the dielectric layer. Anode Cathode TEM Transistor Slide 4 CBRAM Technology - Operation Voltage (V) Program at 600mV and 400nA 1T1R Cell 0.8 Anode 0.6 Tpg=14µs 0.4 Cathode Cathode 0.2 Anode 400nA 0 0 5 10 15 20 25 30 Voltage (V) Erase at 600mV and 200nA 1.2 Cathode 1.2V Ter=2µs Anode 1 0V 200nA Cathode 0.8 0.6 0.4 84 86 88 90 92 Anode Time (µs) Slide 5 CBRAM Macro Architecture Din Write ctrl x8 Write drivers Lvl Conv VWL x8 Array: 32 cols 256 rows x8 8:1 8:1 RD BLAN BLS WL •Dual bit line •Maximum device isolation •Dual supply domains • VDD (read) VCC (write) •Maximum usage of VCC •Minimized series resistance •Variable Word Line voltage RD 4:1 Slide 6 Voltage Across Cell ERASE 0V 0.6 V HALF SEL BL 0V 0.6 V 0.6 V 0.4V PROGRAM 0.6 V READ 0.4 V 0.4V 0V 0V ~0.2V 0V Slide 7 On Chip Energy Monitor VCCANALOG VREF Id(M1)=ILOAD M1 VMEAS •Dynamic Current monitor IBIAS VLOAD ILOAD IBIAS Energy monitor for each supply: VCC, VDD, and VWL Slide 8 Sensing Circuit Pull Up Programmable Pull up Strength VDD as low as 0.3V Read Strobe Data Out SN Read Strobe Source follower Voltage limit 8:1 Read Strobe 8:1 BLAN BLS WL Slide 9 Measured results of Sense circuit Energy Vs. Delay of Reading 1 Byte 10 Strength=0 0.39 pJ/B Delay (us) Strength=4 1 Strength=7 0.1 0.01 0.1 1 Energy (pJ) 10 100 Slide 10 Write Circuit VCC as low as 0.6V VCC VCC Data Dependent Program DinPROG 1 Minimized Series resistance write path drivers 1 OFF 1 VWL Data Dependent Erase DinERASE WL BLAN BLS Complete Isolation when not selected Slide 11 Measured Results of Program Operation Measured Program from CBRAM Array VMEAS (V), α IPROG 0.5 TPROG= 10us 200 160 0.4 120 80 0.3 40 leakage Current 0.2 Meas. Tot. E (pJ) VCC=0.6V, VWL=0.6V, VDD=0.4V 0 0 20 40 60 80 100 Time (μs) Slide 12 Program Energy vs. Supply Sim. Energy/bit to PROG time @ const Ron 6 Energy Minima at 1V Energy (pJ) 5 4 Ron=62.1k Ron=300k 3 Energy Minima at 0.7V 2 1 0 0.4 0.6 0.8 1 1.2 1.4 1.6 VCC (V) Slide 13 Measured Results of Write Operation Measured Erase from CBRAM Array VCC=0.6V, VWL=1V, VDD=0.4V 0.5 VMEAS (V), α IERASE 10 TERASE=23us 0.4 8 leakage Current 6 0.3 4 Meas. Tot. E (pJ) 12 2 0.2 0 0 10 20 30 40 50 60 70 80 Time (μs) Slide 14 Erase Energy vs. Supply Sim. Energy/bit to Erase time @ const Ron 80 70 60 High Ron, Low energy Energy (pJ) 50 Ron=62.5k Ron=602k 40 30 20 10 0 0.4 0.6 0.8 1 1.2 1.4 VCC (V) Slide 15 ClkConfig EnConfig ConfigBits IMEM CONFIG. SCAN CHAIN SystemClk ADC[7:0] ClkScan EnScan ScanBits IMEM DEBUG SCAN CHAIN Accel. Clks CBRAM IMEM Bus1[7:0] Bus2[7:0] Body Sensor Node (BSN) CBRAM DMEM DIGITAL POWER MANAGER CLOCK GEN. SCAN CHAIN OUT DMEM CONFIG. SCAN CHAIN DMA GPP RISC PROCESSOR RR ACCEL. AFIB ACCEL. FIR ACCEL. ENV DET ACCEL. ScanOutBits CBRAM was integrated with the Digital Platform only Slide 16 BSN Results Enable[5:0] 6’hxx 6’h3E 6’hxx 6’h3E ClkGt[6:0] 7’hxx 7’h01 7’hxx 7’h01 Rst[6:0] 7’hxx 7’h01 7’hxx 7’h01 Bus1_connect[12:0] 13’hxxxx 13’h1F9F 13’hxxxx 13’h1F9F Bus2_connect[12:0] 13’hxxxx 13’h17FE 13’hxxxx 13’h17FE 8’hxx 8’h80 RISC_out[7:0] 8’hxx Supply Status/Time Off/… 8’h80 On/10:45 AM Off/… On/5:55 PM Measured scan chain outputs showing correct operation of RISC processor from CBRAM, after power-down all day Slide 17 BSN (digital) and CBRAM Die Photograph Timing Blocks And Config. Scan Chains 64kb CBRAM DMEM 64kb CBRAM IMEM DPM Prog. FIR DMA CLK GEN Scan Out ENV DET RISC μProc RR+ AFib Slide 18 Comparison of Program Energy Program Energy (pJ) [3] [6] 1000 [4] 100 [5] 10 This work 1 0 1 2 3 4 5 6 7 8 9 10 11 Write Voltage (V) [3] 0.5V 4Mb embedded ReRAM [4] Flash with self-aligned split-gate cell [5] STT-MRAM [6] 4Mb embedded phase-change memory Slide 19 Comparison of Technology Metric [3] [4] [5] [6] CBRAM ReRAM FG Flash MRAM PCM CMOS Compatibility Yes Yes No Yes No Read Core Voltage (V) 0.35 0.32 0.5 1.2 1.2 Write Core Voltage (V) 0.6 2.0 10 3.3 2.8 Program Energy/bit 1 pJ 2 nJ 100 pJ 10 pJ 250 pJ Read Energy/bit 50 fJ 75 fJ 500 fJ 100 fJ 500 fJ No Yes Yes Yes Yes Technology Charge pumps needed for <1 V SoC This work Slide 20 Conclusion • Device – 2 CBRAM macros embedded in BSN • Technology – 0.13 mm standard CMOS • Array size – 64 kb • Operating voltage – Integrated in BSN 0.5V – CBRAM macro 0.4 V read 0.6 V write • Operating Frequency – 200 kHz • Write energy – 8 pJ Slide 21 Acknowledgements • Ralph Williams and Derric Lewis – Digital test interface of the CBRAM macro • Altis Semiconductor – Chip manufacturing • DARPA – Partial funding through an SBIR award Slide 22