Presentation

advertisement

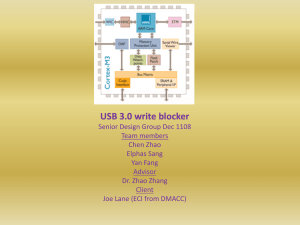

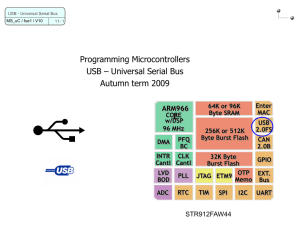

USB 2.0 Controller Anush Rengarajan Feng Zheng Thomas Madaelil Scope of Project Implement USB 2.0 Controller Based on EHCI(Enhanced Host Controller Interface) specification and ULPI (UTMI+ Low Pin Interface) USB 1.1 not supported. Driver Basic driver to test memory interface. EHCI Intel Spec for USB 2.0 Controllers Used in PCs Standardizes the Communication between Host Software and Controller Software emulated Root Hub ULPI Based on UTMI (USB 2.0 Transceiver Marcocell Interface) specification Low pin count interface to PHY. Standardizes interface between host controllers and external PHY. Block Diagram Request Descriptor Parse Descriptor PHY Interaction Post Process Transaction Division of Work Anush – Internal memories and interaction with ARM processor, driver Tom – Data Layer, combine IP Feng – Protocol Layer Device Driver Device Driver is a bare bone driver which initializes memory with data needed for the Hub Controller Not much progress was made with this as there were issues in debugging the design mapped to FPGA Used Device Driver to stimulate part of the design by using memory mapped Registers in FPGA Device Driver contd. The Transfer Descriptor Data needed by the Controller is initialized by the Device Driver in the Memory Block mapped into the FPGA Queue Head Array This Structure maintains the Queue Head Transfer Descriptor The Size of the Queue Head Transfer descriptors are 64 bytes Implemented as 16 entry array with each entry being 4 bytes Transfer Descriptor Array This Structure maintains the Isochronous or the Split Isochronous Transfer Descriptor The Size of this array is 64 bytes to accommodate the entire Descriptor Implemented as 16 entry array with each entry being 4 bytes Data Buffers There are 2 Data Buffers implemented to facilitate the Data Transfer to and from the Hub Controller Each Data Buffer is 1024 bytes to accommodate the maximum Data Transfer Size These are implemented using the FPGA RAM Blocks Data Buffers contd. Data Buffer In gets the data from the Protocol Layer and transfers the data to the memory Data Buffer Out transfers the data from the memory to the Protocol Layer These buffers are instantiated as RAM Block with the aspect ratio of 512 x 32 bits Data Layer Interacts between Protocol and Software Data Layer Protocol Layer Token Packet (Header defining what it expects to follow), an Optional Data Packet, (Containing the payload) and a Status Packet (Used to acknowledge transactions and to provide a means of error correction) Protocol Layer (Common USB Packet Fields) Sync - All packets must start with a sync field. The sync field is 8 bits long at low and full speed or 32 bits long for high speed and is used to synchronise the clock of the receiver with that of the transmitter. PID - Packet ID. This field is used to identify the type of packet that is being sent. ADDR - The address field specifies which device the packet is designated for. Being 7 bits in length allows for 127 devices to be supported. ENDP -The endpoint field is made up of 4 bits, allowing 16 possible endpoints. Low speed devices, however can only have 2 additional endpoints on top of the default pipe. CRC - Cyclic Redundancy Checks are performed on the data within the packet payload. All token packets have a 5 bit CRC while data packets have a 16 bit CRC. EOP - End of packet. Protocol Layer Protocol Layer (Token Packet Fields) In - Informs the USB device that the host wishes to read information. Out - Informs the USB device that the host wishes to send information. Setup - Used to begin control transfers. Start of Frame Packets -The SOF packet consisting of an 11-bit frame number is sent by the host every 1ms ± 500ns on a full speed bus or every 125 µs ± 0.0625 µs on a high speed bus. Sync PID ADDR 00000001 10100101 0000100 ENDP CRC5 EOP 0111 10100 XX1 Protocol Layer (Data Packet, Handshake) Data0, Data1, (DATA2 and MDATA.) Maximum data payload size for high-speed devices is 1024 bytes. Data must be sent in multiples of bytes. Sync PID Data CRC16 EOP 00000001 11000011 00000000100000000100000011000000 1111011101011110 XX1 ACK - Acknowledgment that the packet has been successfully received. NAK - Reports that the device temporary cannot send or received data. Also used during interrupt transactions to inform the host there is no data to send. STALL - The device finds its in a state that it requires intervention from the host. Sync PID EOP 00000001 00101101 XX1 Results / Future Work Tested and synthesized individual blocks Requires Split transaction Interface between USB controller and the PHY, or transceivers, that drives the actual bus USB controller should operate Full/Low speed devices to meet 2.0 spec. Back up Lessons Learned Create written specification for inter-module communication of blocks early in design Xilinx Synthesis quirkiness with Array Design . Initially the Array was Synthesized as flops which took for ever !!! Example Transaction( make a picture?) Data Layer sends request to local memory controller to load transaction descriptor from memory Once descriptor is loaded, data layer parses descriptor and sends transaction data to protocol layer Protocol layer takes transaction data and interacts with phy via ULPI interface Protocol returns transactions status to data layer for post processing Data layer post processes data and requests local memory controller to write data to memory