Presentation Part A - High Speed Digital Systems Lab

DDRIII BASED GENERAL

PURPOSE FIFO

ON VIRTEX-6 FPGA ML605 BOARD

PART A PRESENTATION

STUDENTS:

OLEG KORENEV

EUGENE REZNIK

SUPERVISOR:

ROLF HILGENDORF

Semester: spring 2012

CONTENT

1.

Project overview

2.

Specifications

3.

Part A goals

4.

Memory on ml605

5.

AXI4

6.

Part A overview

7.

Part B goals and Workflow

8.

Timeline

PROJECT OVERVIEW

Design and implementation of General Purpose FIFO IP core which allows usage of external memory (DDR3) as FIFO storage on Xilinx FPGA device

• Design and implement generic IP core of FIFO

• Design and implement GUI generator of IP core on PC

• Create sample design with implemented IP core

SPECIFICATIONS

Hardware

• Xilinx Virtex-6 ML605 FPGA Evaluation Kit

• DDR III memory

• Ethernet interface

• PC with Ethernet interface

Software

• ISE Design Suite Logic Edition Version 14.3

• Modelsim

• Wireshark

• Winpcap library

OUR GOALS PART A

• Gain experience in hardware development

(VHDL environment)

• Explore and expertise FPGA work environment

• Create design with configurable

• word size

• FIFO depth

• Achieve best performance

• Minimize usage of FPGA resources

• Make our world a better place

MEMORY ON ML605

DDR3 memory

• Capacity: 512MB

• Max theoretical bandwidth: 800MT/s*64bit = 6.4GB/sec

Xilinx provides us with DDR3 controller which has AXI Memory

Mapped interface

• AXI bus data width up to 1024 bit

• 256 bit for max memory performance, assuming bus works with 200Mhz

AXI

4

Xilinx provides us with AXI4 Memory Mapped bus, which is a standard bus used in modern ARM SoC.

Features

• Separate Address/Control and Data Phases

• burst-based transactions with only start address issued

• separate read and write data channels

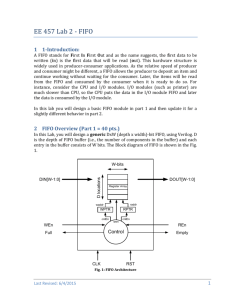

GENERAL PURPOSE FIFO

AXI4 Interface

CONTROLLER

FIFO TO MEMORY MEMORY TO FIFO

F

I

F

O

F

I

F

O

Native Fifo Interface

GENERAL PURPOSE FIFO

INTERFACE

AXI4 Native FIFO

PART A OVERVIEW

GENERAL PURPOSE FIFO

Interface

• GP FIFO has native FIFO interface

• Word size can be 32, 64, 128, 256, 512, 1024 bit

• Utilizes DDR3 memory through AXI interconnect

• Depth is limited only by available RAM memory on DDR3

Internal architecture

• Internal FIFO-To-Memory controller

• Internal Memory-To-FIFO controller

• Internal Bypass controller

Arbitration between GP FIFOs is managed by AXI interconnect

EXAMPLE DESIGN BLOCK DIAGRAM

HOST STORAGE LOGIC STORAGE DDR3

MEMORY CONTROLLER

AXI4 BUS (INTERCONNECT)

USER STORAGE

General

Purpose Fifo

General

Purpose Fifo

MAC Module

MAC Controller

HOST

Example Design

PART A OVERVIEW

EXAMPLE DESIGN

Interface

• Utilizes Ethernet MAC level of communication

• Software has simple and intuitive interface

• Software handles all the data transmission in between host and GP FIFO

Internal architecture

• MAC module

• GP FIFO

• Simple example of a logic which uses GP FIFO

MAC can potentially provide us with a considerably high speed of data transmission, the bottleneck is software - driver performance

PART A OVERVIEW

CONCLUSION

Our design meets the requirements of the project.

• GP FIFO is fast limited only by interconnect bus available bandwidth

• GP FIFO has potentially configurable depth and word size

• GP FIFO is simple, utilizes small amount of resources on the board

GP FIFO gives you another easy way to pass big chunks of data from one module to another.

Our example design provides you with efficient communication in between a host and the board.

OUR GOALS PART B

• Generalize our GP FIFO

• Simulate and test all the possible configurations and their exceptional case

• Make possible optimizations

• Close timing on each configuration

• Develop software generator of GP FIFO IP core

• Write detailed manual for IP core and for it ’s generator

Task

TIMELINE

Duration 7/4 14/4 21/4 28/4 5/5 12/5 19/5 26/5 2/6 9/6 16/6

Generalize GP

FIFO

2 weeks

Optimizations 2 weeks

Simulation and

Testing 3 weeks

Close Timing 2 weeks

Develop IP core generator

3 weeks

Write manual 2 weeks