IRP Presentation

advertisement

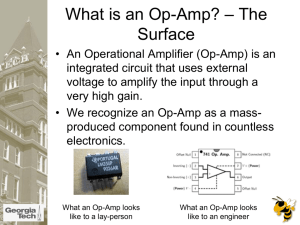

Mixed-Signal Option for the Teradyne Integra J750 Test System May08-12 Emily Evers Vincent Tai Problem Statement The Teradyne system has been updated to allow for analog circuits to be tested, but there are no working test files for ADC, DAC and Op-Amps. Concept Sketch and System Block Diagram Hardware IG-XL Software Documentation Devices Hardware Software System Description Devices Analog-to-Digital (ADC) Digital-to-Analog (DAC) Op-Amp IG-XL Software Hardware Device Interface Board (DIB) Connects daughter board to tester via pogo pins Daughter Board Connects device to DIB Test Plan Pin and Channel Map AC and DC Specs Timing Pattern Documentation Updated Cookbook Commented IG-XL files 4 User Interface and Operating Environment User Interface IG-XL Software Cookbook DIB Operating Environment The room environment needs to be kept at a consistent temperature of 25°C ± 3° Electrostatic discharge wrist bands must be worn when using the tester Access code Requirements Functional Cookbook be written for the new users Testing procedures covers the devices: Analog-to-Digital (ADC) Digital-to-Analog (DAC) Op-Amp Nonfunctional Documentation in English Test program for devices and similar ones Cookbook for specified devices Easy to trouble shooting Market Survey Teradyne website Previous team’s website Teradyne lab manuals Work Breakdown Structure Review Status Previous work Teradyne Training Material IC Interface Test Plan Development Daughter Board DIB Documentation Create IG-XL code for testing devices Debug previous code Add current limits New test plans Execute testing Create Mixed-Signal Option Cookbook Create maps for daughter board, DIB and socket converters Reporting Project Schedule Resource Requirements Resource Team Faculty Advisor: Dr. Weber Faculty Advisor: Dr. Smith Team effort Review Status IC Interface DAC ADC Op-Amp Documentation Reporting Total hours Emily Evers 30.75 17 7 29 5 15 31.5 135.25 Vincent Tai 22 18.5 10 20 15 10 15 110.5 Total 52.75 35.5 17 49 20 25 46.5 245.75 10 Resource Requirements Financial requirements Item Cost Materials Poster $35.00 Devices $130.00 Daughterboard $200.00 Subtotal $365.00 Emily Evers $1352.5 Vincent Tai $1105 Subtotal $3562.5 Labor($10.00/hr) Total $3927.5 11 Risks Risk: Problems learning program Limited team members Risk Management: Read Teradyne manuals and previous groups documentation Time management Design Method Inputs Process Outputs Parts Results Cookbook ADC DAC Input/Output Signals Op-Amp Calculations AD7892 AD7470 AD5440 AD5447 AD823 Hardware Software IG-XL Program ADC & DAC Op-Amp INL & DNL Bandwidth Offset Voltages Intermodulation Tests Interfaces J750 Tester DIB Daughterboard Socket converter Computer Input and Output Specification Input DAC LTC1450 Op-Amp AD823 ADC AD7470 Output Input signals Output signals Calculations ADC DAC INL and DNL INL and DNL Op-Amp Offset Voltage Bandwidth Intermodulation Distortion Hardware, Software, and User Interface Specification Hardware Daughterboard DIB Socket converter User Interface Updated Cookbook IG-XL test files Software Pattern Tool IG-XL Pin and Channel Maps AC, DC, and Global Specs Time sets and Pin Levels Test Procedures Test Specification Component Test Test individual IG-XL source and capture System Test Test IG-XL test file and pattern Detailed Design DAC Schematic 17 Detailed Design Op-Amp Schematic 18 Detailed Design ADC Schematic 19 Build – Pin Map Define pins on IG-XL 20 Build – Channel Map Define connections from daughterboard to tester DAC 21 Build – Channel Map Op-Amp 22 Build – Channel Map ADC 23 Build – Board Wiring 24 Build – AC Specs Specify AC variables 25 Build – DC Specs Specify DC variables 26 Build – Pin Levels User specify voltage level for high/low logic level. 27 Build – Time Sets Create timing basis for pattern Allow for testing on digital pins 28 Build – Test Procedures Set up user defined tests 29 Build – Test Instances Set up IG-XL template tests Input data for user defined tests 30 Build – Pattern Uses time sets from IG-XL file User defined inputs Can be used to start analog and digital source and capture signals 31 Build – Pattern Several sheets are used in the pattern file Pin Lists Imports (time sets) Instruments 32 Test System testing was done using an oscilloscope 33 Test Test Teradyne System Testing Functional Test Continuity Test 35 Test Functional and Continuity Outputs 36 Earned Value Analysis Budgeted Cost of Work Scheduled: $4365 Actual Cost of Work Performed: $3650 Budgeted Cost of Work Performed: $3895 Cost Variance: $3530 Schedule Variance: -$470 Cost Performance Index: 1.067 Schedule Performance Index: 89.23% 37 Lessons Learned Team Work The value of hands-on experience Verify Input Signals: Use oscilloscope and multimeter. 38 Conclusions Accomplishments Updated CprE 210 D-flip flop test Created an interface mapping of the current boards ADC Wired daughter board Created IG-XL test file Ran tests Conclusion Accomplishments DAC Wired daughterboard Created IG-XL test file Op-Amp Wired daughterboard Created IG-XL test file Updated Cookbook 40 Conclusions Future Work Run tests on DAC and Op-amp Fix if needed Finish ADC test file