DIGITAL.

INTEGRATED

CIRCUITS

THOMAS A. DEMASSA

ARIZONA STATE UNIVERSITY

ZACK CICCONE

VLSI TECHNOLOGY INC.

JOHN WILEY & SONS

New York • Chichester • Brisbane • Toronto • Singapore

Acquisitions Editor Steven M. Elliot

Marketing Manager Debra Riegert

Designer Laura Nicholls

Manufacturing Manager Mark Cirillo

Production Service University Graphics Production Services

Cover Photo: Fuzzy Logic Chip/Courtesy VLSI Technology, Inc.

Recognizing the importance of preserving what has been written, it is

a policy of John Wiley & Sons, Inc. to have books of enduring value

published in the United States printed on acid-free paper, and we

exert our best efforts to that end.

The paper on this book was manufactured by a mill whose forest

management programs include sustained yield harvesting of its

timberlands. Sustained yield harvesting principles ensure that the

number of trees cut each year does not exceed the amount of new

growth.

Copyright © 1996, by John Wiley & Sons, Inc.

All rights reserved. Published simultaneously in Canada.

Reproduction or translation of any part of

this work beyond that permitted by Sections

107 and 108 of the 1976 United States Copyright

Act without the permission of the copyright

owner is unlawful. Requests for permission

or further information should be addressed to

the Permissions Department, John Wiley & Sons, Inc.

Libran; of Congress Cataloging in P11blication Data

DeMassa, Thomas A

Digital integrated circuits/ Thomas A. DcMassa, Zack Ciccone.

p.

cm.

Includes index.

ISBN 0-471-10805-7 (cloth: alk. paper)

1. Digital integrated circuits. I. Ciccone, Zack. II. Title.

TK7874.65.D38

1996

95-312

621.3815-dc20

CIP

10 9 S 7 6 5

To my patient and loving wife, Joann;

To Kari, Tom and Dcbb,

Andrea, as well as Mary and Karen

-with particular thanks to my mom and dad for their lifelong support

Tha111as A OcMassn

To the memory of Louise Ciccone and David E. Duick

Zack Jahn Ciccone

BACKGROUND

GOALS

Digital Integrated Circuits is intended as a textbook

suitable for electrical engineering students as well as

electronic technology students. This text has been

used in note form for a senior/first-year graduatelevel electrical engineering course and an upper-level

electronic technology course with excellent results. It

can also serve as a self-teaching tool for practicing

circuit designers in the IC development profession or

as a reference for engineers in industry that need

familiarization with the operation and design of various digital integrated circuits.

The text, written in a clear and concise manner,

provides maximum coverage of the material and

requires a minimum of instructor support. This

is achieved by providing complete, qualitative

descriptions of circuit operation followed by indepth analysis and SPICE simulations whenever appropriate. There are numerous example problems

throughout the text, and solutions have been provided. These problems enhance the text material and

provide an additional learning tool for the reader.

Both static and transient operation are considered in

detail.

The text provides the most extensive coverage

of digital integrated circuit principles available in a

single resource. The circuit families described in

detail are: transistor-transistor logic (TTL, STTL,

and ASTTL), emitter-coupled logic (ECL), NMOS

logic, CMOS logic, dynamic CMOS, BiCMOS

structures, and various GASFET technologies. In

addition to presentations of the basic inverter

circuits for each digital logic family, complete details

of other logic circuits for these families are presented. The logic circuits include NAND, AND,

NOR, OR, XOR, XNOR, complex logic functions

such as AOI and OAI, as well as latches, flip-flops,

memory elements, and Schmitt trigger gates. A manual is provided with the book which contains the

solutions to the end-of-chapter problems, and

a detailed outline for a general course study of 15

weeks.

We had definite goals in mind as we were preparing

this manuscript for publication. Some of those goals

were:

V

1.

To offer extensive knowledge and a broad background base for the operation and design of

digital integrated circuits by furnishing easy-toread descriptions and including numerous

examples

2.

To describe the details of the internal operation

and use of digital integrated circuits

3.

To emphasize CMOS digital logic, since this

circuit family has become the most extensively

used

4.

To provide extensive and detailed descriptions of

the operation and design of gallium arsenide

digital-logic families

5.

To present a thorough description of the operation of various logic gates from each family, not

just the inverters. Entire chapters are dedicated

to the following:

a. TTL design of AND, NOR, OR, complex

AOI and OAI, Schmitt trigger, and tri-state

gates

b. ECL design of AND and NAND (not just OR

and NOR) gates using collector dotting and

series gating methods

c. CMOS and NMOS design of NAND, NOR,

complex AOI and OAI, XOR, XNOR, tristate, Schmitt trigger, as well as dynamic

CMOS gates

6.

To explain the DC behavior, as well as the transient behavior of digital integrated circuits

7.

To compare SPICE modeling for each of the

digital logic families with theoretical circuit

analysis

8.

To demonstrate the operation and design

of latches, memory circuits, and BiCMOS

gates

VI

Preface

IMPROVEMENTS ON THE

COMPETITION

In writing this text, extremely important topics have

been addressed without skipping steps. There are

over 200 clearly written examples that have been

worked out. Furthermore, learning is promoted by

the fact that the order of each family has been done

in a similar fashion. Additionally, a new technique of

Kirchoff's Voltage law (KVLt shown along a dashed

path in a complex circuit figure, allows the reader to

rnaximize ltis understanding of this new approach. A

great deal of the material contained in the STTL,

ECL, NMOS, CMOS, and gallium arsenide digital

integrated circuit chapters is not available in any

other textbook.

Chapter 1 introduces the basic properties and

definitions of digital integrated circuits and the five

basic combinational logic operations for digital

electronic circuits (NOT, AND, OK NAND, and

NOR).

Chapter 2 describes the behavior of semiconductor PN junction diodes and metal-semiconductor

MN Schottky diodes. These two-terminal devices are

used in digital logic circuits to perform logic operations, provide DC voltage level shifting, as well as to

operate as variable capacitors and clamping diodes

at logic circuit inputs and outputs. The diode SPICE

model also is completely detailed.

Chapter 3 indicates basic methods used to fabricate bipolar junction transistors (BJTs) in digital

logic families. Also, the BJT modes of operation and

the BJT models, Ebers-Moll, Gummel-Poon, and

SPICE are described.

Chapters 4-15 deal with bipolar digital integrated circuits. The resistor-transistor logic (RTL)

family is described in Chapters 4 and 5. This family

was the first logic family to be commercially available. RTL has very poor power-speed performance,

due primarily to the use of resistors. To improve RTL

circuits, diode-transistor logic (DTL) was introduced

based on the design of preexisting circuits. Basic and

modified DTL circuits are described in Chapter 6. As

the name implies, circuits of the DTL logic family use

diodes and transistors in their design. However, because this family uses a resistor as the passive pullup element DTL circuits provide poor pull-up

speeds. In 1965, the transistor-transistor logic (TTL)

family was introduced. This name implies that the

usage of diodes in DTL was replaced with transistors

in TfL. Basic TTL circuits are described in Chapter

7. The resulting TTL circuits provided increased fanout, improved transient response, and a reduction in

chip area. The main improvement in TTL design over

DTL was the inclusion of an active pull-up subcircuit.

This resulted in faster charging of the equivalent output capacitance which improves the output rise time.

Standard TTL circuits, however, continue to have the

disadvantage of long propagation delay time because

these circuits provide operation in the saturation

mode. This can be avoided when Schottky transistors

are used in place of ordinary bipolar transistors. In

1970, Schottky transistor-transistor logic (STTL) was

introduced. The major advantage of using STTL circuits was a much-improved delay time because the

Schottky-clamped BJTs can not operate in the saturation mode. Hence, the switching speed was improved and the time delays shortened. In 1985, advanced Schottky TTL (ASTTL) was introduced. These

circuits were made possible in part by improving BJT

fabrication techniques. Ion implantation, 3 µ minimum size, and oxide isolation were major improvements that reduced the ASTTL propagation delays,

while maintaining the typical power dissipation.

Schottky TTL circuits are described in Chapters 8-10.

Another important bipolar digital logic family is

emitter-coupled logic (ECL). ECL circuits are described in Chapters 11-15. The BJTs in ECL circuits

operate only in the forward-active and cutoff regions.

Therefore, the major improvements of ECL circuits

are the faster switching time and larger fan-out.

Moreover, ECL has a smaller logic swing than TTL.

This small logic swing combined with the use of

emitter-coupled pairs eliminate current spikes and

result in a lower susceptibility to noise. However, the

improved performance is achieved at the expense of

much higher power dissipation among all of the logic

families.

In Chapter 16, silicon MOS transistors are introduced. This chapter contains the semiconductor

field-effect transistors (MOSFETs) including geometry, modes of operations, parameters, and the

SPICE MOSFET model.

In Chapters 18-22, NMOS digital circuits are described. The NMOS digital logic families detailed are:

The resistor loaded NMOS, the saturated enhancement-only loaded NMOS, the linear enhancementonly-loaded NMOS, and the enhancement-deple-

Preface

tion loaded NMOS. The basic NMOS circuits can be

augmented to perform all of the combinational logic

functions. These circuits are presented in Chapter 22.

Chapter 23 introduces the important features of

complementary MOS (CMOS) inverters, including

modes of operation, power dissipation, fan-out, and

latch-up. Currently, CMOS is the most widely used

digital circuit technology and this family is emphasized throughout this text. CMOS logic families have

the lowest power dissipation and the highest packing

density of all logic families.

In Chapters 24-27, the various combinational

CMOS digital logic circuits are presented. CMOS tristate gates are discussed as well as a presentation of

output contention. CMOS Schmitt trigger circuits

exhibiting output hysteresis are implemented using

source-follower feedback MOSFETs. The hysteresis

is the result of the output feedback to intermediate

points of stacked NMOS and PMOS transistors.

Gates with such an output hysteresis have a high

noise immunity and are useful for noisy inputs, non

rail-to-rail inputs, and slow inputs.

Chapter 28 deals with additional forms of CMOS

logic referred to as dynamic CMOS logic; pseudo

NMOS logic, dynamic CMOS logic, and CMOS

domino logic.

Chapter 29 compares digital logic families. These

include the various silicon integrated circuits families

(both bipolar and MOS) as well as the high speed

gallium arsenide logic families.

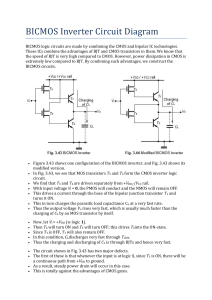

Chapter 30 describes circuits referred to as

BiCMOS. This is an advanced technology digital in-

VU

tegrated circuit family that consists of both bipolar as

well as CMOS transistor structures on the same chip.

Such BiCMOS circuits provide the advantages of bipolar and CMOS technologies.

Chapter 31 contains a detailed description of

both latches and flip-flops. These are the memory

elements in the digital integrated circuit area. Edgetriggered and tri-statc gates are also described.

In Chapters 32 and 33, semiconductor memory

circuits are provided. Chapter 32 includes the readonly memories (ROMs) and Chapter 33 describes

static random access memories (RAMs). Diode, transistor, NMOS, and CMOS memories are described

in detail.

Chapter 34 provides details of the metal-semiconductor FET called the MESFET. A model is developed for these devices that leads to the SPICE

NMESFET model.

Chapters 35-37 detail the important gallium arsenide digital logic circuits. The important families

described are: (1) the direct-coupled NMESFET logic

(DCFL) family, (2) the Schottky diode NMESFET

logic (SDFL) family, and (3) the buffered NMESFET

logic (BFL) family.

Finally, Chapters 38 and 39 provide descriptions

of various other gallium arsenide digital logic families. Chapter 39 also includes various gates such as

DCFL OR gates, BFL NOR gates, and a DCFL XOR

gate. Additionally, transmission gates and RAM

memory elements are discussed in Chapter 39.

Thomas A. DeMassa

Zack Ciccone

ACKNOWLEDGMENTS

The authors would like to thank the many colleagues

and students who suggested corrections and changes

to the original manuscript. In addition, thanks are

extended to

Manda J. Turley

Linda Rawles

Marney Thompson

Sherrie Benton

Jennifer Yee

Jeff Miles

Beth J. Quang

Steve J. Macia

Victor Tiginini

Ron Roedel

Ginny Reggiani

Deborah Thornber

Douglas Cochran

Chris Springfield

Chris J. Ciccone

Tom J. Ciccone

Richard J. Huebner

Wendell Wells

Debra DeMassa

Edward Gyeki

Suzanne Azzarella

Shankar Chandrashekaran

Hiram Upadhyay

Joseph Perez

Bhaskar Aravind

Mathew Joseph

Sharada Yeluri

Peter J. Young

Mindy J. McCormick

Brian G. Kirkland

Shannon Bushard

Rakesh Cheerla

Denise J. Marques

Tim Beatty

Carl Liepold

Melanie J. Nemetz

Dawn J. Johnson

Dena J. Douglas

John Crum

Marc Buer

Edie J. Eiker

Val J. Lipton

Jim J. Corbett

Chuck J. Day

Allen Sulliven

The authors would also like to thank the following

reviewers for their comments and suggestions:

Arthur D. van Rheenen

University of Minnesota

Richard B. Brown

University of Michigan

Krzyszof Iniewski

University of Toronto

Edward Maby

Rensselaer Polytechnicd Institute

Walter Varhue

University of Vermont

Darrell L. Vines

Texas Tech University

Special thanks are extended to Steven J. Nemetz.

ix

CONTENT

1

PROPERTIES AND DEFINITIONS

OF DIGITAL ICS

1

1.1

1.2

1.3

1.4

1.5

1.6

1. 7

1.8

1.9

Inverting and Non-Inverting Gates 1

Ideal Logic Elements 2

Inverter Voltage Transfer Characteristic

Logic Swing and Transition Width 6

Noise in Digital Circuits 6

Fan-In and Fan-Out 7

Transient Characteristics 8

Power Dissipation 10

Power-Delay Product 11

2

DIODES

2.1

2.2

2.3

2.4

2.5

2.6

2.7

2.8

PN Junction and MN Schottky Diodes 15

Diode Modelling 15

Diode Capacitance 18

SPICE Diode Model 18

Diode- Resistor Logic 19

Level-Shifted Diode-Resistor Logic 21

Clamping Diodes 23

Level-Shifting Diodes 24

3

BIPOLAR JUNCTION

TRANSISTORS

5

15

27

Junction Isolated NPN BJT 27

Oxide Isolated NPN BJT 27

3.3

Multi-Emitter BJT 27

3.4

Schottky-Clamped BJT 28

3.5

Lateral PNP BJTs 31

3.6 The Ebers-Moll BJT Model 31

3.7 BJT Modes of Operation 32

3.8 The Gummel-Poon BJT Model 35

3.9

SPICE BJT Model 37

3.10 Integrated Circuit Resistors 39

3.2

4.1

4.2

4.3

4.4

INTRODUCTION TO BIPOLAR

DIGITAL CIRCUITS

Analysis of BJT Circuits with Known

States 42

BJT Inverter 45

TTL Super-Circuitry 46

Level-Shifting BJTs 48

4.6

4.7

4

3.1

4

4.5

RESISTOR-TRANSISTOR

LOGIC (RTL)

56

5.1

5.2

5.3

5.4

5.5

5.6

5.7

5.8

5.9

5.10

Basic RTL Inverter 56

Basic RTL NOR Gate 56

Basic RTL NAND Gate 57

RTL Fan-Out 59

RTL Power Dissipation 62

Basic RTL Non-Inverter 62

Basic RTL OR and AND Gates 64

RTL with Active Pull-Up 64

RTL SPICE Simulation 67

Direct Coupled Transistor Logic and Current

Hogging 68

6

DIODE-TRANSISTOR

LOGIC (DTL)

6.1

6.2

6.3

6.4

6.5

6.6

6.7

Basic DTL Inverter 72

Modified DTL 73

Transistor Modified DTL 74

DTL NAND Gate 75

DTL Fan-Out 75

DTL Power Dissipation 78

DTL SPICE Simulation 80

7

TRANSISTOR-TRANSISTOR

LOGIC (TTL)

7.1

7.2

7.3

42

Discharge Paths and Base Driving

Circuitry 48

Self-Biasing BJTs 49

Power Dissipation of Bipolar Logic

Circuits 50

7.4

7.5

7.6

7.7

72

83

Basic TTL Inverter 83

Comparison of Stored-Charge Removal from

DTL and TTL 84

Basic TTL NAND Gate and the MultipleEmitter BJT 85

Standard TTL NAND Gate with Totem Pole

Output 85

Standard TTL Voltage Transfer

Characteristic 87

TTL Fan-Out 89

TTL Power Dissipation 91

xii

Table of Contents

7.8

Open -Collector TI"'L 91

7. 9 Low Power TTL (L TTL) 92

7.10 High Speed TTL (HTTL) 92

7.11 TfL SPICE Simulation 93

8

SCHOTTKY TRANSISTORTRANSISTOR LOGIC (STTL)

8.1

8.2

8.3

8.4

8.5

8.6

8.7

Schottky-Barrier Diodes 98

Schottky-Clamped BJTs 98

Schottky-Clamped TTL (STTL) 101

STIL Fan-Out 104

STTL Power Dissipation 104

Low-Power STTL (LSTTL) 107

STTL SPICE Simulation 110

9

ADVANCED SCHOTTKY

TRANSISTOR-TRANSISTOR

LOGIC (ASTTL)

9.1

9.2

9.3

98

12

TEMPERATURE

COMPENSATING EMITTERCOUPLED LOGIC

12.1

12.5

12.6

12.7

MECL II with Temperature Compensating

Bias Network 171

DC Analysis of the Bias Network 173

The Need For Temperature

Compensation 174

Bias Network Compensation for

Temperature Variation 176

Fan-Out of MECL II 177

Power Dissipation of MECL II 177

MECL II SPICE Simulation 179

13

MECL III and ECL 10K

12.2

12.3

12.4

115

Advanced LSTTL (ALSTTL) 115

Fairchild Advanced Schottky TTL

(FAST) 118

Advanced Schottky Transistor-Transistor

Logic (ASTTL) 121

13.1 MECL III 182

13.2 MECL III Voltage Transfer

Characteristic 183

13.3 MECL III Fan-Out 185

13.4 MECL III Power Dissipation 187

13.5 ECL 10K Series 189

13.6 ECL 10K Series SPICE Simulation

14

10

OTHER TTL GATES

124

10.1

10.2

10.3

10.4

10.5

10.6

TTL AND Gates 124

TTL NOR Gates 129

TTL OR Gates 131

TTL AND-OR-Invert (AOI) Gates 133

TTL XOR Gates 137

TTL Schmitt Trigger Inverters and NAND

Gates 140

10.7 TTL Tri-State Buffers 144

11

BASIC EMITTER-COUPLED

LOGIC (ECL)

11.1 BJT Current Switch 155

11.2 ECL Current Switch Voltage Transfer

Characteristic 156

11.3 ECL Super-Circuitry 158

11.4 Basic ECL NOR/OR Gate 159

11.5 MECL I NOR/OR Gate with Output

Buffers 161

11.6 MECL I Voltage Transfer Characteristic

11.7 MECL I Fan-Out 163

11.8 MECL I Power Dissipation 165

11.9 MECL I SPICE Simulation 167

1n

182

189

MODERN EMITTER-COUPLED

LOGIC

194

14.1 100K ECL Subfamily 194

14.2 DC Analysis of the 100K ECL Bias

Network 196

14.3 Bias Network Compensation for

Temperature Variation 198

14.4 Power Dissipation of 100K ECL

Subfamily 199

14.5 Other ECL Families 199

155

15

OTHER ECL GATES

15.1

Use of NOR/OR Gates as AND/NAND

Gates with Inverted Inputs 201

Collector Dotting Wired-AND Gates 202

Collector Dotting Complex OR-AND Logic

Gates 206

Series Gating-Basic ECL NANO/AND

Current Switch 208

Series Gating NANO/AND Gate 211

Series Gating Complex OR-AND

Gates 215

ECL XOR/XNOR Gates 216

ECL Decoding Tree 219

15.2

15.3

15.4

162

15.5

15.6

15.7

15.8

201

Table of Contents

16

METAL OXIDE

SEMICONDUCTOR FIELD

EFFECT TRANSISTORS

19.2

221

16.1

16.2

16.3

16.4

16.5

16.6

16. 7

16.8

16.9

16.10

Metal Gate N-Channel MOSFETs 221

Silicon Gate N-Channel MOSFETs 221

MOSFET Modes of Operation 221

MOSFET Transconductance Parameter 225

MOSFET Threshold Voltage 226

P-Channel MOSFET 227

MOSFET Capacitances 227

SPICE MOSFET Model 228

CMOS Devices 230

Integrated Circuit Capacitors 232

17

INTRODUCTION TO MOS

DIGITAL CIRCUITS

RESISTOR LOADED NMOS

INVERTER

Graphical Determination of Saturated

Enhancement-Only Loaded NMOS Inverter

VTC 263

19.3 Calculation of VTC Critical Points for

Saturated Enhancement-Only Loaded

NMOS Inverter 264

19.4 Body Bias Considerations for Saturated

Enhancement-Only Loaded NMOS

Inverter 266

19.5 Power Dissipation of Saturated

Enhancement-Only Loaded NMOS 270

19.6 Saturated Enhancement-Only Loaded

NMOS SPICE Simulation 271

20

234

17.1 General NMOS Inverter 234

17.2 The Zero Drain Current Active

MOSFET 234

17.3 Graphical Solution of the NMOS

Inverter 237

17.4 Partial Differentials 239

17.5 Analytical Solution of the NMOS

Inverter 240

17.6 Power Dissipation 240

17.7 MOSFan-Out 240

18

xiii

LINEAR ENHANCEMENT-ONLY

LOADED NMOS INVERTER

274

20.1

244

18.1

Operation of Resistor Loaded NMOS

Inverter 244

18.2 Graphical Determination of VTC for Resistor

Loaded NMOS Inverter 245

18.3 Calculation of VTC Critical Points for

Resistor Loaded NMOS Inverter 247

18.4 Power Dissipation of Resistor Loaded NMOS

Inverter 250

18.5 Resistor Loaded NMOS Inverter Dynamic

Response 252

18.6 Resistor Loaded NMOS SPICE

Simulation 258

19

SATURATED ENHANCEMENTONLY LOADED NMOS

261

INVERTER

19.1

Operation of Saturated Enhancement-Only

Loaded NMOS Inverter 261

Operation of Linear Enhancemnet-Only

Loaded NMOS Inverter 274

20.2 Graphical Determination of Linear

Enhancement-Only Loaded NMOS Inverter

VTC 276

20.3 Calculation of VTC Critical Points for Linear

Enhancement-Only Loaded NMOS

Inverter 277

20.4 Body Bias Consideration for Linear

Enhancement-Only Loaded NMOS

Inverter 281

20.5 Power Dissipation of Linear EnhancementOnly Loaded NMOS 284

20.6 Linear Enhancement-Only Loaded NMOS

SPICE Simulation 285

21

21.1

ENHANCEMENT-DEPLETION

LOADED NMOS INVERTER

288

Operation of Enhancement-Depletion

Loaded NMOS Inverter 288

21.2 Graphical Determination of EnhancementDepletion NMOS Inverter VTC 289

21.3 Calculation of VTC Critical Points for

Depletion Loaded NMOS Inverter 290

21.4 Body Bias Considerations for EnhancementDepletion Loaded NMOS Inverter 294

21.5 Enhancement-Depletion Loaded NMOS

Power Dissipation 297

21.6 Enhancement-Depletion Loaded NMOS

SPICE Simulation 298

XIV

Table of Contents

22

NMOS GATES

22.1

22.2

22.3

22.4

22.5

22.6

22.7

NMOS

NMOS

NMOS

NMOS

OAls)

NMOS

NMOS

NMOS

23

CMOS INVERTER

23.1

Operation of Complementary MOS (CMOS)

Inverter 336

Power Dissipation of CMOS 338

Graphical Determination of CMOS Inverter

VTC 339

Calculation of VTC Critical Points for CMOS

Inverter 340

The Symmetric CMOS Inverter 343

The Minimum Size CMOS Inverter 345

CMOS Inverter Capacitances 346

CMOS Inverter Dynamic Response 349

CMOS Fan-Out 358

CMOS Inverter SPICE Simulation 361

Design of CMOS Inverters 364

CMOS Latch-Up 367

Electro-Static Discharge and Input Clamping

Sections 369

23.2

23.3

23.4

23.5

23.6

23.7

23.8

23.9

23.10

23.11

23.12

23.13

24

24.1

CMOS COMBINATIONAL

LOGIC GATES

24.6

CMOS Inverter Pull-Up and Pull-Down

Review 373

CMOS NANO Cate 374

CMOS NOR Gate 379

CMOS AND and OR Gates 384

CMOS Complex Logic Gates (AOis and

OAis) 384

CMOS XOR/XNOR Gates 399

25

CMOS TRI-STATE GATES

24.2

24.3

24.4

24.5

25.1

301

NOR Gate 303

NANO Gate 305

OR and AND Gates 308

Complex Logic Gates (AOis and

308

XNOR/XOR Logic Gates 313

Schmitt Triggers 316

Transmission Gates 323

25.6

25.7

25.8

25.9

25.10

336

373

26

CMOS SCHMITT TRIGGER

GATES

26.1

26.2

26.3

26.7

Hysteresis 437

CMOS Schmitt Inverter 439

Operation and Voltage Transfer

Characteristic of the CMOS Schmitt

Inverter 441

Design of CMOS Schmitt Inverter 444

CMOS Schmitt Inverter with Buffered

Output 446

CMOS Schmitt Inverter with Buffered

Output and Feedback 447

CMOS Schmitt NANO Gates 451

27

CMOS DRIVERS

27.1

Cascaded CMOS Inverters Driving a Load

Capacitance 454

CMOS Multi-Stage Inverter Drivers 457

CMOS Tri-State Pin Drivers (Pad

Drivers) 461

Pad Driver with Break-Before-Make

Embodiment 463

26.4

26.5

26.6

27.2

27.3

27.4

411

CMOS Logic Gates with High Impedance

Z-States 411

25.2 CMOS Logic Gates with Contention

X-States 414

25.3 CMOS Tri-State (Clocked) Inverters 417

25.4 Application of Tri-State Inverters 419

25.5 Integrated Circuit BUSes Utilizing Tri-State

Inverters 422

Ordering of Stack Transistors in Tri-State

Inverters 422

Tri-State Logic of Multi-Input Logic

Functions 422

CMOS Bi-Directional Transmission Gate

(Switch) 426

Application of CMOS Bi-Directional

Transmission Gates 431

Disadvantages of CMOS Bi-Directional

Transmission Gates (Non-Fnult

Gmdnbility) 432

28

DYNAMIC CMOS

28.1

28.2

Pseudo-NMOS Logic 467

CMOS Precharging and Discharging of a

Load Capacitance 467

Dynamic CMOS Logic 469

CMOS Domino Logic 4 71

283.

28.4

29

29.1

COMPARISON AND

INTERFACING OF

LOGIC FAMILIES

Comparison of Silicon IC Logic

Families 477

437

453

467

477

Table of Contents

33

29.3

Comparison with Gallium Arsenide Digital

Logic Families 478

Interfacing Logic Families 478

30

BiCMOS

33.1

29.2

486

30.1 Reason for BiCMOS 486

30.2 BiCMOS Devices 486

30.3 BiCMOS Inverters with Resistive

Shunts 488

30.4 BiCMOS Inverters with Active Shunts 488

30.5 BiCMOS Inverters with Parallel Output

CMOS Inverter 488

30.6 BiCMOS NAND Gates with Resistive

Shunts 490

30.7 BiCMOS NAND Gates with Active

Shunts 491

30.8 BiCMOS Drivers 492

30.9 Full Swing Methods 494

31

LATCHES AND FLIP-FLOPS

31.1

Basic Definitions for Sequential Logic

Gates 498

Cross Coupled Inverters 501

Reset-Set (RS) Latch 504

Gated RS Latches 511

Gated RS Latches with Asynchronous Clear

and Preset 513

Edge-Triggered Master-Slave RS FlipFlops 515

JK Latch 526

Edge-Triggered Master-Slave JK Flip-Flops

0KFF) 528

Basic Data (D) Latch 534

Gated Data (D) Latch 536

Tri-State Embodied Gated Data (D)

Latches 540

Edge-Triggered Master-Slave D

Flip-Flops 543

31.2

31.3

31.4

31.5

31.6

31.7

31.8

31.9

31.10

31.11

31.12

32

32.1

32.2

32.3

32.4

32.5

32.6

32.7

498

SEMICONDUCTOR READ-ONLY

MEMORIES

556

Diode Read-Only Memories 557

BJT Read-Only Memories 563

Bipolar ROM Line Amplifier 572

NMOS NOR Read-Only Memories 572

NMOS NAND Read-Only Memories 580

CMOS Precharging and Discharging of a

Load Capacitance 583

CMOS Read-Only Memories 585

33.2

33.3

34

34.1

34.2

34.3

34.4

34.5

34.6

34.7

34.8

34.9

35

SEMICONDUCTOR STATIC

RANDOM-ACCESS

MEMORIES

Static RAM Cell with Transmission

Gates 603

MOSFET Static RAM Cell Technologies

BJT Static RAM Cell Technologies 608

GALLIUM ARSENIDE METAL

SEMICONDUCTOR FIELD

EFFECT TRANSISTORS

XV

603

607

613

N-Channel MESFETs (NMESFETs) 613

Enhancement-Depletion NMESFETs 615

Enhancement-Only NMESFETs 616

NMESFET Modes of Operation 616

NMESFET Transconductance

Parameter 618

NMESFET Threshold Voltage 618

NMESFET Capacitance 619

NMESFET Choice 619

SPICE NMESFET Model 620

DIRECT COUPLED NMESFET

LOGIC (DCFL) INVERTER

622

35.1

Direct-Coupled Enhancement-Only

NMESFET Inverters 622

35.2 Operation of Direct Coupled NMESFET

Inverter 622

35.3 Graphical Determination of Direct Coupled

Inverter VTC 624

35.4 Calculation of VTC Critical Points for DCFL

Inverter 624

35.5 Optimum f3 0 /f3L (W0 /W 1J Ratio for DCFL

Inverter 627

35.6 Power Dissipation of DCFL Inverter 628

35.7 DCFL Fan-Out 628

35.8 DCFL Inverter SPICE Simulation 629

36

36.1

SCHOTTKY DIODE NMESFET

LOGIC (SDFL) INVERTER

633

Schottky Diode Enhancement-Depletion

Inverters 633

36.2 Operation of SDFL Inverter 633

36.3 Calculation of VTC Critical Voltages for the

SDFL Inverter 635

36.4 Optimum f3t)f3L = Wn/WL Ratio for SDFL

Inverter 636

XVI

Table of Contents

36.5 Power Dissipation of SDFL Inverter 637

36.6 SDFL Fan-Out 638

36.7 SDFL Inverter SPICE Simulation 639

37

37.1

37.2

37.3

37.4

37.5

37.6

38

BUFFERED NMESFET LOGIC

(BFL) INVERTER

39.4

39.5

39.6

39.7

39.8

642

Buffered Enhancement-Depletion NMESFET

Inverters 642

Operation of BFL Inverter 642

Calculation of vrc Critical Voltages for the

BFL Inverter 643

Power Dissipation of BFL Inverter 645

BFL Fan-Out 646

BFL Inverter SPICE Simulation 646

OTHER GALLIUM ARSENIDE

LOGIC FAMILY INVERTERS

649

38.1

Capacitor Coupled NMESFET Logic (CCFL)

Inverter 649

38.2 Capacitor-Diode NMESFET Logic (CDFL)

Inverter 649

38.3 Source Coupled NMESFET Logic (SCFL)

Inverter 650

38.4 Low Pinch-Off Voltage NMESFET Logic

(LPFL) Inverter 651

38.5 Gallium Arsenide Transmission Gates 652

38.6 Power Dissipation 653

39

GALLIUM ARSENIDE

NMESFET GATES

39.1 DCFL NOR Gate 655

39.2 DCFL NANO Gate 656

39.3 DCFL OR Gate 657

655

39.9

39.10

39.11

39.12

SDFL NOR Gate 657

SDFL NANO Gate 658

BFL NOR Gate 659

BFL NANO Gate 659

Gallium Arsenide NMESFET Complex ANDOR-Invert (AOI) and OR-AND-Invert (OAI)

Gates 659

DCFL XOR Gate 660

Other OR/NOR Gates 661

Gallium Arsenide Transmission Gate

Logic 662

Gallium Arsenide Static RAM Memory

Elements 663

APPENDIX A

A.1

A.2

A.3

A.4

Development of the Stored Charge

Equation 666

Shockley's Expression 667

Diode Turn-On Transient 668

Diode Turn-Off Transient 669

APPENDIX B

B.1

B.2

B.3

DIODE SWITCHING

TIMES

666

BJT SWITCHING

TIMES

670

Development of the Stored Charge

Equation 670

BJT Turn-On Transient 670

BJT Turn-Off Transient 671

SUPPLEMENTARY READING

672

SELECTED ANSWERS

674

INDEX

679

PROPE TIES A D

DEFINITIONS OF

DIGITAL ICS

This chapter introduces the general properties and

definitions of digital circuits. These properties and

definitions are common to all digital integrated circuit families and are used throughout this text.

Digital electronic circuits are represented by five

basic logic operations. These are as follows:

•

We begin by describing the basic building blocks

of digital integrated circuits, the inverter and the

non -inverter.

1.1 INVERTING AND

NON-INVERTING GATES

NOT

• AND

• OR

Inverter

• NAND

Figure 1.1 displays circuit symbols that are used to

represent gates that perform logic inversion. That is,

if the input voltage is low, the output voltage will be

high and vice versa. This device is usually referred to

as an inverter or NOT gate, since it performs the logical NOT operation.

The small circle in Figure l.la and b is referred

to as an inverting bubble or inverting circle. The small

circle denotes logical inversion and is used extensively in digital logic circuits. It makes no difference whether the inverting circle is at the input or

output.

• NOR

When one of these operations is carried out by an

electronic circuit, the citcuit that performs this logic

function is referred to as a gate. The logic gates that

perform one or more of the basic operations are referred to as combinational gates. In these cases, the

outputs depend only upon the present value of the

inputs. We will describe many electronic circuits that

are used to carry out combinational logic operations

throughout the text. Circuits that perform sequential

logic operations are also presented in later chapters.

Sequential gates have output(s) that depend upon

past values of input(s), as well as present values. Implementation of these digital logic functions is also

accomplished feasibly using quite a few different digital electronic circuits.

The voltages (or currents) in digital logic circuits

have two possible states indicating that the variables

are binary. Considering voltage as a variable, the two

possible states correspond to a low voltage or a high

voltage, where we usually define the low voltage to

correspond to a binary O and the high voltage to a

binary 1. This is referred to as positive voltage logic

and is used for all IC logic families throughout this

text.

Non-Inverter (Buffer)

Another basic digital circuit device is the non-inverting gate which is sometimes referred to as a buffer.

Alternate circuit symbols for these devices are shown

in Figure 1.2. Buffers are used to regenerate voltage

levels, making degraded high levels higher and degraded low levels lower.

The inverting and non-inverting elements are

the fundamental building blocks for all digital logic

families. The basic inverter and its operation are

described for each logic family in succeeding chapters.

1

2

Chapter 1/Properties and Definitions of Digital !CS

1.2

IDEAL LOGIC ELEMENTS

Ideal Static and Power Characteristic

(a)

(b)

Figure 1.3a shows an ideal logic inverter. It operates

with a single power supply (Vcc in this case). A typical operating voltage of many logic families is 5 V.

The current Ice drawn from Vcc is ideally zero, giving

a power dissipation P cc of zero. In actual digital circuits the power dissipated is minimized for optimum

design. Figure 1.3b shows how voltage levels are ideally used to represent the input and output logical 0

and logical 1 states in digital circuits. The logical 1

output voltage is ideally at the power supply voltage

Vcc· The logical O output voltage is ideally at ground

(O V). Logic gates with output voltage transitions

from ground to the power supply voltage are said to

operate "rail-to-rail".

The transition between output logic states ideally occurs abruptly at an input of Vcc/2. Thus, logical input O is represented by the voltage range O :s;

V1;--.: < Vcc/2, since an input in this range will gen-

Alternate Inverter Logic Symbols

FIGURE 1.1

~ ~

(a)

FIGURE 1.Z

(b)

Alternate Non-inverting Logic Symbols

(a)

YaurCV)

logical 1

output

Yee I"""_

_ _.....,

YIN(V)

t,_

V

cc

logical O

input

i

logical 1

input

►

t

►

t

Yaur(V)

◄---

+

Yee,-!---,

logical 0

output

L___ _ __ . . _. . . . ._ _~ - - -

Ya/2

YIN(V)

Yee

(c)

(b)

FIGURE 1.3 Ideal Logic Inverter: (a) Operates from a single power supply, (b) Voltage transfer characteristic,

(c) Transient response

1.2 Ideal Logic Elements

Ideal Transient Characteristic

erate a logical 1 output state. Similarly, logical input

1 is represented by the voltage range Vcc/2 < V1;-..: :::::

Vee• The input voltage V1;-..: = Vcc/2 has an undefined

output and will cause unpredictable results, and is

therefore avoided. As will be seen in Chapter 23, the

CMOS logic family comes closest to meeting these

ideal static characteristics.

Figure 1.3c illustrates the transient response of the

ideal logic inverter. Upon transition of the input from

logical O to logical 1, the output instantaneously, and

without delay, switches from logical 1 to logical 0.

(As will be seen in section 1.7 the switching speed is

Your

-►

Iour

V' IN

1~ ►

. I'

i

IN

- - - - -- - load gates

I

driving gate

(b)

FIGURE 1.4

3

(a) Modelling of inverter input and output impedance, (b) Static driving of multiple (identical) inverters

4

Chapter 1/Propertics and Definitions of Digital !CS

V'om:

I

:;:: C'IN

I

load gate

driving gate

(c)

FIGURE 1.4 (continued) (c) Charging of load capacitance

not instantaneous and a delay between the output

and input transitions is present.)

Ideal Input and

Output Gate Impedances

The transient response, as well as the driving ability

(referred to as fan-out and discussed in section 1.6)

of logic gates is directly dependent upon the gate's

input and output impedance. Figure 1.4a shows a

model of the input and output impedance of a logic

inverter. The input can be modelled as a parallel resistance and capacitance. The output is modelled as

resistance in series with a complemented voltage

source. Examining Figure 1.4b, which shows an inverter driving multiple (identical) logic inverters, it is

observed that the driving gate must provide enough

output current to drive all the load gates. Quantitatively speaking, for N load gates, the output current

must be

where the primed terms of Figure 1.4 refer to the load

gates. For a very large input resistance, the input current is zero and the driving capabilities are maximized. Ideally, an infinite input resistance is desired,

giving infinite driving capability.

Referring to Figure 1.4c, which shows cascaded

inverters with infinite input resistance, it can be seen

that the input capacitance of load gates must be

charged through the output resistance of the driving

inverter. Thus, a smaller output resistance will provide a larger charging current for the load capacitance and a faster switching time, suggesting an ideal

zero output resistance. Of course, a smaller input capacitance will also speed up the switching time of

load gates. This is provided when fewer gates are

attached at the output.

1.3 INVERTER VOLTAGE

TRANSFER CHARACTERISTIC

The voltage transfer characteristic (VTC) for logic inverters have been standardized. Figure 1.5 displays

the linearized form of an idealized voltage transfer

characteristic. Indicated on the output (vertical) axis

are the voltages VoH and Vm, which correspond to

the output high and output low voltage levels, respectively. On the input (horizontal) axis, the input low

voltage is Vn_ and the input high voltage is V11+ Note

that as the input voltage is increased from 0, V1L is

the maximum input voltage that provides a high output voltage (logical 1 output). Furthermore, V1H has

the definition of being the minimum input voltage

that provides a low output voltage (logical O output).

The values Vc)H, V0 1,, V,L, and V1H are referred to as

the critical voltages of the voltage transfer characteristic.

It is customary to list output voltages VoL and

VoH on the input axis. This is because these outputs

for the present inverter will be inputs to the next

] .3 Inverter Voltage Transfer Characteristic

5

Vour(V)

T

VOH

t

5

4.3

4

3

2

1

0.2 1..-'.,----+tt--------,------+--+-t--+------Vm (V)

2

3

4 I

5

V DL=O.~ 1

p.9

V 0 H=4.3

0.7

FIGURE 1.5 Idealized Inverter Voltage Transfer

Characteristic

gate. Additionally, in order that the high and low

voltage levels always be distinguishable, we must always have

FIGURE 1.6 Voltage Transfer Characteristic for

Examples 1.1, 1.2, and 1.3

Solution The highest and lowest output voltages

are 4.3 V and 0.2 V, respectively. Thus

and

Vi,H = 4.3

VoL

<

V1L

Manufacturers usually specify worst case values for

the four voltages Vrn,, VoL, V1H, and Vu.

One final critical point labeled on the VTC of

Figure 1.5 is the midpoint voltage VM, sometimes referred to as the threshold voltage Vth (not to be confused with the MOSFET threshold voltage Vr)- The

midpoint voltage is defined as the point on the transfer characteristic where VoUT = V,N and ideally appears at the center of the transition r_egion. VM c~n

be found graphically by superirnposmg (the urnty

slope) Your = V,N and finding its intersection with

the VTC.

Example 1.1 Voltage Transfer Characteristic

Critical Points

What are the critical voltages V oH, VoL, Yiu V,H, and

VM for the voltage transfer characteristic of Figure

1.6?

V

and

VOL= 0.2 V

The input voltage at which the output begins to drop

is 0.7 V. The output reaches its lowest value at an

input of 0.9 V. Hence

Vrt = 0.7

V

and

Vu 1 = 0.9 V

The point on the VTC at which the input and output

are equal is calculated to be 0.87 V. The midpoint

voltage is therefore

VM = 0.9 V

which is far from being ideal. (Note the output low

and high voltages are labeled on the input axis.)

6

Chapter 1/Properties and Definitions of Digital !CS

1.4 LOGIC SWING AND

TRANSITION WIDTH

digital circuits is referred to as voltage level degradation and is termed noise.

Two important parameters that are obtained from

voltage differences of VTC critical voltages on a mutual axis are logic swing and transition width.

Logic Swing

Logic swing is defined as the magnitude of voltage

difference between the output high and low voltage

levels. Hence, the logic swing is equal to

Transition Width

The transition width is the amount of voltage change

that is required of the input voltage to cause a change

in the output voltage from the high to the low level

(or vice-versa). Hence, from the VTC the transition

width is equal to

Example 1.2 Logic Swing and Transition

Width

Determine the logic swing and transition width for

the VTC of Figure 1.6.

Solution Substituting the critical points determined in Example 1.1 directly into the definitions for

the logic swing and transition width yields

VLs

= (4.3) - (0.2) = 4.1

Vyw

=

V

Noise Margins

Since variations in the high and low logic levels occur, terminology is used to describe these fluctuations. From the idealized inverter VTC of Figure 1.5

with the defined voltages VoH, V0u Vn-1, and VrL, the

following definitions are made:

VNMH

=

Vm1 -

VNML

=

V1L -

V111

and

Var_

where NM stands for noise margin, VNMH is the high

noise margin (for the logic 1 level), and VNML is the

low noise margin (for the logic 0 level). The voltage

noise margins represent a safety margin for the high

and low voltage levels. Extraneous noise voltages

must have magnitudes less than the voltage noise

margins. The exact magnitudes of the high and low

voltage level is not important. However, the high or

low magnitude of voltage must remain in the range

of voltages that provide positive noise margins.

Noise Sensitivities

The effects of input variations are quantified in terms

of the noise sensitivities. The high and low noise sensitivities are defined as the difference between the

input and midpoint voltage for V 1N at V 0H and V0u

respectively. Expressions for each are

VNsH

=

Vo11 -

VM

and

and

1.5

(0.9) - (0.7) = 0.2 V

NOISE IN DIGITAL CIRCUITS

Noise Immunities

The quantity noise immunity is the ability of a gate to

reject noise. The high and low noise immunities are

quantitatively defined as the quotient of the noise

sensitivities and the logic swing as follows:

Noise

Variations in the steady-state voltage levels of digital

circuits (i.e. the logical 1 and the logical 0 states) are

undesirable and cause logic errors if the fluctuation

from the desired or specified voltage levels is too

great. This variation of steady state voltage levels in

VNill

-

VNS/i

V

LS

and

1.6 Fan-In and Fan-Out

The maximum fan-out possible during the driving

gate's logical O output state is

Example 1.3 Noise Margins, Noise

Sensitivities and Noise Immunities

By direct substitution the noise margins

are

V NM// = (4.3) - (0.9) = 3.4 V

and

VN,vlL

= (0.7) - (0.2) = 0.5 V

Using the results of Examples 1.1 and 1.2, the noise

sensitivities are by direct substitution

(4.3) - (0.9) = 3.4

VNSI/

=

VNS/

= (0.9) -

V

and

(0.2) = 0.7 V

The noise immunities by direct substitution are then

(3.4)

VNIH

_ lourUow)

N

Determine the noise margins, noise sensitivities, and

noise immunities for the VTC displayed in Figure 1.6.

Solution

7

/mu -

['

IN

(/

OW

)

The maximum fan-out of a digital gate is limited by

both of the previous expressions and is determined

from the lesser of the two.

Further, the fan-out (and fan-in) is an integer

because fractions of gates have no meaning as indicated in the following example. Fan-in is of lesser

concern and is determined in a similar manner.

Example 1.4

Maximum Fan-Out

The inverter of Figure 1.7 has the terminal currents

I,N(low) = 2.43 mA (out), 11N(high) = 98.9 µA (in),

IourOow) = 54.3 mA (in), and Iocr(high) = 71.4 mA

(out). What is the maximum fan-out?

Solution The maximum fan-out for the driving

gate with logical 1 output state is

= -(-) = 0.83

(71.4111)

4.1

N1i;:,;1i

= (98 _9 µ,) = 721.9

and

For the driving gate logical O output state, we have

(0.7)

VNIL

1.6

= -() =

4.1

FAN-IN AND FAN-OUT

A general logic gate has multiple inputs and multiple

outputs. By multiple outputs we mean the output of

a given gate is connected to (driving) the inputs of

several load gates. The term fan-in is used to describe

the number of inputs of a gate. Similarly, the term

fan-out is used to describe the number of outputs of

a gate. The maximum fan-out of a digital logic circuit

is restricted by its input and output currents as discussed in section 1.2. Not mentioned in section 1.2

is that the input and output currents of a gate are in

general different for the logical Oand logical 1 states.

Also, the input and output currents can be either into

or out of the gate. The maximum fan-out possible

during the driving gate's logical 1 output state is

N

_ lm 17 (high)

1; N(high)

1,igi, -

(54.3111)

N101,, = (

) = 22.3

0.17

2.4 3111

The maximum fan-out is clearly limited by the output low state of the driving gate. The least greatest

integer of N 10w is 22, and this is the maximum fanout.

As will be seen with logic circuits utilizing MOSFETs, the input current of such a logic gate is limited

to the MOSFET's infinitesimal gate current. This

suggests that logic circuits using MOSFET technol-

Irn(low) = 2.43 mA (out)

IIN(high) = 98.9 µA (in)

FIGURE 1.7

Logic States

I0 ur(low) = 54.3 mA (in)

lour(high) = 71.4 mA (out)

Inverter with Terminal Currents for both

8

Chapter 1/Properties and Definitions of Digital JCS

ogy have an infinite fan-out. However, this is not the

case. As will be seen in Chapter 16, the fan-out of

MOSFET digital circuits is limited by the input

capacitance of the gate which is the gate oxide

capacitance.

As just mentioned, the transient characteristics of

digital circuits employing MOSFETs are limited by

the gate oxide capacitance. This will be further discussed in later chapters.

Switching Speed Definitions

1.7

Figure 1.8 shows an input pulse and the output response of a logic inverting circuit. On the output response, which does not necessarily reach V cc (i.e.

usually YoH < Yee), the 10% YoH and 90% YoH

points are marked on both the rising and falling

edges of the output voltage. The characteristic

switching speed times are then defined in general in

terms of these output values as follows:

TRANSIENT CHARACTERISTICS

Digital logic circuits have finite switching speeds.

That is, switching a voltage from high to low (or viceversa) requires a finite amount of time. Additionally,

when the input voltage changes from one level to

another, the output voltage response is delayed in

time. This is referred to as propagation delay. These

limitations are present for all circuits and in particular

digital logic circuits. For digital circuits employing

BJTs, these time limitations are caused by the time

required to store and remove charge from the base

region. Section 4.5 discusses methods for decreasing

the storage and removal times required by the base.

0

=

=

=

=

t., 11 =

toff =

td

tr

t,

tr

delay time

rise time

storage time

fall time

turn on time = td

turn off time = ts

~------------------+--------------- t(ns)

(a)

Your<V)

--------,----

-------------~-------------------,..-

90% -- -:- -- ---- --------- -- ------ ---- ---- ---- ----- -- ---'. --- --- ---- ---'

10%

- ·--r -- -- - --- . -- . ··--- ------ ----

------------

-

-----

'

(b)

FIGURE 1.8

+ tr

+ tr

Switching Speed Definitions: (a) Input pulse, (b) Output pulse

1. 7 Tr,msien t Characteristics

9

The overall propagation delav time t"(avg) is defined as the average of these two, given by

The rise time and fall time are the times associates

with charging and discharging load capacitances.

The delay time and storage time are associated with

stored charge of PN junctions. The turn on time and

turn off time are sums of these quantities. See Figure

1.8b.

Propagation Delays

Example 1.5

Figure 1.9 shows an input waveform and output response of a logic circuit. The output delay is typical

of all digital logic gates and represents the response

of the output voltage to a change in the input voltage. The 50% V0 H points are labeled on the rising

and falling edges of both the input and output waveforms. The 50% points are used to define the time

required for the output to respond to the input.

These response times are called the propagation delay

times. The /ow-to-11igh propagation delay time tl'LH

refers to the low-to-high transition of the output and

the high-to-low propagation delay time tp 11 L is for the

output high-to-low transition. TI1e definitions of tp 11 L

and t,u, are as shown in Figure 1.9.

Transient Characteristics

For the input and output waveforms of Figure 1.10,

determine

(a) the switching times t, and t 1

(b) the propagation delay times tl'LJJ and tl'llL·

Solution (a) By direct examination of Figure 1.10

t, = 168

11S

tr= 168

11S

and

Note that the output falling edge is to the left of the

output rising edge.

L___----------------------~--~--- ►

(a)

VOUT(V)

(b)

FIGURE 1.9

Propagation Delay Definitions: (a) Input waveforms, (b) Output response

t(ns)

10

Chapter 1/Properties and Definitions of Digital JCS

VOH

f---- --------------------------------------------------

VOL

i-------"

90% ·

10% ·---- ------------------------------------~--+----+----+-----+-----+-----+------1-----+----------+---,► t(ns)

100

200

300

400

500

600

700

800

900

1000

1100

(a)

VOH - - - - - - - - - - -...

I

90% ---- -----------------------

VOL'

~--+----+----+-----+-----+-----+--~-----------,1-----+----------+--~ ►

100

200

300

400

500

600

700

800

900

1000

t(ns)

1100

(b)

FIGURE 1.10

Input and Output Waveforms of Example 1.5

Solution (b) The propagation delay times are

tPI/L

= 100

115

Calculation of average power dissipation for actual

digital circuits entails the determination of the current supplied by the power source for both output

logic states and is determined as follows:

tl'LI/

=

115

Pcc(avg) = Icc(OH) + lec(OL) Vee

and

250

2

1.8

POWER DISSIPATION

In section 1.2, it is stated that an ideal gate has a

single power supply as shown in Figure 1.3a. The

power dissipation for such a gate is obtained by realizing it is equal to the power supplied. Furthermore, the power dissipated in this gate for the output

high (logical 1 output) and output low (logical Ooutput) states, P cc(OH) and P cc(OL), respectively, will

generally be different. Manufacturers therefore in

general specify the average power dissipation for a gate

with two possible output states as follows:

p

( )

Pcc(OH) + Pec(OL)

cc avg =

2

Some logic circuits have two power supplies, one

with a positive voltage and one with a negative voltage. Figure 1.11 shows such a gate. In this case, both

currents Ice and IEE are obtained for each of the output high and output low logic states. The average

PEE= IP.EVEE

FIGURE 1.11 Power Dissipation in a Logic Gate with

Two Power Supplies

Chapter 1 Problems

power supplied by this gate with two possible states

is then defined c1s

Pcdavg) + Pn (avg)

Icc(OH) + Icc(OL) V

cc

2

+ hi:(OH) + Ii:i:COL) V

2

E£

Pee = IccVcc

PEE

= IFEVEE

Note that the current IEE flowing into -VEE does yield

a positive power dissipation.

Example 1.6

Average Power Dissipation

Determine the average power dissipation for a gate

supplied by a 5 V power supply with I(OH) = 1 mA

and I(OL) = 3.18 mA.

Solution The average power dissipation by direct

substitution is

P(avg)

(1m) + (3.18111) ( )

=- - - - 5 = 10.5

2

m

W

However, as will be seen, faster propagation delay

times are achieved at the cost of increased power

dissipation. Conversely, lower power dissipation results in longer propagation delays. Thus, a practical

figure of merit used for digital logic gates is the product of the Jverage power dissipation P(avg) and the

average propagation delay time tr(avg). This is referred to as the power-delay product and is written as

follows:

PD

POWER-DELAY PRODUCT

= Prnss(avg)tp(avg)

This value is sometimes referred to as the speed-power

product. The smaller the power-delay product is for

a given gate, the more ideal the gate is. For the ideal

gJte, PD = 0. Note thJt since power has units of

watts and propagation delay has units of seconds,

the power-delay product has units of joules.

Example 1. 7

Power-Delay Product

The gate of example 1.6 has propagation de!Jy times

of tPHL = 1.4 ns and tPLH = 3.2 ns. Calculate the

power-delay product for this gate.

Solution The average propagation delay is

tp (avg) =

1.9

11

(1.411)

+ (3.2n)

2

=

2.3 ns

The power-delay product is therefore

PD = (10.5111)(2.311) = 24.2

Low power dissipation and short propagation delay

times are both desirable for digital logic circuits.

pf

CHAPTER 1 PROBLEMS

Ymrr(V)

1.1

1.2

1.3

1.4

1.5

The voltage transfer characteristic (VTC) for a logic

inverter is shown in Figure Pl.1. For this inverter,

determine the following:

(a) Vo11, You V1L, Vll 1, and VM

(b) the logic swing

(c) the transition width

(d) the noise margins, noise sensitivities, and noise

immunity levels

Repeat Problem 1.1 for the VTC of Figure Pl.2.

Repeat Problem 1.1 for the VTC of Figure P1.3.

Repeat Problem 1.1 for the VTC of the non-inverting

logic gate of Figure P1.4. (For a non-inverter, V1L is

the highest input that provides a low output and Vll 1

is the lowest input that provides a high output.)

Sketch the VTC for a logic inverter with V011 = 5 V,

Vm = 0.2 V, v,L = 1.4 V, and V11-l = 1.6 V. Also,

determine the logic swing, transition width, and the

noise margins.

3 - - -....

2

0.2

~ - - - - - + + - J - - - - - + - - - - - - + - - - - VIN

1

FIGURE Pl.I

2

3

(V)

12

Chapter 1/Properties and Definitions of Digital !CS

V 011,(V)

Yaur(V)

A

5-1----

51

4.3" --- - ------ 41-

4

I

3

3t

I

2f

2

1LJ:

i

'

o.~ .

I\~--------

I

,'

'--------++'-t'---+----+----t------.------+-----VIN (V)

1

1.

2

3

4

i

3

4

1.9

FIGURE Pl.4

Yaur(V)

-1.5

munity levels for the VTCs described in Problems 1.5 through 1.9.

VIN (V)

-0.5

1.11

Find the maximum fan-out for a gate with I011 =

12 mA (out), IoL = 7 mA (in), ! 111 = 0, and In. =

124 µ,A (out).

1.12

Find the maximum fan-out for a gate with Ioi 1 =

4 mA (out), IoL = 6.2 mA (in), I1r1 = 240 µ,A (in),

and Ill.= 0.

1.13

Find the maximum fan-out for a gate with IoL =

57.5 mA (in), 11L = 1.09 mA, and lu 1 = 0.

Find the maximum fan-out for a gate with IoL =

79.3 mA (in), I1L = 1 mA, and 1111 = 0.

-0.8

-1.0

-1.5

-1.6

1.14

1.15

FIGURE P1.3

1.6

Repeat Problems 1.5 for Vm1 = 3.6 V, VoL = 0.2 V,

ViL = 0.5 V, and V111 = 1.2 V.

1.7

Repeat Problem 1.5 for Vrn-i = 4.3 V, Vm = 0.5 V,

V1L = 0.9 V, and V1H = 1.1 V.

Repeat Problem 1.5 for VoH = -0.77 V, Vm =

-1.58 V, V 1L = -1.225 V, and V111 = -1.125 V.

1.10

I

121

~-1

-1.2

1.9

:

:'

0.2·'

5

1.4

FIGURE Pl.2

1.8

:

Repeat Problem 1.5 for V011 = 5 V, Vm = 0 V, V1L

= -2 V, and V1r1 = 3 V.

1.16

1.17

A non-inverter has a voltage pulse applied at the

input and the corresponding output voltage response as shown in Figure Pl.17. Determine the delay, rise, storage, and fall times. Also, find the propagation delays.

1.18

Repeat Problem 1.17 for Figure Pl.18.

1.19

Sketch the input and output waveshapes for a TTL

inverter with t, = 10 ns and t, = 30 ns.

1.20

Repeat Problem 1.19 for an STIL inverter with t, =

5 ns and t, = 7 ns.

1.21

Repeat Problem 1. 19 for an ASITL inverter with t, =

2 ns and t1 = 3 ns.

(a) Find the high and low noise sensitivities for the

VTCs described in Problems 1.5 through 1.9. Assume the midpoint voltage is in the center of the

transition region for each VTC.

(b) Using the results of part (a), find the noise im-

Find the maximum fan-out for a gate with IoL =

199 mA (in), I1L = 1.32 mA, and 1111 = 0.

A rookie electrical engineer designs a digital gate

with Irn 1 = 3.9 mA (out), Im= 5.4 mA (in), I111 =

0 mA, and 11L = 56 µ,A (in). Is there anything inherently wrong with this design? If so, what?

Chapter 1 Problems

13

VIN(V)

v•• t

I

I

~:- ~ - - - - - - - - - - - - - ~ - - - - - - - - - - - - - t ( µ s )

'

~ - 20~

Yom(Y)

'

VIT - - - - - - -90%

10%

~~-~~-----t(µs)

f'---15 __.!:

FIGURE P1.17

VIN(V)

t

v•• I

~•- ~ - - - - - - - - - - - - - - ~ - - - - - - - - - - t ( µ s )

90%

~------;--------------------~-------+---•t(µs)

~·-40---~

I

:---20~

I

I

•

FIGURE Pl.18

1.22

A gate is powered by a single 5 V supply. The current

delivered by the power supply is 4.2 mA for the output high state and 1.7 mA for the output low state.

What is the average power supplied?

=

0.52 mA and

1.23

Repeat Problem 1.22 for Icc(OH)

Icc(OL) = 42 µA

1.24

Find the average power supplied to the inverter of

Figure Pl.24.

14

Chapter 1/Properties and Definitions of Digital !CS

Vee= 5V

1.25

What is the power-delay product for P(avg) = 2 mW

and

(a) tp(avg) = 100 ns?

(b) tp(avg) = 250 ns?

(c) tp(avg) = 500 ns?

1.26

Repeat Problem 1.25 for P(avg)

0

FIGURE P1.24

= 10.2 mW.

In this chapter, two-terminal semiconductor PN

junction and MN Schottky diodes are introduced.

These important elements are used in digital logic

circuits to perform various logic operations, as well

as variable capacitors, DC voltage level shifting, and

clamping diodes at logic circuit inputs.

The chapter begins by describing semiconductor

diode circuit models. Diode-resistor logic is also presented. This is the simplest of all logic families but

also possesses many intolerable disadvantages. In

the latter sections, the function of clamping diodes

and level-shifting diodes are described.

mize the BJT performance and it is not feasible to use

additional layers for diodes.

Schottky-Barrier (MN Junction) Diodes

For MN diodes, the N- semiconductor region and a

particular metal form the Schottky diode. Schottky

diodes are rectifying junctions entirely analogous to

PN diodes, except that the P-region is replaced with

a particular metal that provides a barrier to electron

flow in one direction. Not all metals provide Schottky

diodes with N doped silicon.

When N-type silicon is the semiconductor material, platinum silicide (Pt 5 Si 2) is the metal most often used to form the MN Schottky diode. This is accomplished by depositing Pt on Si and heating

(annealing) at 600°C to form Pt 5 Si 2 .

PN JUNCTION AND

MN SCHOTTKY DIODES

2.1

PN junction semiconductor diodes and Schottky barrier MN diodes are important elements in digital integrated circuits. The circuit symbols for these two

terminal devices are shown in Figure 2.1 along with

definitions of forward current and voltage. Diodes

are used in bipolar IC families as actual circuit components, as well as clamping diodes at logic circuit

inputs. When used as clamping diodes, their purpose

is to reduce transient voltages that result from

switching transitions. However, these clamping diodes do not affect normal circuit operation. Figure

2.2 displays device cross-sections for digital IC PN

and MN diodes. Typical cross-sections arc indicated

for the case of a double diffused implanted epitaxial

bipolar IC. The particular diode geometries of Figure

2.2 are chosen because of fabrication compatibility

with the double diffused epitaxial BJT discussed in

the following chapter.

DIODE MODELLING

2.2

Shockley's Current-Voltage Expression

The theoretical current-voltage relation that represents the DC current dependence on voltage for PN

junction and MN Schottky diodes is

10 = 15 (ev,,i<t,r - 1)

where

I5 = reverse saturation current [A]

cf>T = thermal voltage [V] calculated by

kT

q

q>T = -

= Boltzmann's constant= 1.34

T = Temperature [°K]

k

x 10- 23 J/°K

q = elementary electronic charge

= 1.60 X 10- 19 C

PN Junction Diodes

This expression, often referred to as Shockley's

equation, is temperature dependent, as seen by the

Usually, the PN junction diodes utilize two out of the

three regions of a bipolar junction transistor, instead

of a separate device structure. This is because the

various P and N layers have been selected to opti-

temperature dependence of the thermal voltage q>y.

The reverse saturation current is the minute leakage

current that flows through a reverse biased diode and

15

16

Chapter 2/Diodcs

'it

.

(a)

Shockley's Equation

at Room Temperature

(b)

At room temperature (T = 27°C or 3OO°K) ¢ 1

is given by

FIGURE 2.1 Diode Symbols: (a) PN junction diode,

(b) MN Schottky barrier diode

PN junction

;

ohmic contact

P+

(

--

'

N- epitxiai layer

-(

-

)

N+ buried layer

I

_ \ P+

/

)

Tips, Tricks, and Gimmicks

__

)

Note that the 1/¢T term in the exponential has

a magnitude of approximately ·40 for room

temperature leading to the more compact expression

I

-1

(

P substrate

20

_.

K = (1.34 X 10- )(300) _

¢,(3000 )

(1.6Ox10-l'J)

-25.9111V

In(T = 3OO°K) = I 5 (e 40 vn - 1)

which is valid only at room temperature.

\

(a)

Solution By direction substitution

Schottky MN contact

Si02

/ohmi'.:,contact

~\-_-\-~+-}_->-'.--,~.~~~,{

\

L

,

~

P substrate

In(VD

Io(Vn

I

,

(

~

In(Vo

(b)

In(Vn

ln(Vn

In(Vn

In(Vo

=

=

=

=

=

=

=

(1O-14)[e40(0

0.2)

oo- 14) [e4o(o 21

0.5)

oo-14)[e40(05) - 1)]

0.7)

(10-14)[e40(01) _ l) l

is typically a pA or less for PN junction diodes and a

µA or less for MN Schottky diodes.

The following examples indicate magnitudes for

positive and negative diode voltages.

Example 2.1 Relative Forward-Biased

PN Junction Diode Current Magnitudes

Use Shockley's expression to determine the diode

current for V0 = 0.1, 0.2, 0.5, 0.7, 0.8, 1, and 2.3 V.

Use Is = 10- 14 A and assume room temperature.

I) _

_

0.8)

(1O-H)[e40(0~) _ 1)]

1.0)

(1O-l4)[e4ll(IO) _ 1)]

2.3)

oo-14) [e40(23) _ 1)]

=

FIGURE 2.2 Diode Cross Sections: (a) PN junction

diode, (b) MN Schottky barrier diode

l)j = 536 JA

l) l = 29.8 pA

0.1)

=

=

=

=

4.85 µA

14.5 mA

790 111A

2.35 kA

9.02 X 10 25 A

As can be seen, the diode current's exponential dependence on VD is quite pronounced. For a diode

voltage of 0.5 V the diode current is a few microamps

and approaches zero rapidly for smaller voltages. For

currents in the milliamp range, the diode voltage is

0.7 V and the diode current reaches hundreds of 111i//iamps for another 0.1 V increase to 0.8 V. For a diode

voltage of 1 V, the current magnitude is at a normally

unobtainable hundreds of amps. Note that for VD =

2.3 V the diode current is an unprecedented 9.02 X

10 25 A and the IDVI) power dissipated in the diode

exceeds the entire power output of our sun. The diode would surely become damaged long before this

would happen.

2.2 Diode Modelling

Example 2.2 Relative Reverse-Biased

PN Junction Diode Current Magnitudes

17

Tips, Tricks, and Gimmicks

ex >> 1 or e-x << 1

Use Shockley's expression to determine the diode

current for VD = -1, -10, -100, and -200 m V. As

in Example 2.1 use 15 = 10- 14 A and assume room

temperature.

The two previous examples suggest the following approximations:

Solution By direct substitution

and

Io(Vo = -1 mV) = (10- 14)[e'l0(-llll)

IoWo

InWo

-

> 0.1) = fsev[)1<1>1

< -0.1) = -]5

1)]

= -392 aA

InWo = -10 mV) = (10-14)[e40(-10,11l - 1)]

= -3.30 fA

Io(VD

=

-100 mV)

=

(1o-14)[e40(-100111)

1)]

-9.82fA

][)(VD= -200 mV) = (1o-14)[e40(-200111) - 1)]

-10.0 fA

-10-14 A

As seen, at V0 s -0.2 V the reverse diode current

has a magnitude equal to 15, accurate to three decimal places. Hence, 15 is called the reverse saturation

current.

The following section utilizes the computational infonnation of the previous examples in suggesting a reasonable piecewise linear model for diodes.

Piecewise Linear Diode Model

Example 2.1 indicates that a forward diode voltage

of 0.5 V corresponds to a diode current of only a few

microamps. Furthermore, increasing the forward

voltage to 0.8 V increases the current to hundreds of

milliamps. For currents up to a few milliamps, which

is a practical order of magnitude for active IC device

currents, the diode voltage is approximately 0. 7 V.

This suggests that a practical diode model for hand

l>t- -

cutoff

- - - - - - - - - / - ~ ~ ~ ~ ~ ~ - - - VD (V)

Vo(ON)=0.7

(a)

FIGURE 2.3

(b)

Piecewise Linear Diode Model: (a) Diode current versus diode voltage, (b) Diode symbol

18

Chapter 2/Diodes

TABLE 2.1

Diode Modes of Operation

PN Junction Bias

Reverse

Forward

Cl){1

junction capacitance [F]

Mode of Operation

Cutoff

Conducting

¢n

= junction potential

m

= grading coefficient

(typically 0. 7 to 0.9 V)

TT

analysis is the piecewise linear model shown in Figure 2.3. This model has two linear regions:

I0 = 0 for V0 :s: V0 (0N)

and

Vn = Vi/ON) for I 0

2:

0

where a practical value for VD(ON) is the aforementioned 0.7 V. Thus, for diode voltages less than

V0(ON), the diode is cutoff and for diodes conducting forward current, a forward voltage of 0.7 V is

present. A similar model for MN Schottky diodes is

also used but with a s1T1aller turn on voltage

Vstm(ON) of 0.3 V for silicon.

From the above discussion, a diode can be seen

to have two modes of operation, cutoff and conducting, the operating mode of a diode depe'.,ding upon

the magnitude and polarity of the diode junction bias

VD. These modes and the corresponding junction biases are tabulated in Table 2.1. The diode breakdown

region of operation is avoided in digital circuits and

no 1nodeling for this mode is necessary.

2.3

DIODE CAP A CIT AN CE

A PN junction diode has a capacitance associated

with it due to charge in the depletion region and for

forward bias, charge stored in the semiconductor

bulk regions due to injected minority carriers. The

capacitance contributes to transient response limitations. Furthermore, this capacitance must be fully

charged to switch the diode into the conducting state

and discharged to switch the diode to the cutoff state.

Thus, the capacitance of a diode is voltage-dependent and can be represented by the expression

= zero-bias (i.e. VI) = O)

=

(m = ½ or 1/3 for digital IC diodes)

minority carrier transit time

It is further noted that the first term is due to stored

minority charge, whereas the second term is due to

depletion region charge. The magnitudes of these

pJrarneters can be calculated from the diode's physical attributes and fabrication processing paran,eters,

such as doping densities.

Varactor Diodes

The PN junction capacitance can be utilized in ICs

by applying a negative bias to a diode. Diodes used

for this purpose are referred to as varactor diodes and

have the modified diode circuit symbol of Figure 2.4.

For this device, the forward diode voltage VD is negative. As will be seen in Chapter 9, advanced STrL

logic families utilize varactors in a configuration that

improves the overall transient response of the logic

gate.

2.4

SPICE DIODE MODEL

This section introduces the SPICE diode model and the

physical significance of each cf the SPICE diode model

pa m111etcrs.

The large signal diode model used in SPICE is

shown in Figure 2.5.

SPICE Diode DC Characteristic

"n1e nonlinear current source lb has a value according to the empirically modified Shockley expression

Ib

- 1)

.-------t>l 1---FIGURE 2.4

where

= JS(evniN<t,,

Varactor Diode (Voltage Dependent

Capocitor for Vn < 0)

19

2.5 Diode-Resistor Logic

+

Q0 = TT X IS(ev1,1N,t,T

+ CJO

Rs

_

f" (1 - ~rM

1)

-

dV

For V0 > FC</> 0 , where FC is a model parameter