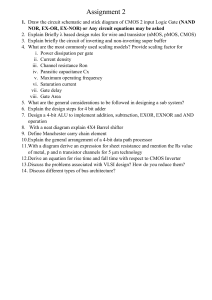

EE409 - VLSI Design Static CMOS Dr. Emily Leong (Leong Hung Yang) Email: leonghy@ucsiuniversity.edu.my Reference : Weste, Neil HE, and David Harris. CMOS VLSI design: a circuits and systems perspective. Pearson Education India,2015. CMOS nMOS commonly tied toGND pMOS commonly tied toVDD Gate Voltage • VDDrepresent gate input in the digital circuits, or simply the power = logic 1 • In 1970 to 1980 , VDD=5V, • However, recent small transistor can’t withstand high voltage, VDD has reduced to (3.3 V, 2.5 V, 1.8 V, 1.5 V, 1.2 V, 1.0 V and so on) • VSS = simply represent ground = logic 0 nMOS Transistor Operation Source Gate Drain Polysilicon SiO2 n+ n+ p • Body is commonly tied to gnd ( 0V) • When the Gate is at low voltage(VGS < VTP) – Source to Body and Drain to Body diodes are OFF – No current flow >>Transistor OFF • When the Gate is at high voltage = 1(VGS ≥ VTN): – Negative charge attract to body – Inverts a channel under gate to n-type – Electrons flow from Source toDrain – Current flow >> TransistorON bulk Si pMOS Transistor Operation Source Gate Drain Polysilicon Bubble – inverted /opposite behavior compared to nMOS SiO2 p+ p+ n • Body is commonly tied toVDD • When the gate is at a low voltage (VGS < VTP): – Positive charge attracted to body – Inverts a channel under gate top-type – Transistor ON, current flows • When the gate is at a high voltage (VGS ≥ VTP): – Source and drain junctions areOFF – Transistor OFF, no current flows bulk Si Transistor as switches • In Digital circuits, MOS transistors are electrically controlled switches • Voltage at gate controls path from source to drain d nMOS pMOS g =0 g =1 d d OFF g ON s s s d d d g OFF ON s s s g1 g2 Series Combination Series Combination ON OFF OFF OFF Parallel Combination Parallel Combination NMOS Inverter Resistive Load Inverter https://www.tutorialspoint.com/vlsi_design/vlsi_design_mos_inverter.htm NMOS LogicGate NMOS acts as pull-down network What function isthis? NMOS NOR Gate NMOS LogicGate NMOS Nand Gate NMOS Logic GateSummary • Series transistor – AND • Parallel transistor – OR • Need to implement resistor separately (Not good in design performance)WHY? NMOS Logic GateSummary • Series transistor – AND • Parallel transistor – OR • Needto implement resistor separately ( Not good in design performance)WHY? • Fabricate transistor in silicon area issmaller compared to resistive load • Transistor is active load givesbetter performance Exercise 1. Draw 2 inputs NAND gates using 3 NMOS transistors 2. Draw 2 inputs NOR gates using 3 NMOS transistors CMOS CMOS asinverter CMOS NAND GATE AND – nMOS series or parallel? CMOS NAND GATE EXERCISE • DRAW 3-INPUTS CMOS NAND GATE EXERCISE • DRAW 3-INPUTS CMOS NAND GATE CMOS NOR GATE • Draw 2 inputs CMOS NOR Gate CMOS NOR GATE • Draw 2 inputs CMOS NOR Gate Exercise Exercise Homework • Form a group 3 students ( for future assignment also) • Task 1 – Advantages of CMOS logic circuitdesigns over nMOS logic circuitdesigns. – Make an electrical performancecomparison between CMOS andNMOS – Why CMOS technology is preferred over NMOS technology? • Task 2 - Operation of MOSFET (Depletion , Accumulation and Inversion) Exercise • Consider Figure showing a combination of logic gates below. Figure 1 a. Determine the Boolean expression for Figure 1 b. Sketch Boolean expression above a. b. using NMOS transistorsonly CMOS transistors Tutorial Consider the logic functions below. i. F = 𝐴𝐵𝐶 + 𝐷 ii. F = AC+BC+AC+D a. Illustrate the schematic of the transistor level for the logic function F based on using NMOS technology. a. Illustrate the schematic of the transistor level for the logic function F based on using CMOS technology. Tutorial Consider the logic functions below. i. F =(𝐴+𝐵)𝐶 ii. F = 𝐴+(𝐵. 𝐶) a. Determine the Boolean expression for the logic function above. b. Illustrate the schematic of the transistor level for the logic function F based on using NMOS technology. c. Illustrate the schematic of the transistor level for the logic function F based on using CMOS technology.